High-speed dynamic comparator with metastable state suppression technology

A technology of dynamic comparator and metastable state, applied in multiple input and output pulse circuits, etc., can solve the problems affecting the accuracy of SARADC, comparator metastable state, wrong comparison results, etc., achieve simple structure, improve comparison speed, Effect of Power Consumption Reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with the accompanying drawings.

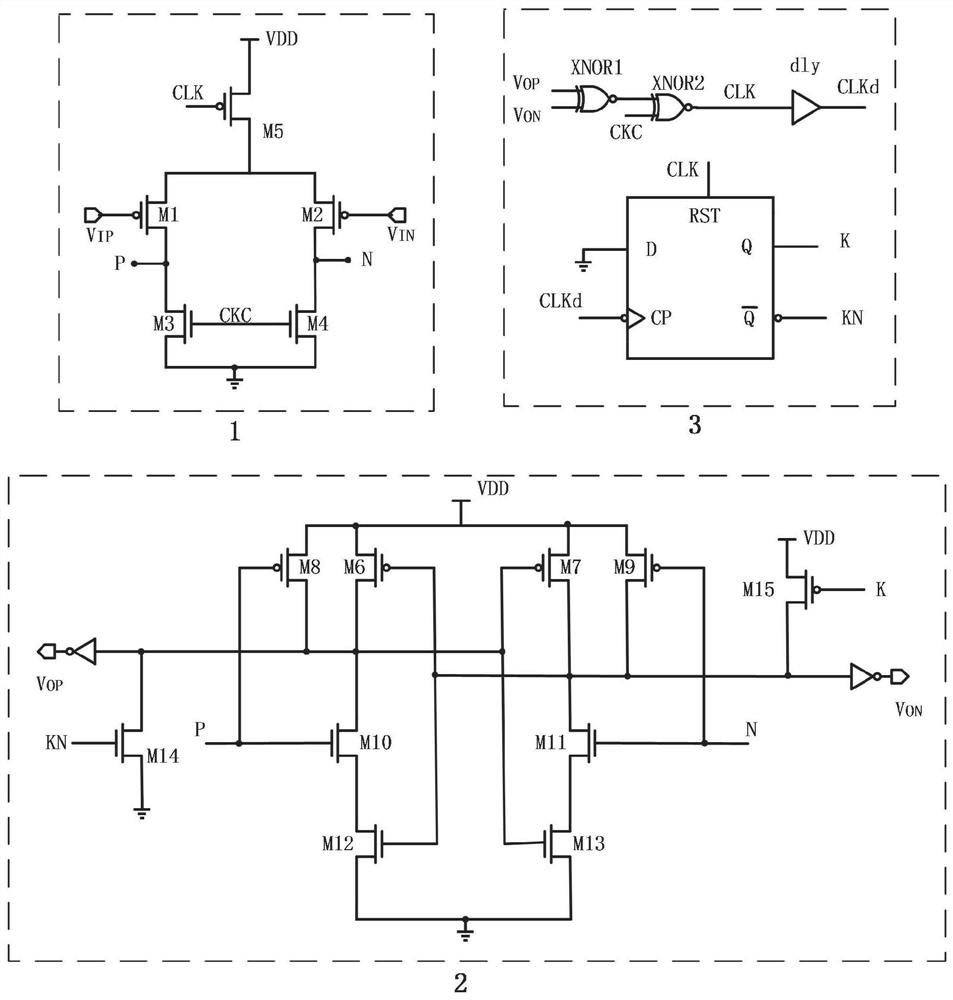

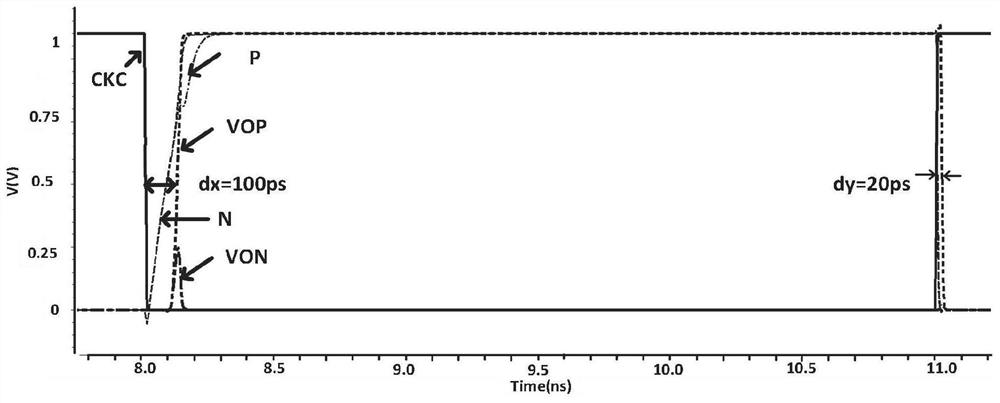

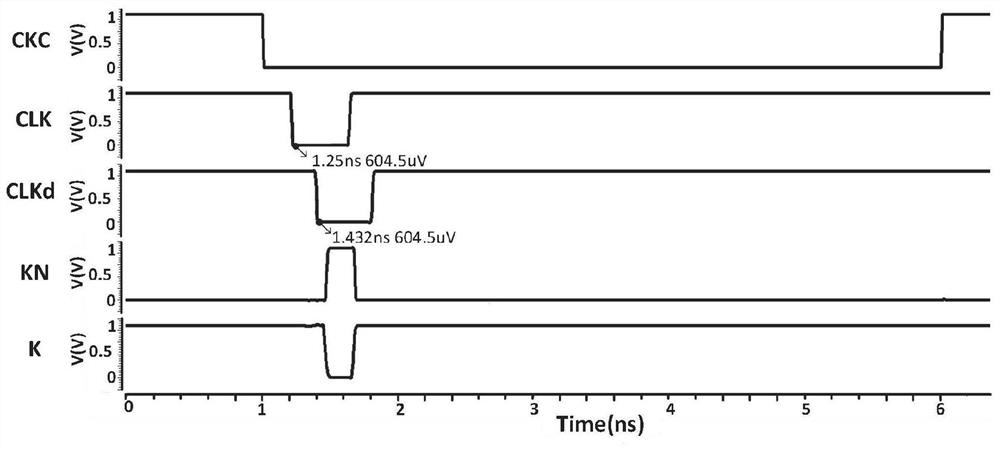

[0032] Such as figure 1 Shown, a kind of high-speed dynamic comparator with metastability suppression technology of the present invention comprises pre-amplifier 1, post-stage latch 2 and metastable state suppression circuit 3; Preamplifier 1 realizes to input differential signal namely The positive terminal input signal VIP and the negative terminal input signal VIN are amplified, and the output amplifier positive terminal output signal P and the amplifier negative terminal output signal N are connected to the two input terminals of the subsequent stage latch 2; the latter stage latch 2 realizes the input Fast comparison of the signals, the output signal VOP at the positive end of the latch and the output signal VON at the negative end of the latch are sent to the metastable suppression circuit 3; the output clock signal CLK of the metastable suppression circuit 3 is co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More