FPGA based IPv6 data packet high-speed processing device and operational method thereof

A high-speed processing and data packet technology, applied in data exchange networks, digital transmission systems, electrical components, etc., to solve problems such as processing speed discounts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0038] Embodiment 1: (device embodiment)

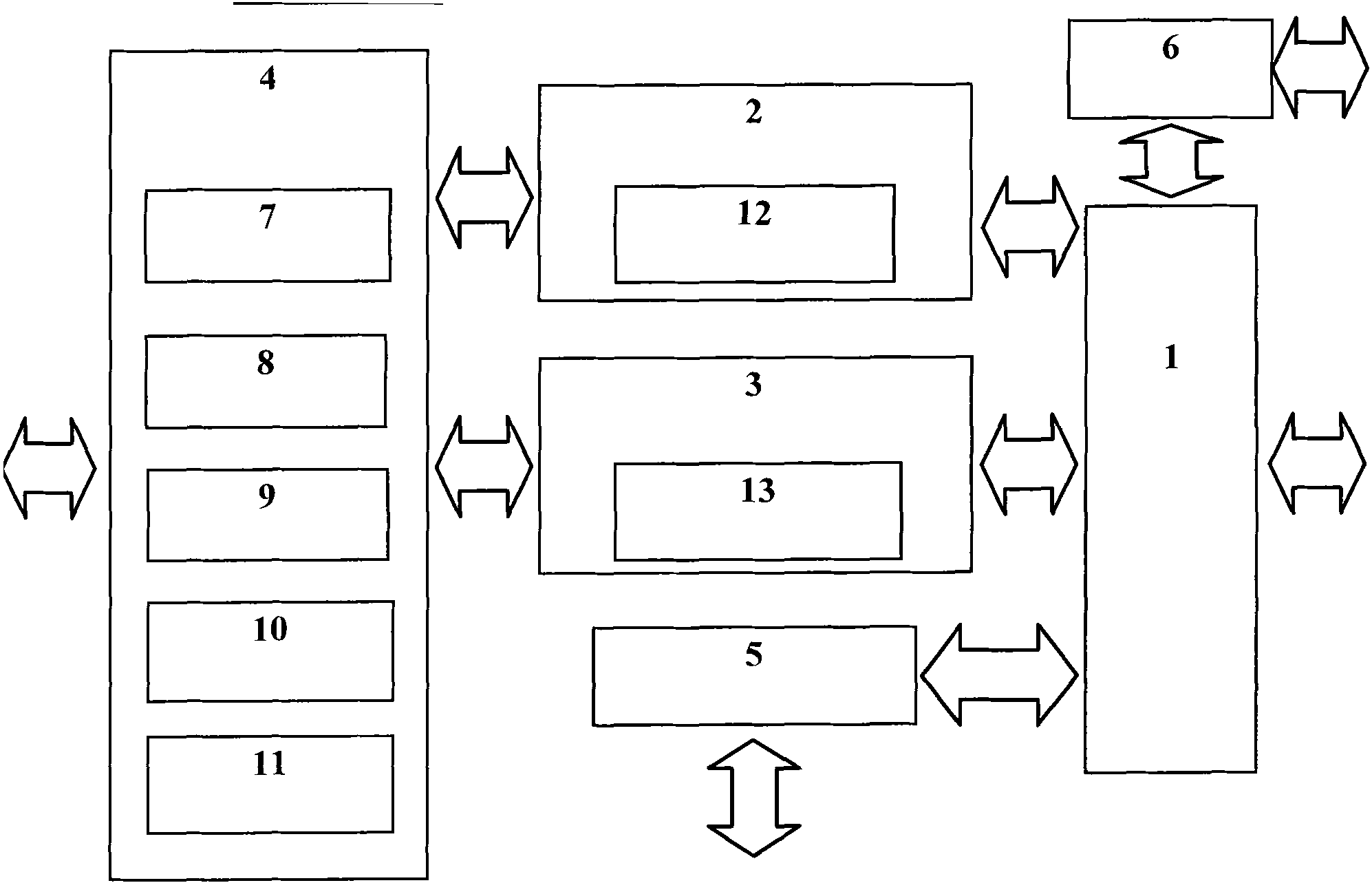

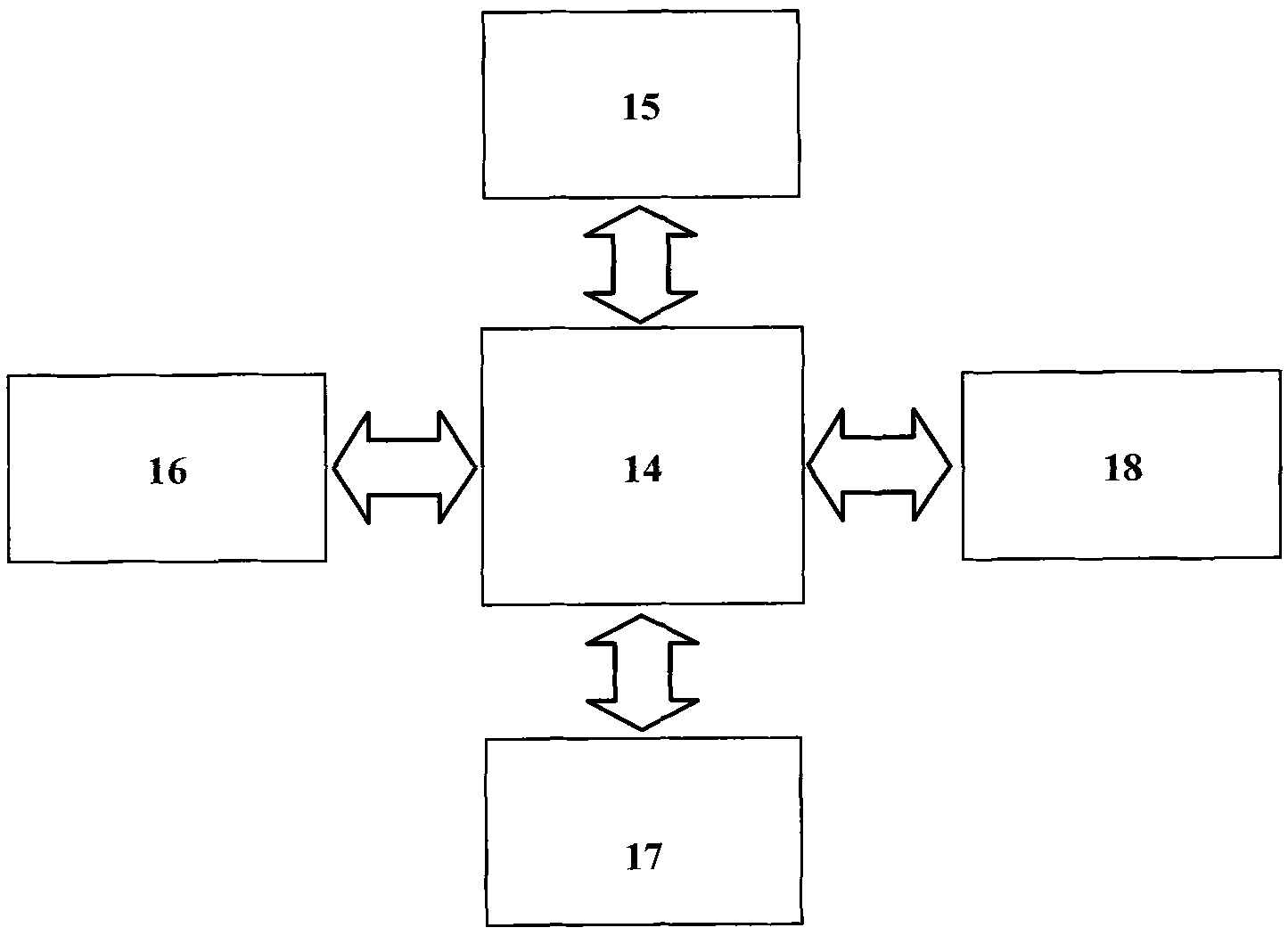

[0039] Embodiments of the device of the present invention are Figure 1-2 As shown, it includes a microprocessor interface module 1, an IPv6 packet encapsulation sending module 2, an IPv6 packet unpacking analysis module 3, an Ethernet MAC controller module 4, a SRAM controller module 5 and a user interaction module 6, and is characterized in that The microprocessor interface module 1 is connected with the external microprocessor 15, the IPv6 data packet encapsulation sending module 2, the IPv6 data packet unpacking analysis module 3, the SRAM controller module 5 and the user interaction module 6 respectively, and sends the external microprocessor 15 The address, data and control signals of the system are synchronized and converted into internal control signals and configuration information, requesting the IPv6 data packet encapsulation and sending module 2 to perform preprocessing and sending operations, and receiving the request sig...

Embodiment 2

[0045] Embodiment 2: (method embodiment)

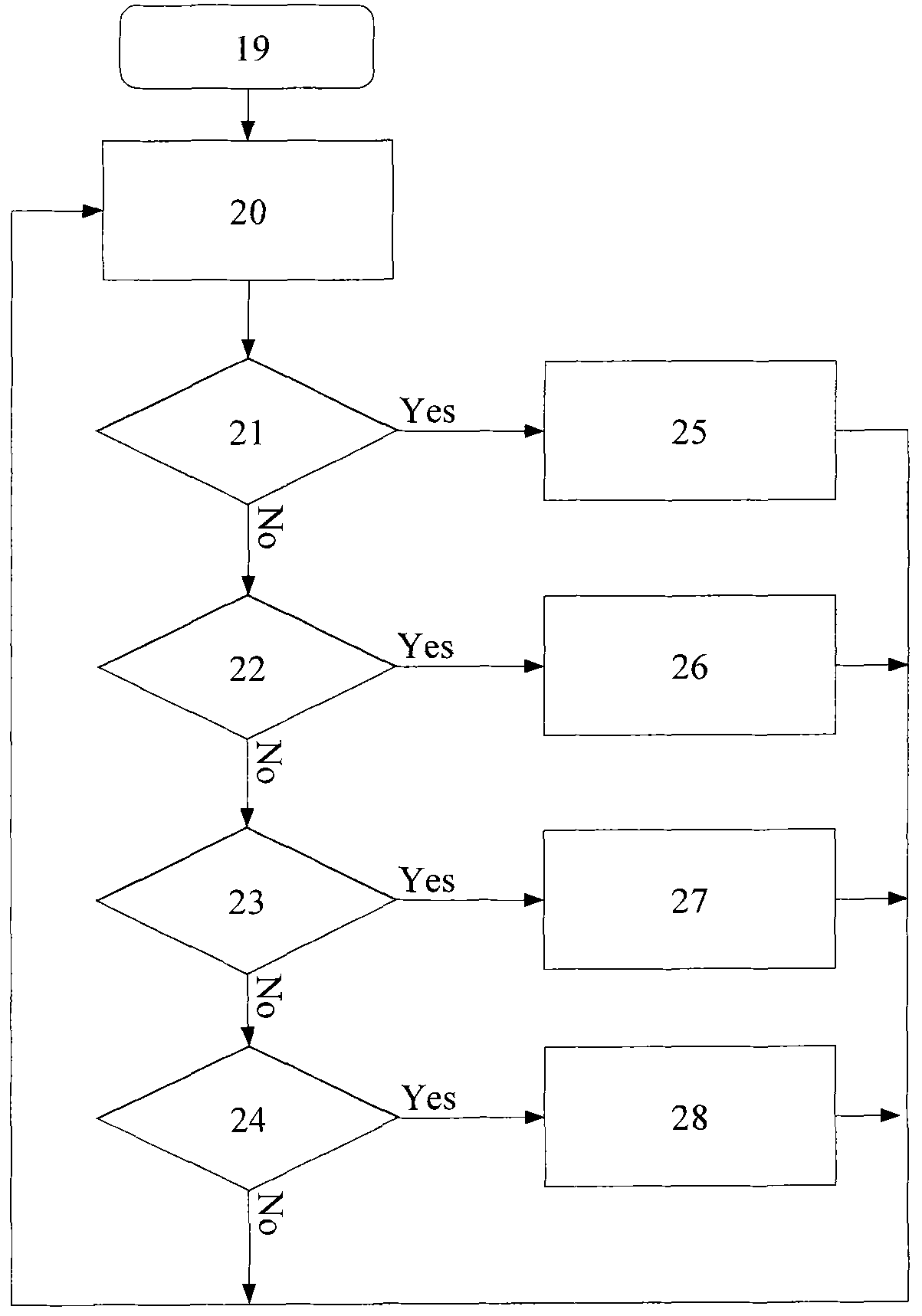

[0046] The operating method of the microprocessor interface module in the device of the present invention is as image 3 As shown, the steps are as follows:

[0047] 19. start;

[0048] 20. Receive instructions from the microprocessor;

[0049] 21. Receive a write register instruction from the microprocessor, if so, go to step 25; otherwise go to the next step;

[0050] 22. Receive the read register instruction from the microprocessor, if so, go to step 26; otherwise go to the next step;

[0051] 23. Receive a request to send an instruction from the microprocessor, if so, go to step 27; otherwise go to the next step;

[0052] 24. Receive the receiving completion signal from the IPv6 packet unpacking analysis module, if so, go to step 28; otherwise go to step 20;

[0053] 25. Write the data sent by the processor data bus into the register of the corresponding module, complete the configuration process, and then turn to step 20;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More