Method and system for simulating power supply network on chip

A technology of power supply network and simulation method, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as huge memory consumption, large design scale, and incapable of large-scale power supply network analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

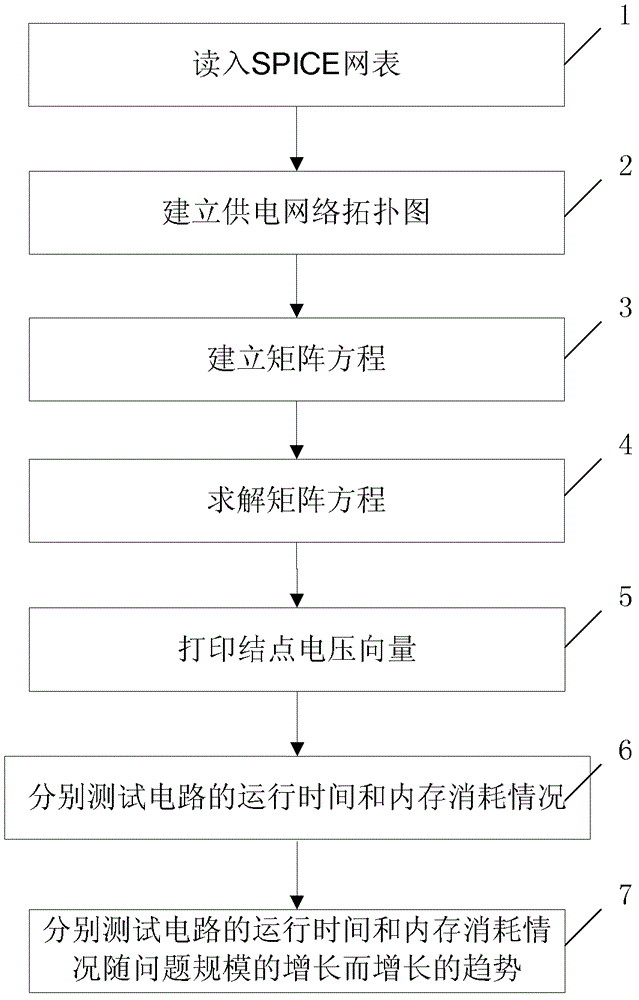

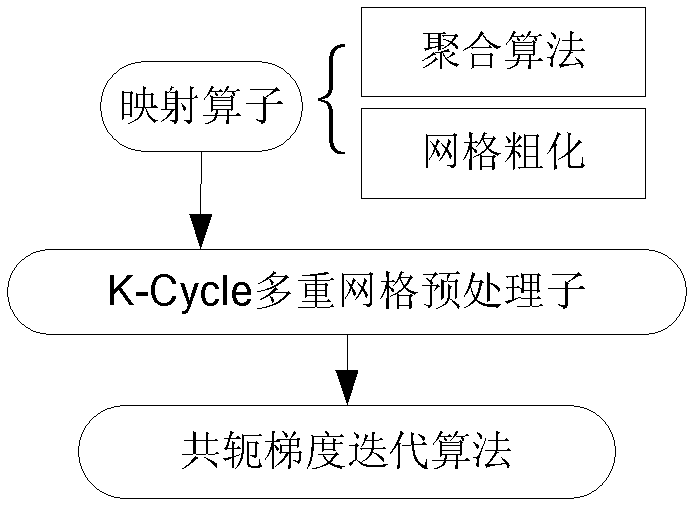

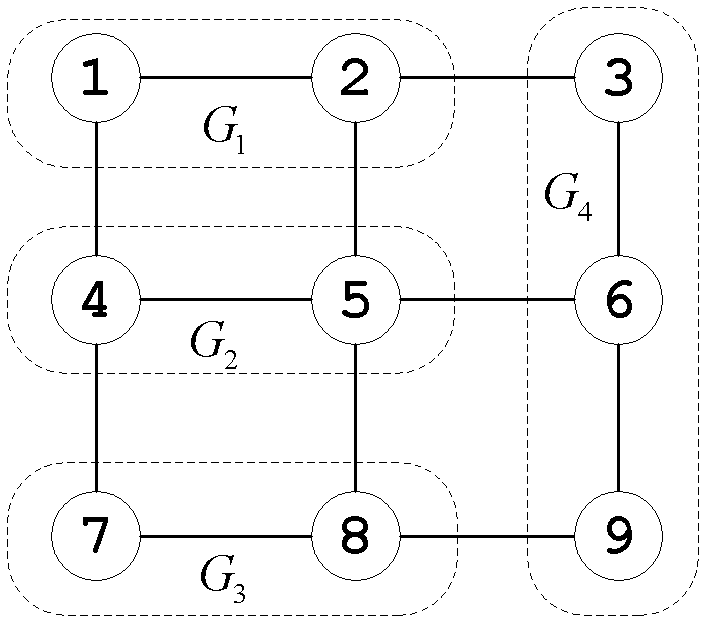

[0065] The invention provides an on-chip power supply network simulation system with linear complexity, which includes an efficient SPICE netlist parser, an efficient circuit builder, and a fast linear system solver. Using this simulation system, the power supply network in SPICE netlist format can be quickly and accurately analyzed for static voltage drop, and it has good convergence stability. The power supply network simulation system first reads the netlist in SPICE format, stores the electrical components and node information in the power supply network into the data structure, and then builds the power supply network into a simulation matrix and the right-hand current vector. The conjugate gradient algorithm with the grid as a preprocessing sub-process solves the node voltage vector of the power supply network and outputs it.

[0066] The present invention will be described in detail below with reference to the accompanying drawings.

[0067] The on-chip power supply ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More