Patents

Literature

277 results about "Conjugate gradient method" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In mathematics, the conjugate gradient method is an algorithm for the numerical solution of particular systems of linear equations, namely those whose matrix is symmetric and positive-definite. The conjugate gradient method is often implemented as an iterative algorithm, applicable to sparse systems that are too large to be handled by a direct implementation or other direct methods such as the Cholesky decomposition. Large sparse systems often arise when numerically solving partial differential equations or optimization problems.

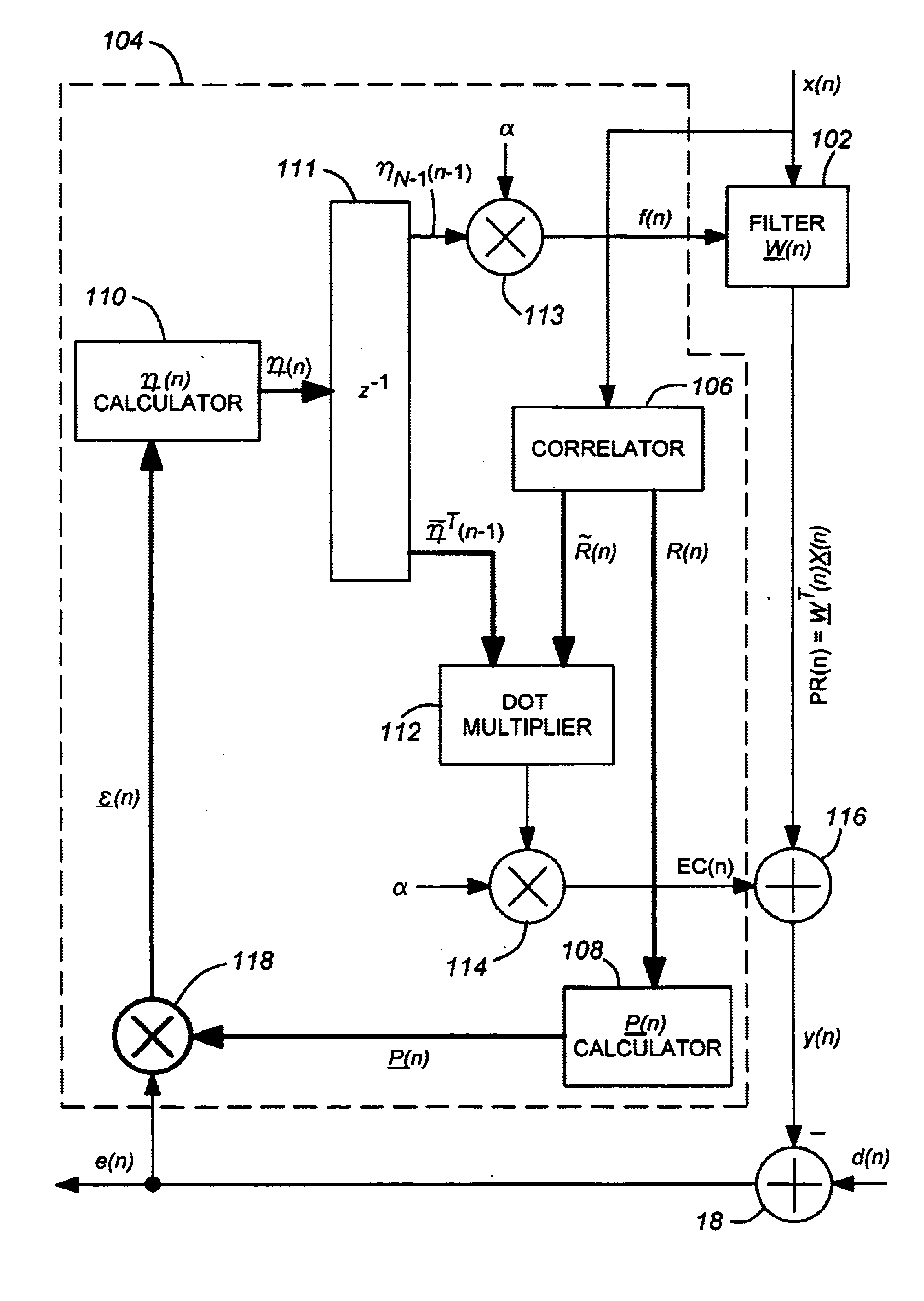

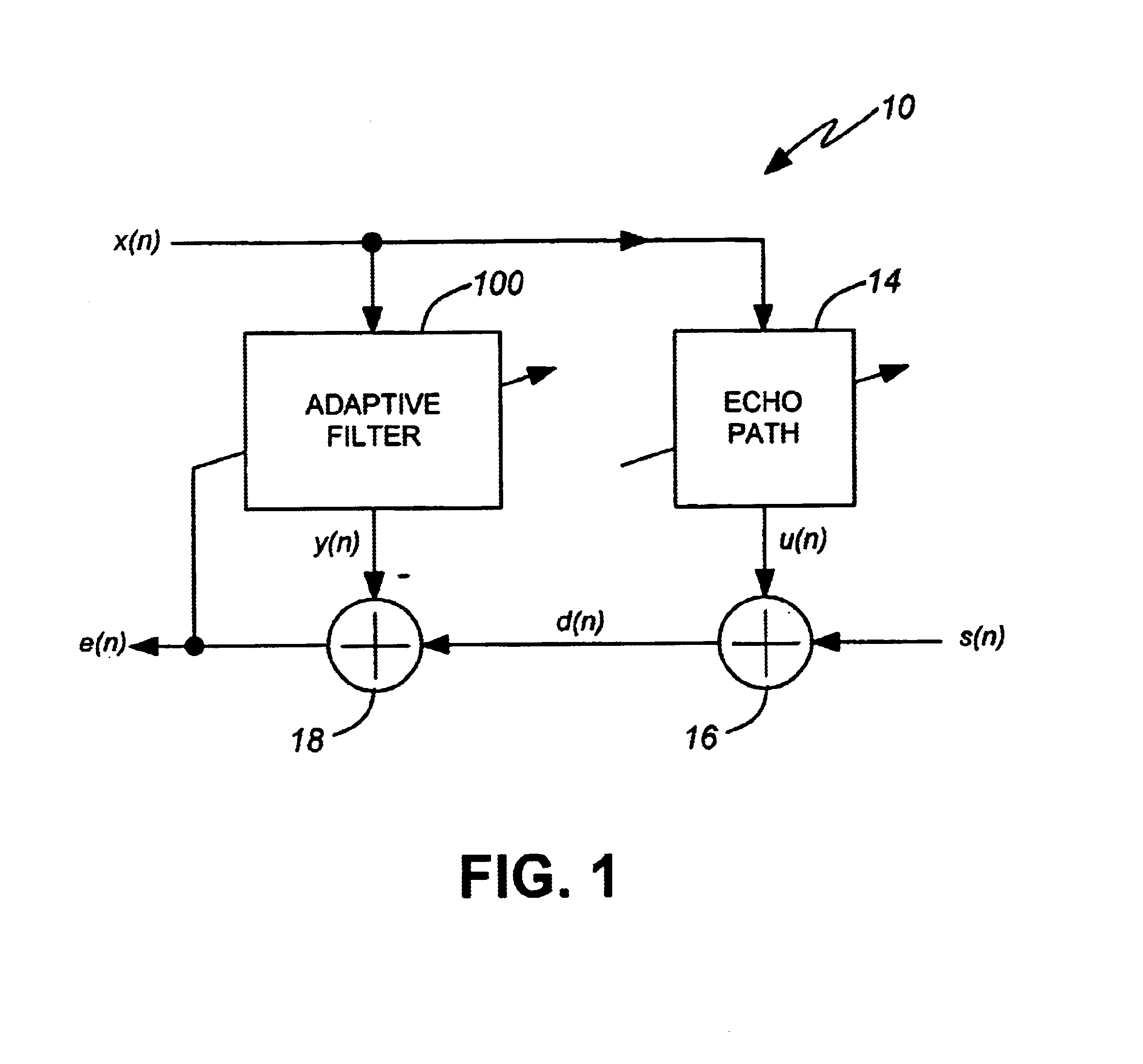

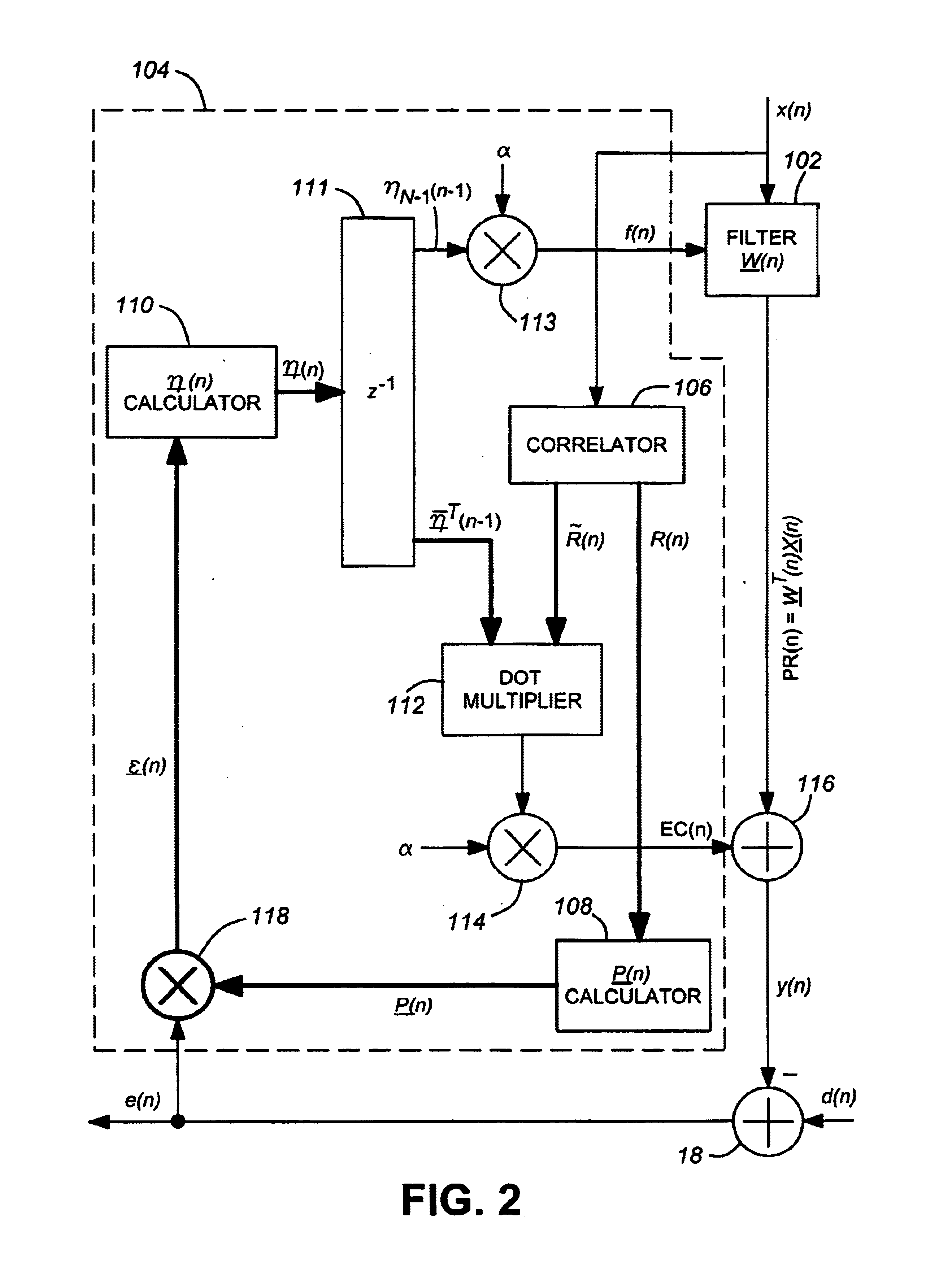

Stable adaptive filter and method

Stable adaptive filter and method are disclosed. The invention solves a problem of instability associated with Fast Affine Projection adaptive filters caused by error accumulation in an inversion process of an auto-correlation matrix. The Stable FAP uses a simplification of setting a normalized step size close to unity and reduces a problem of the matrix inversion to solving a system of linear equations whose solution coincides with a first column of the inverse auto-correlation matrix. The system of linear equations is then solved by one of descending iterative methods which provide inherent stability of operation due to intrinsic feedback adjustment. As a result, inevitable numerical errors are not accumulated, being corrected as the process goes on. In first and second embodiments of the invention the system of linear equation is solved by steepest descent and conjugate gradient methods respectively. Being immune to numerical errors, the invented method and filter are suitable for various DSP platforms, e.g., 16 and 24 bit fixed-point as well as floating point platform.

Owner:CIENA

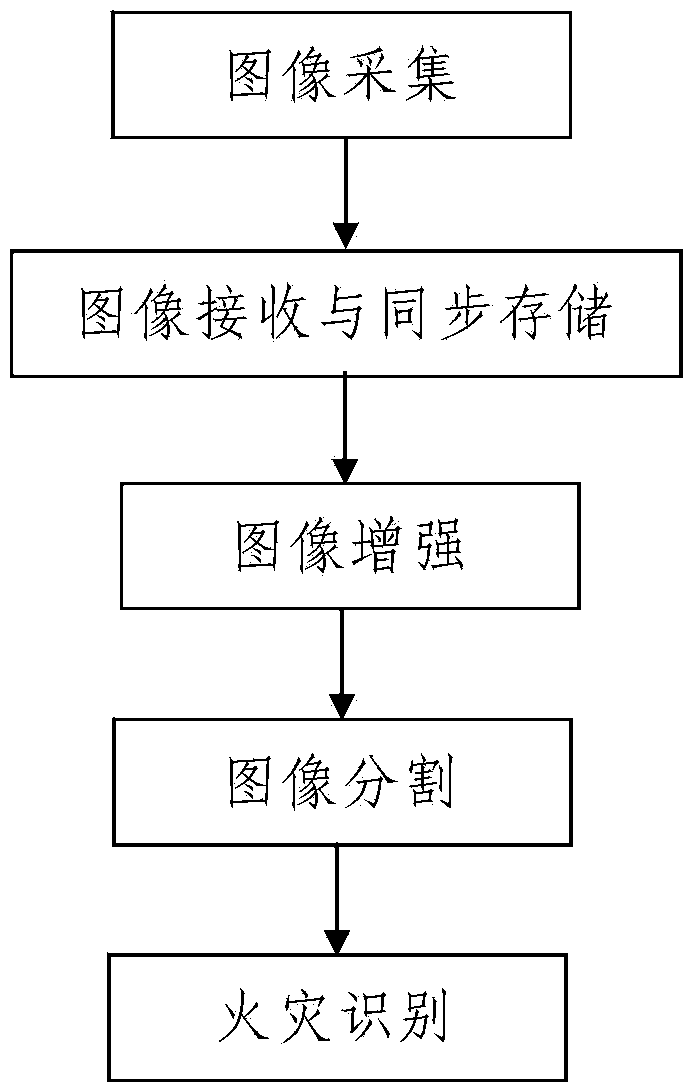

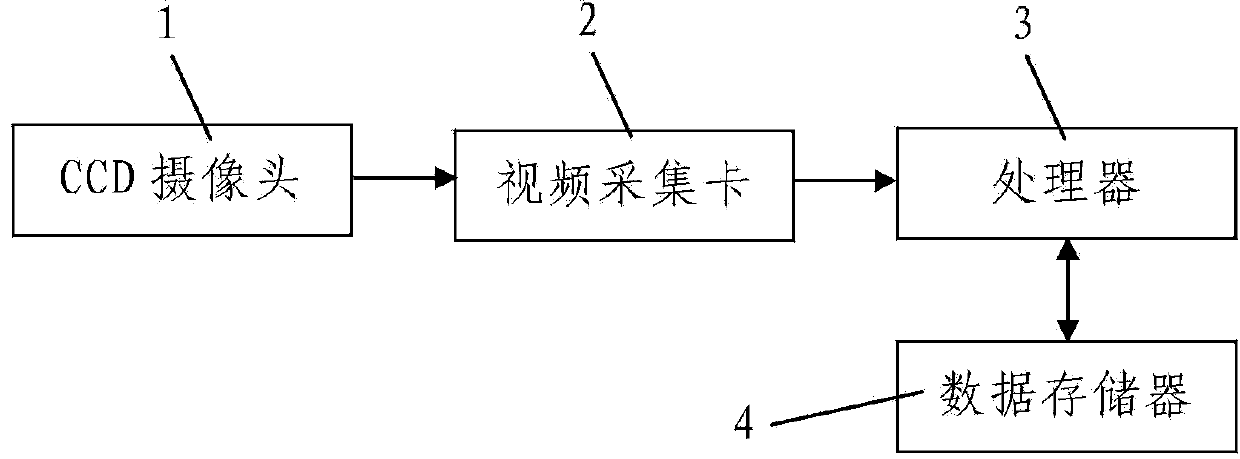

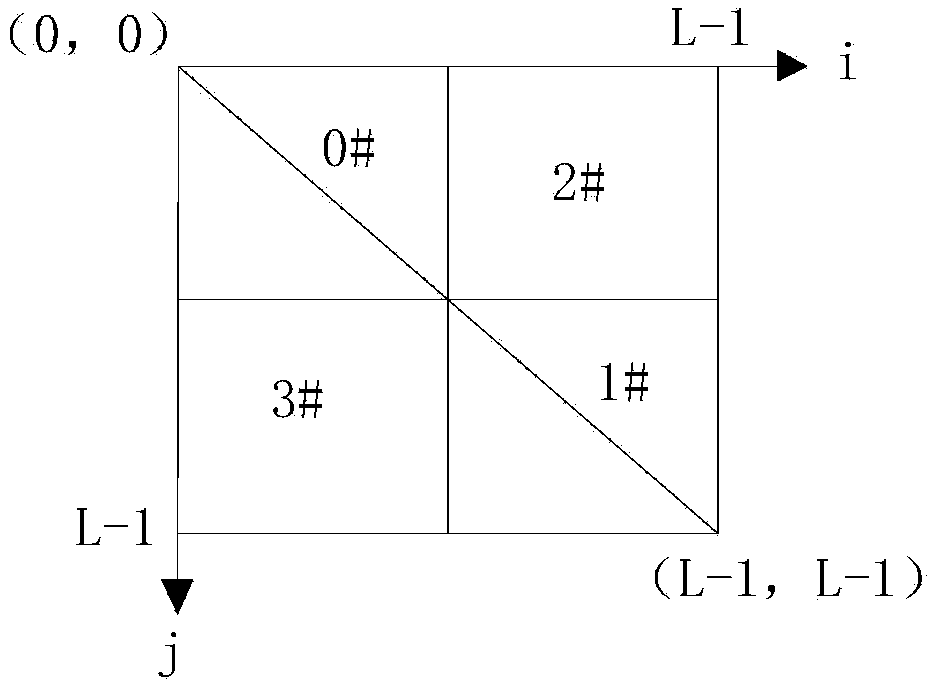

Image type fire flame identification method

ActiveCN103886344AThe method steps are simpleReasonable designCharacter and pattern recognitionImaging processingFeature extraction

The invention discloses an image type fire flame identification method. The method comprises the following steps of 1, image capturing; 2, image processing. The image processing comprises the steps of 201, image preprocessing; 202, fire identifying. The fire identifying comprises the steps that indentifying is conducted by the adoption of a prebuilt binary classification model, the binary classification model is a support vector machine model for classifying the flame situation and the non-flame situation, wherein the building process of the binary classification model comprises the steps of I, image information capturing;II, feature extracting; III, training sample acquiring; IV, binary classification model building; IV-1, kernel function selecting; IV-2, classification function determining, optimizing parameter C and parameter D by the adoption of the conjugate gradient method, converting the optimized parameter C and parameter D into gamma and sigma 2; V, binary classification model training. By means of the image type fire flame identification method, steps are simple, operation is simple and convenient, reliability is high, using effect is good, and the problems that reliability is lower, false or missing alarm rate is higher, using effect is poor and the like in an existing video fire detecting system under a complex environment are solved effectively.

Owner:东开数科(山东)产业园有限公司

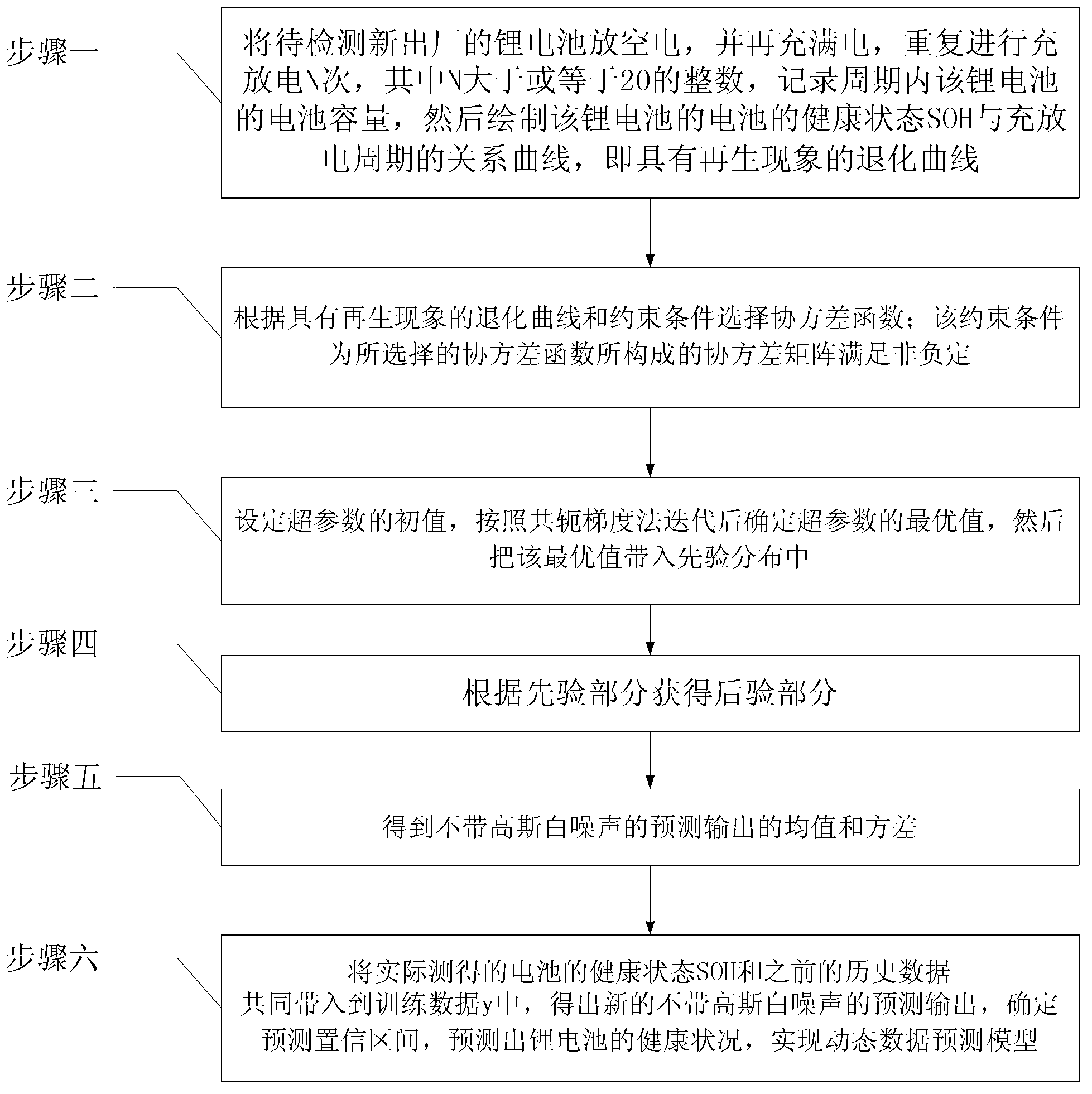

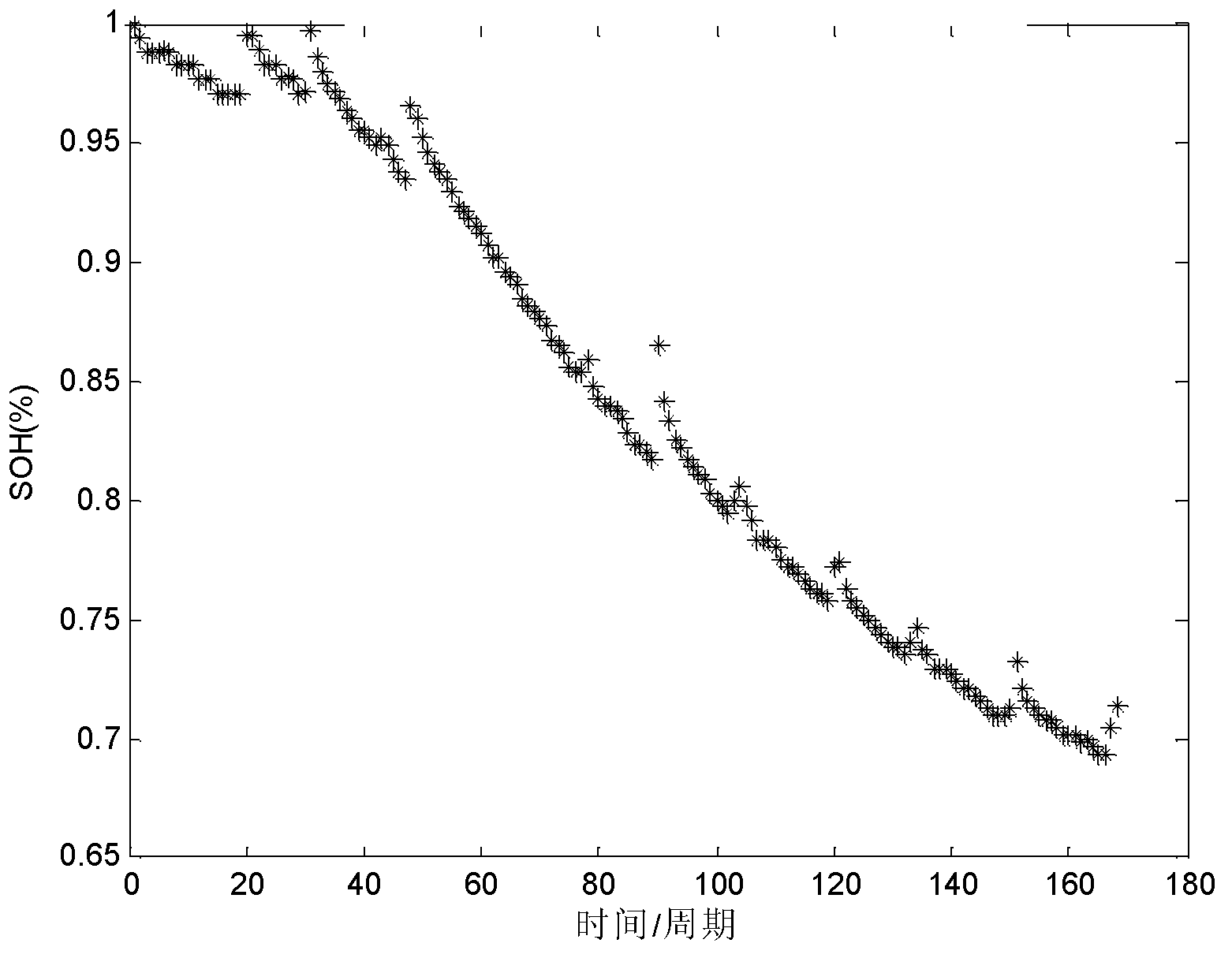

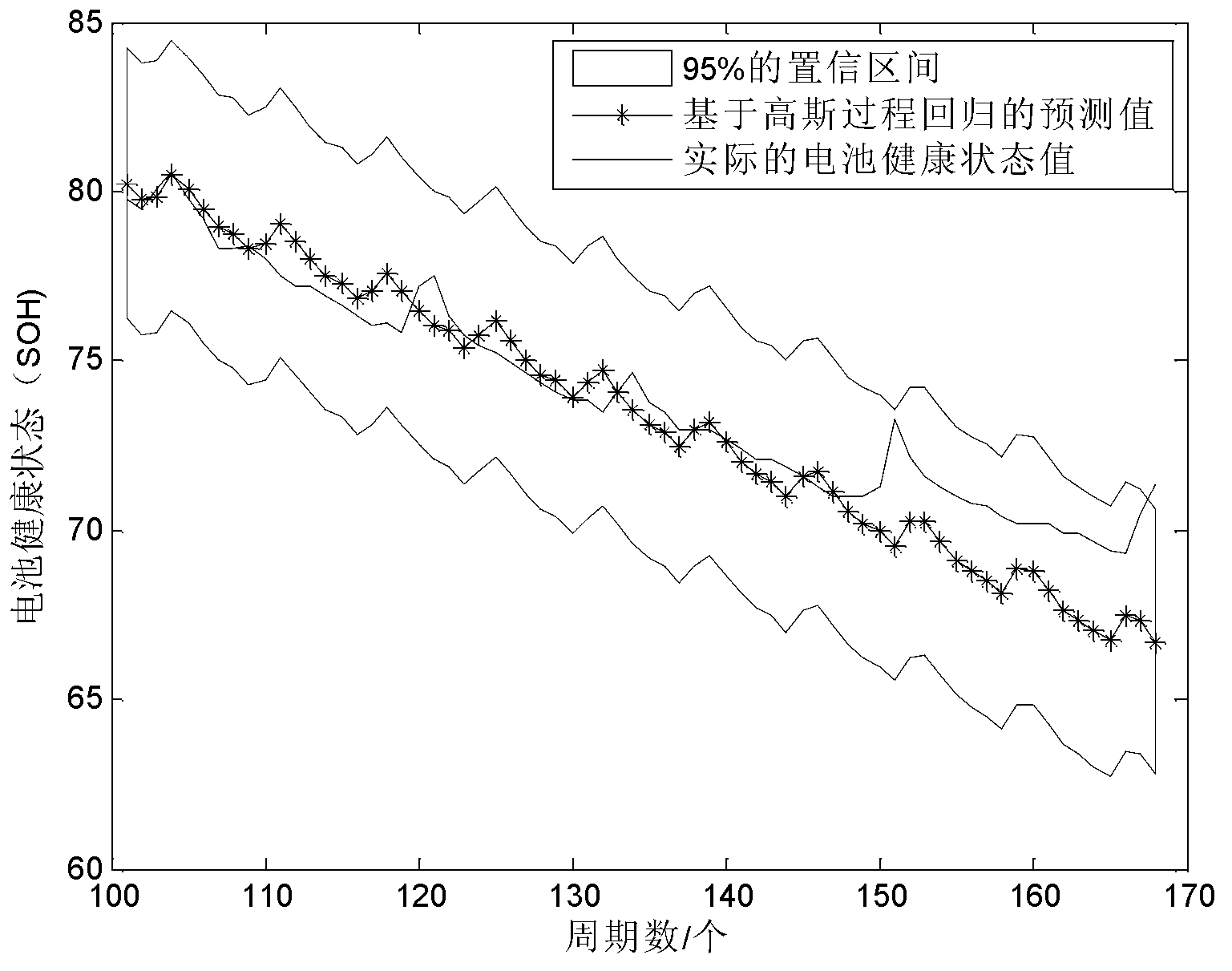

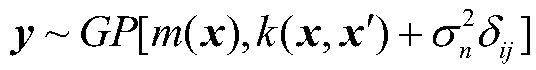

Gaussian process regression-based method for predicting state of health (SOH) of lithium batteries

InactiveCN102798823AImprove adaptabilityImprove effectivenessElectrical testingConfidence intervalCharge discharge

The invention discloses a Gaussian process regression-based method for predicting state of health (SOH) of lithium batteries, relates to a method for predicting the SOH of the lithium batteries, belongs to the fields of electrochemistry and analytic chemistry and aims at the problem that the traditional lithium batteries are bad in health condition prediction adaptability. The method provided by the invention is realized according to the following steps of: I. drawing a relation curve of the SOH of a lithium battery and a charge-discharge period; II, selecting a covariance function according to a degenerated curve with a regeneration phenomenon and a constraint condition; III, carrying out iteration according to a conjugate gradient method, then determining the optimal value of a hyper-parameter and bringing initial value thereof into prior distribution; IV, obtaining posterior distribution according to the prior part; V, obtaining the mean value and variance of predicted output f' without Gaussian white noise; and VI, together bringing the practically predicted SOH of the battery and the predicted SOH obtained in the step V into training data y to obtain the f', then determining the prediction confidence interval and predicting the SOH of the lithium battery. The method provided by the invention is used for detecting lithium batteries.

Owner:HARBIN INST OF TECH

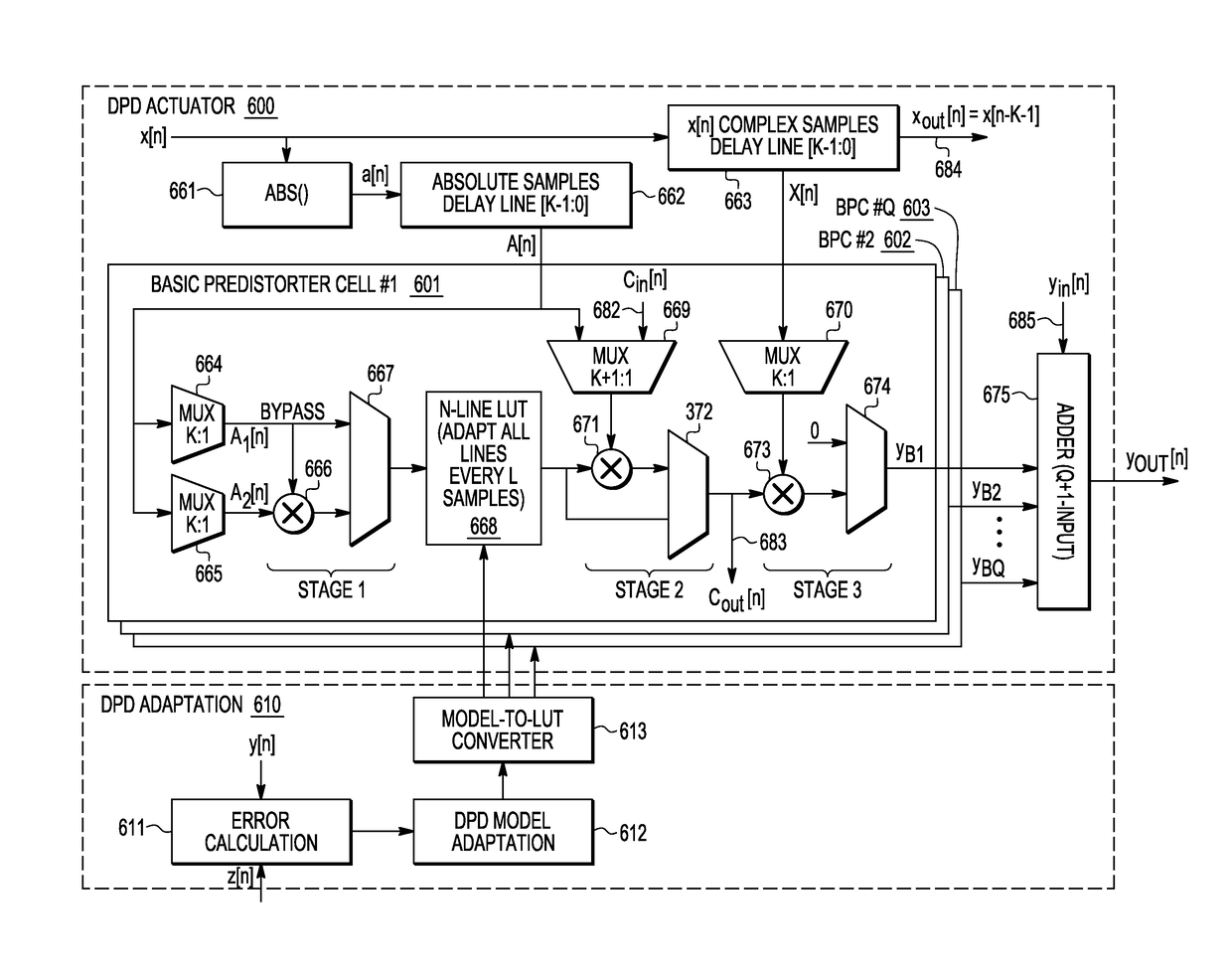

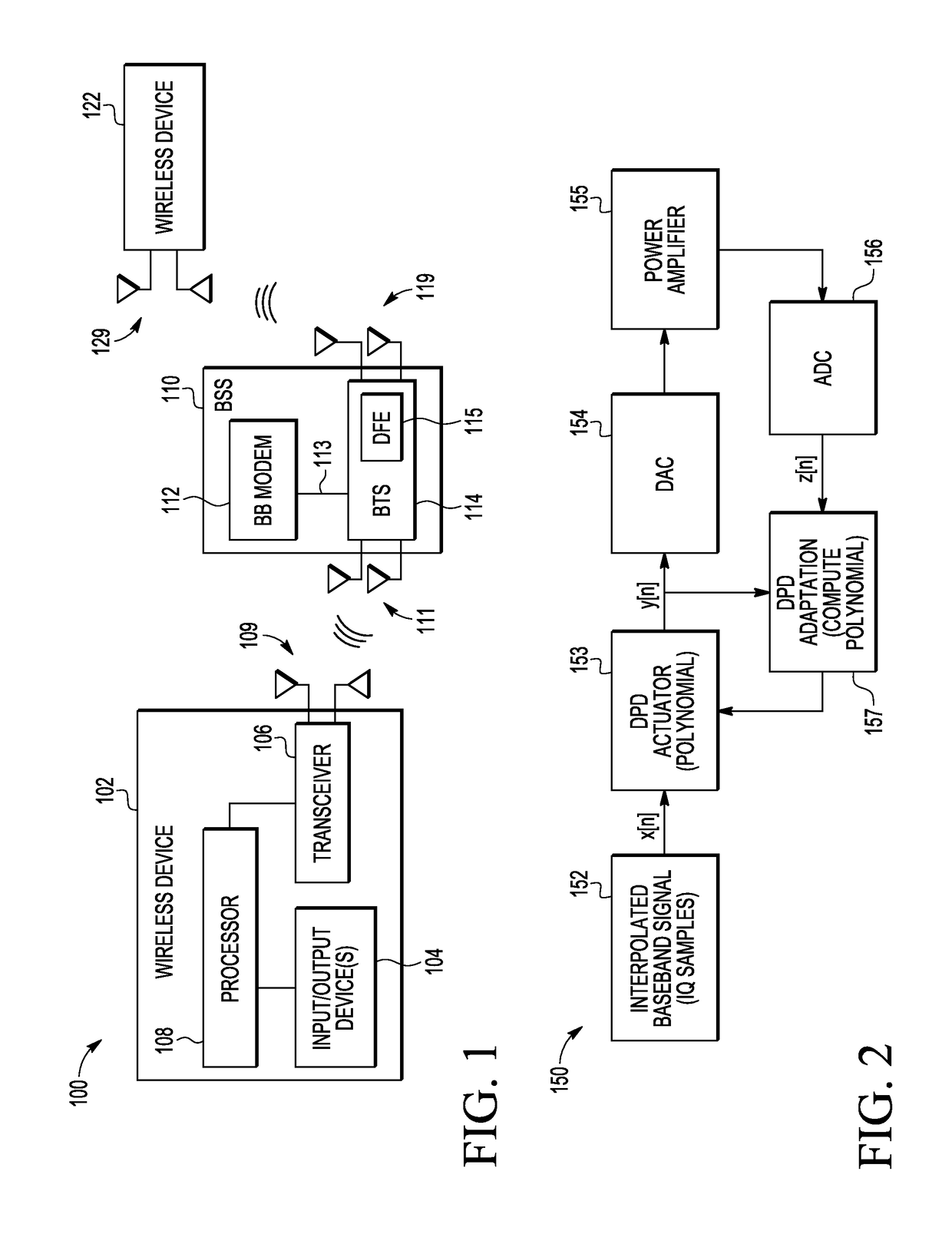

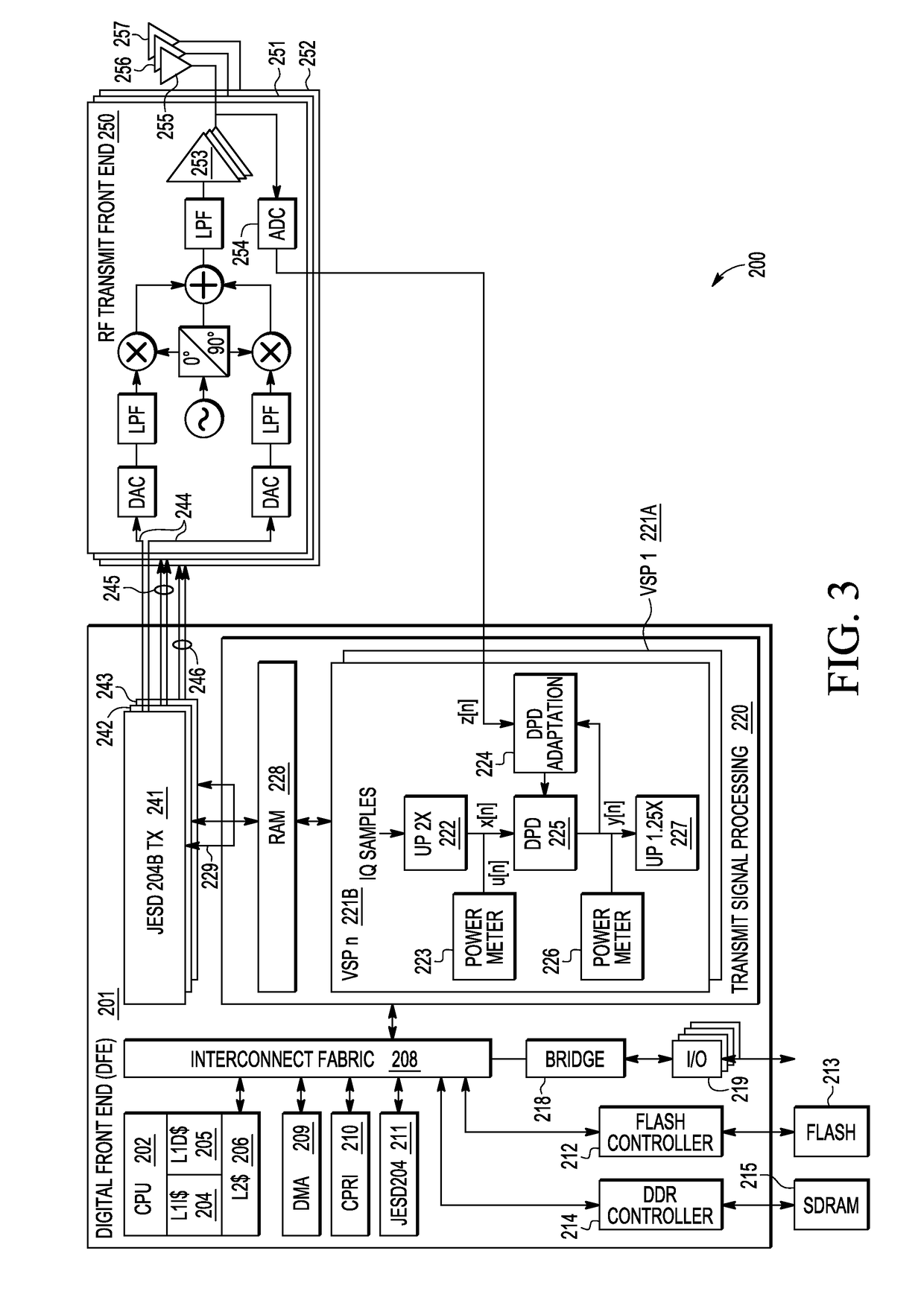

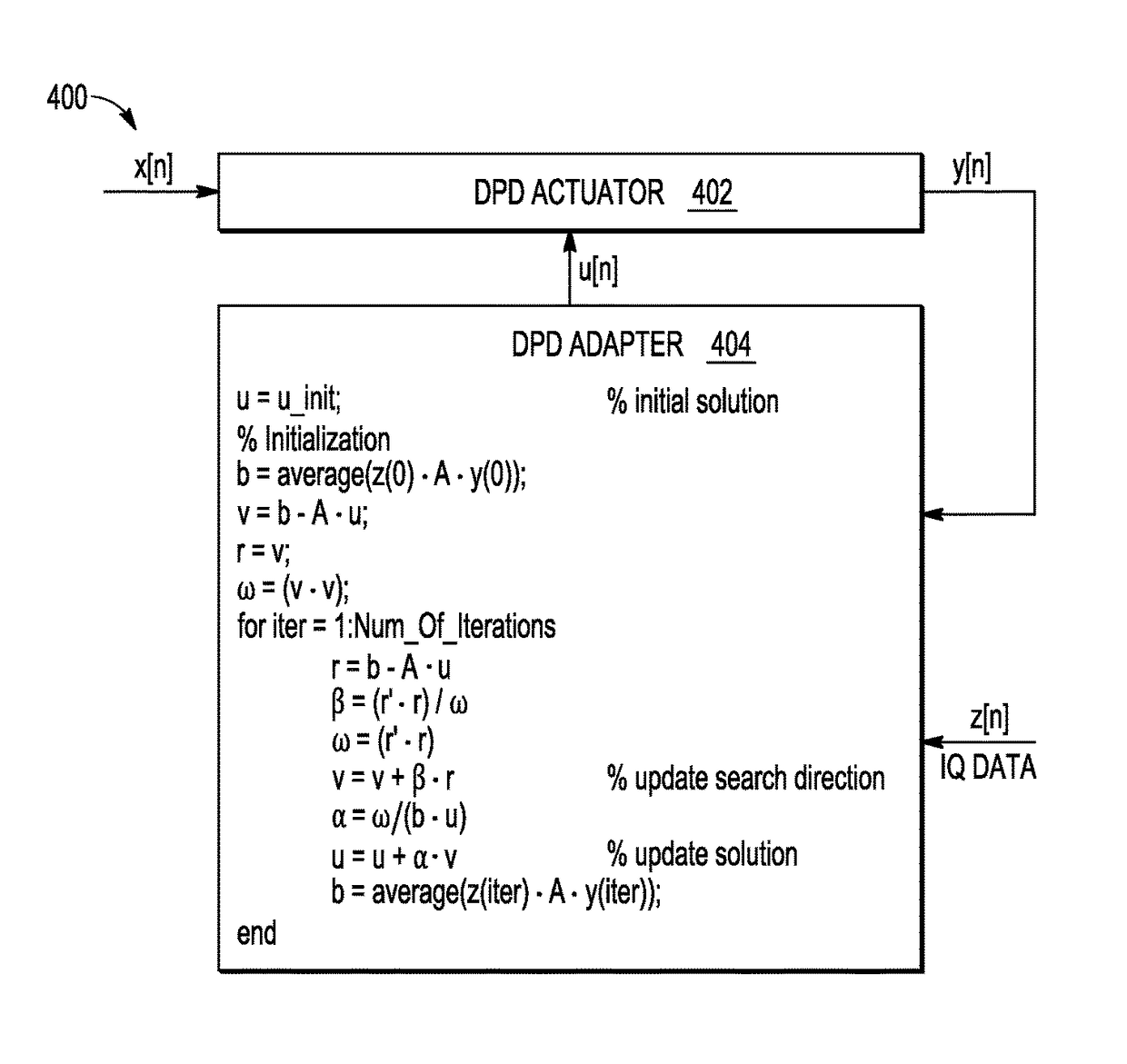

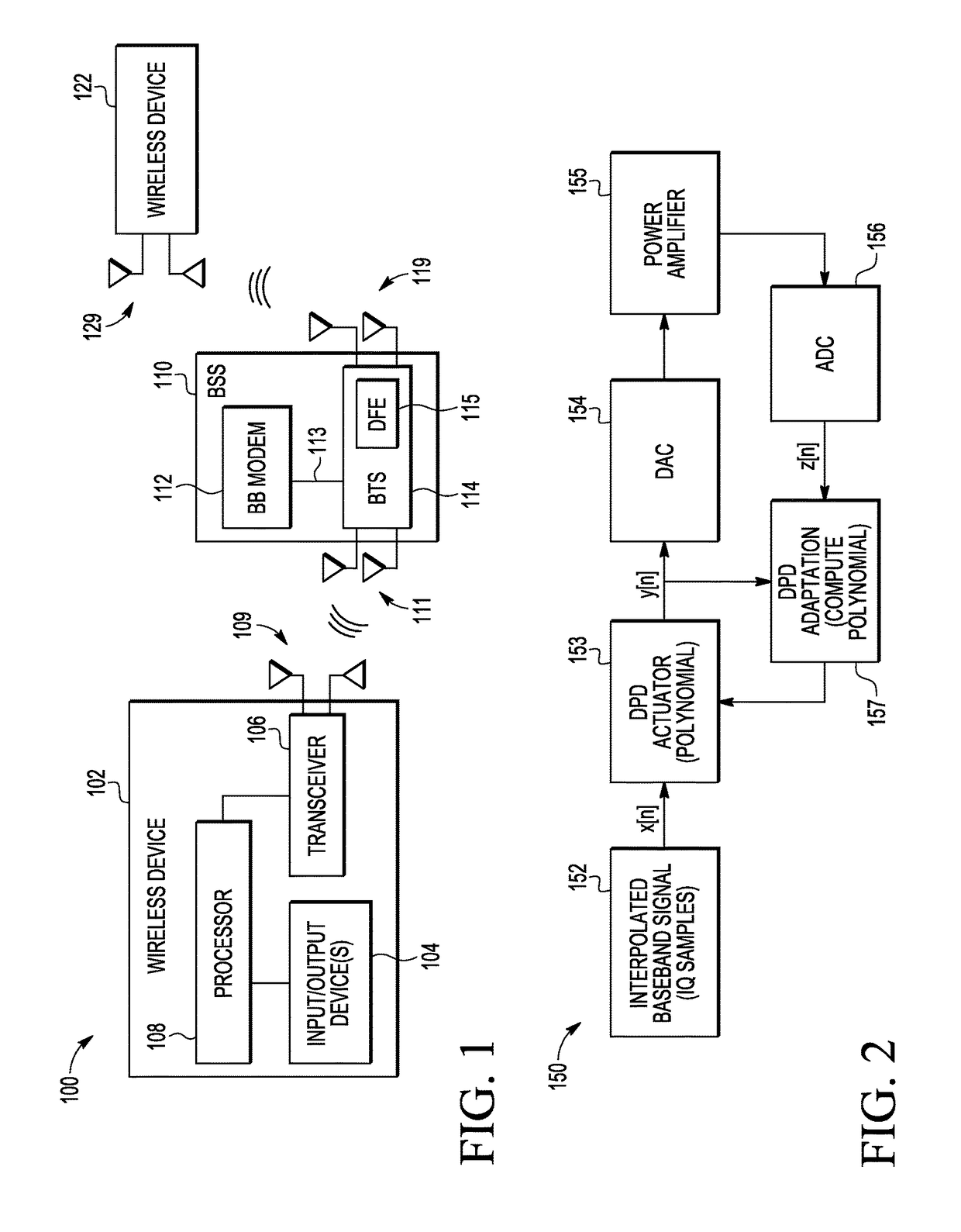

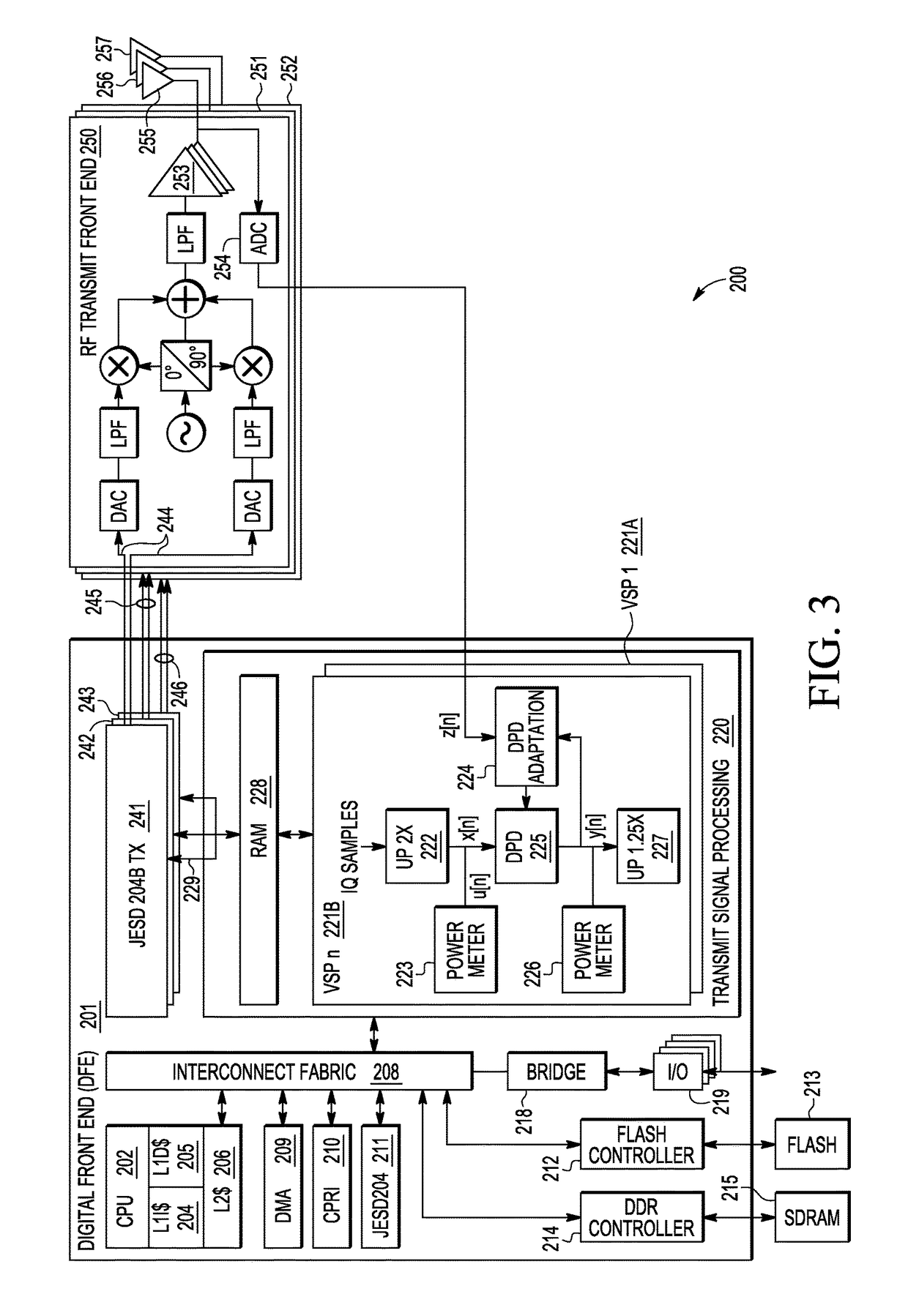

Fixed-Point Conjugate Gradient Digital Pre-Distortion (DPD) Adaptation

A predistortion method and apparatus are provided which use a DPD actuator (225) to apply a memory polynomial formed with first DPD coefficients to a first input signal x[n], thereby generating a first pre-distorted input signal y[n] which is provided to the non-linear electronic device (253) to produce the output signal, where the memory polynomial may be adaptively modified with a digital predistortion adapter (224) which computes second DPD coefficients u[n] with an iterative fixed-point conjugate gradient method which uses N received digital samples of the first pre-distorted input signal y[n] and a feedback signal z[n] captured from the output signal to process a set of conjugate gradient parameters (u, b, v, r, ω, α, β) at each predetermined interval, thereby updating the first DPD coefficients with the second DPD coefficients u[n] generate a second pre-distorted input signal which is provided to the non-linear electronic device.

Owner:NXP USA INC

Power system short-term load probability forecasting method, device and system

InactiveCN109214605AReduce forecast errorForecastingResourcesPredictive methodsConjugate gradient method

The invention discloses a power system short-term load probability forecasting method, a device and a system. The short-term load probability density forecasting model of Gaussian process quantile regression is established by selecting an optimal input variable set affecting the load. Firstly, the importance score of input variables is given by stochastic forest algorithm, and the influence degreeof each input variable is sorted. Secondly, particle swarm optimization algorithm is used to search the super-parameters of the model to form the optimal Gaussian process quantile regression prediction model, avoiding the adverse effect of artificial experience setting initial parameters on the prediction performance of the model. The invention can avoid the shortcomings of manual experience selection, the load forecasting model established in the optimal input variable set has low error, which further reduces the forecasting error, and overcomes the problems that the common conjugate gradient method is easy to fall into the local optimal solution, the iterative number is difficult to determine, and the optimization performance is greatly affected by the initial value selection, so that the self-searching and group cognitive ability can be brought into full play.

Owner:ELECTRIC POWER RESEARCH INSTITUTE OF STATE GRID SHANDONG ELECTRIC POWER COMPANY +2

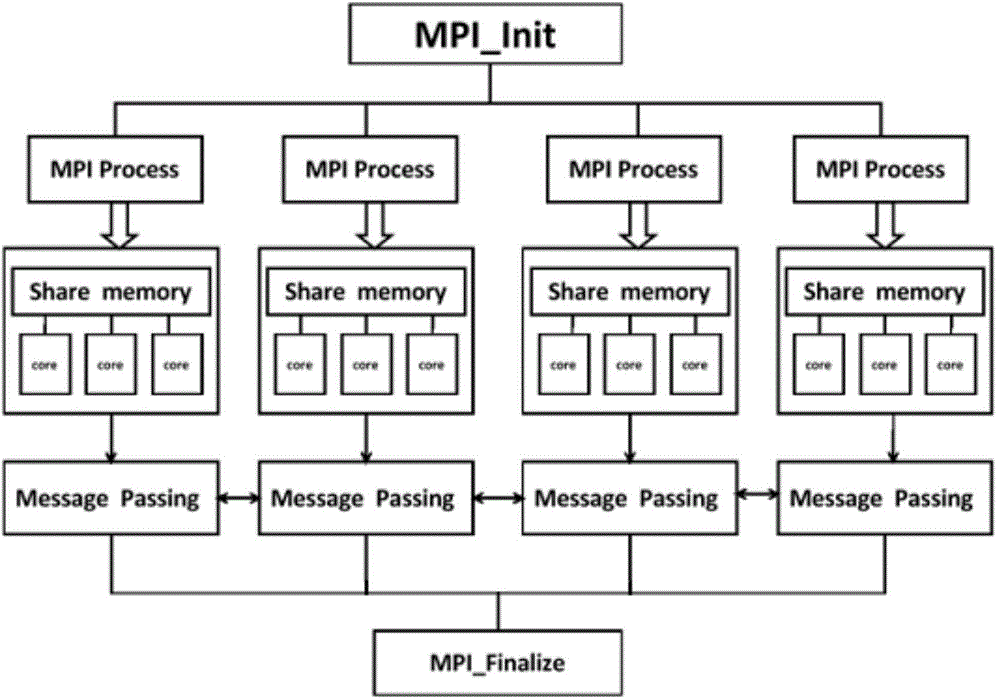

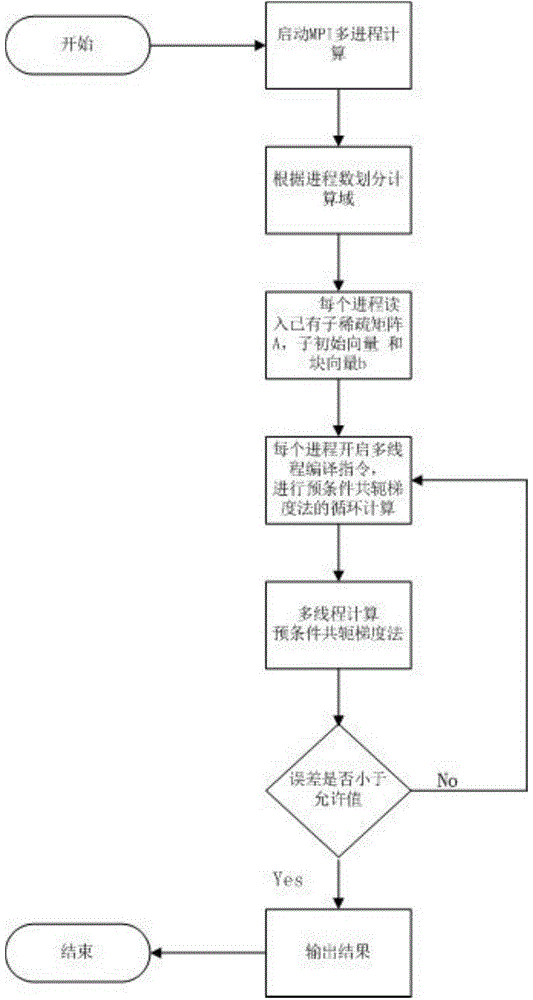

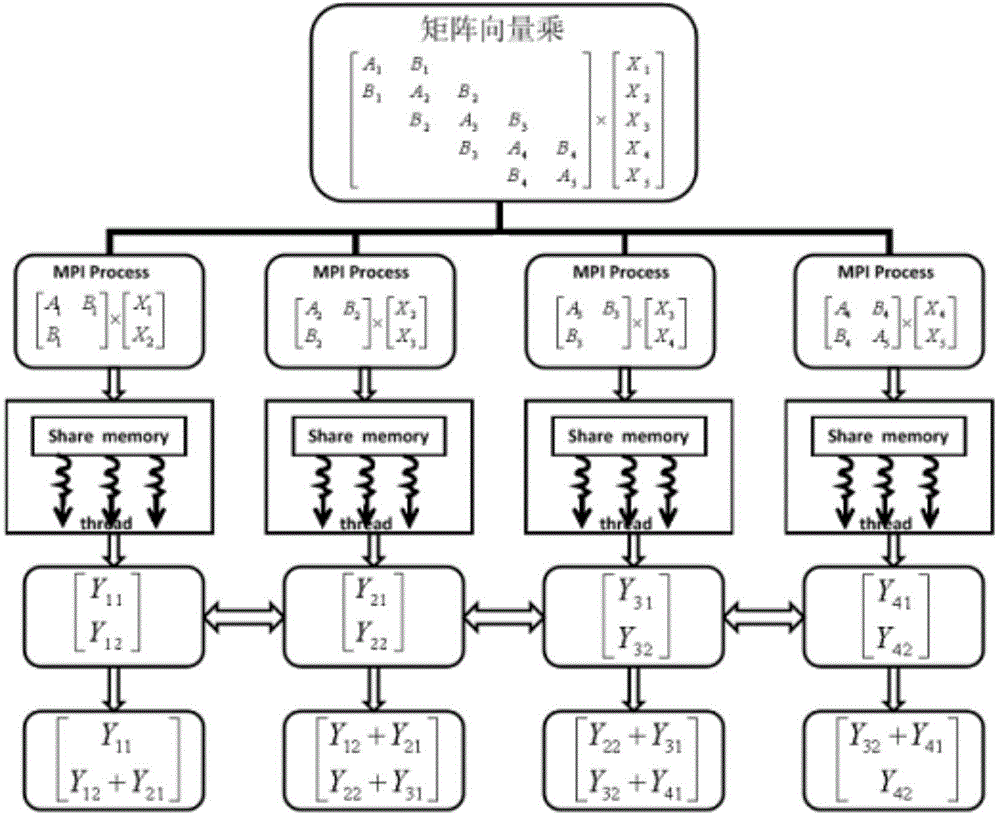

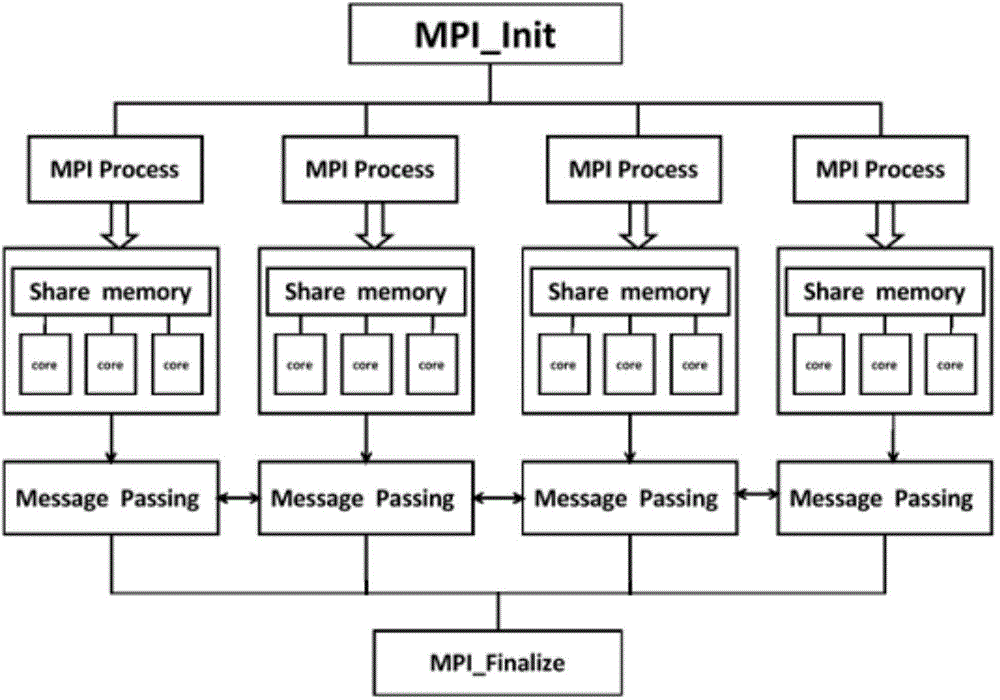

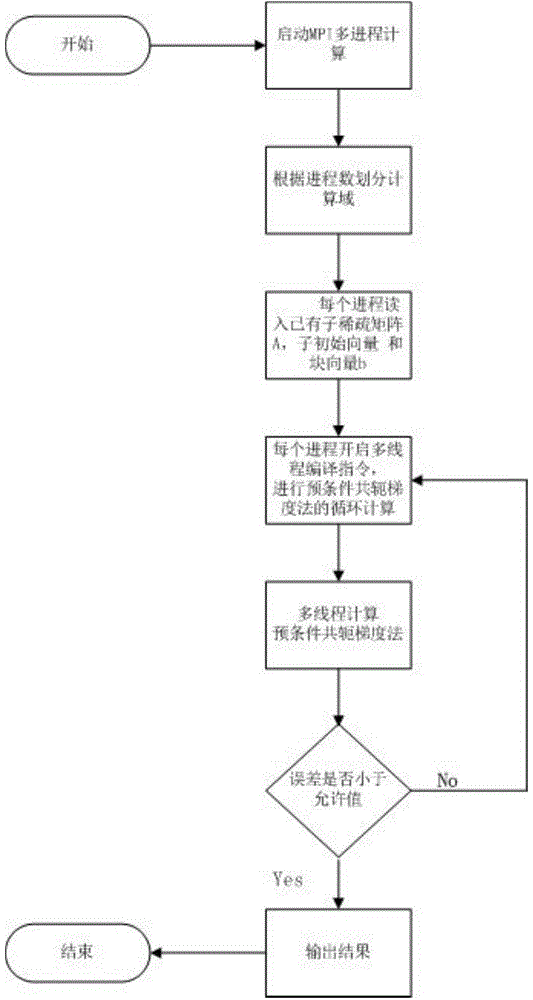

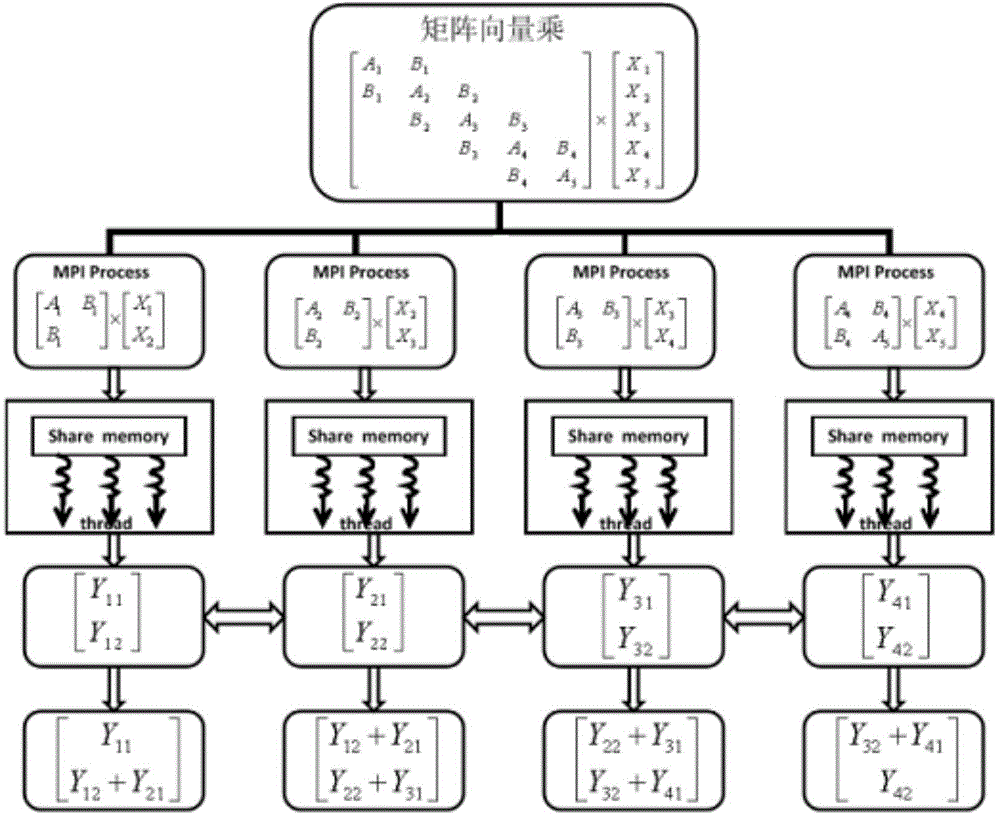

Method for increasing computing speed through parallel computing based on MPI and OpenMP hybrid programming model

ActiveCN104461466AAvoid interactionCalculation speedConcurrent instruction executionNODALHybrid programming

The invention discloses a method for increasing the computing speed through parallel computing based on an MPI and OpenMP hybrid programming model. The method includes the steps that the callable MPI process number and OpenMP thread number are determined according to the computing node number and the available CPU core number in nodes; an existing sub sparse matrix A, the sub initial vector x0, the block vector b and the maximum computing tolerance Tolerance are read into each process; a multi-thread compiling command is enabled for each process; cycle computing of a precondition conjugate gradient method is conducted on all the processes; if the computed error is smaller than the permissible value, cycle computing is ended, and otherwise, cycle computing is continuously conducted; computing results of all the processes are reduced, and a solution of a problem is output; when parallel computing is conducted, MPI processes are started, multi-thread resolving is conducted on the problem, parallel computing among the nodes is started, all the MPI processes are distributed to one computing node, and information is exchanged through message transmission among the processes; then in all the MPT processes, an OpenMP guidance command is used to create a set of threads, and the threads are distributed to different processors of the computing node to be executed.

Owner:INST OF SOFTWARE APPL TECH GUANGZHOU & CHINESE ACAD OF SCI

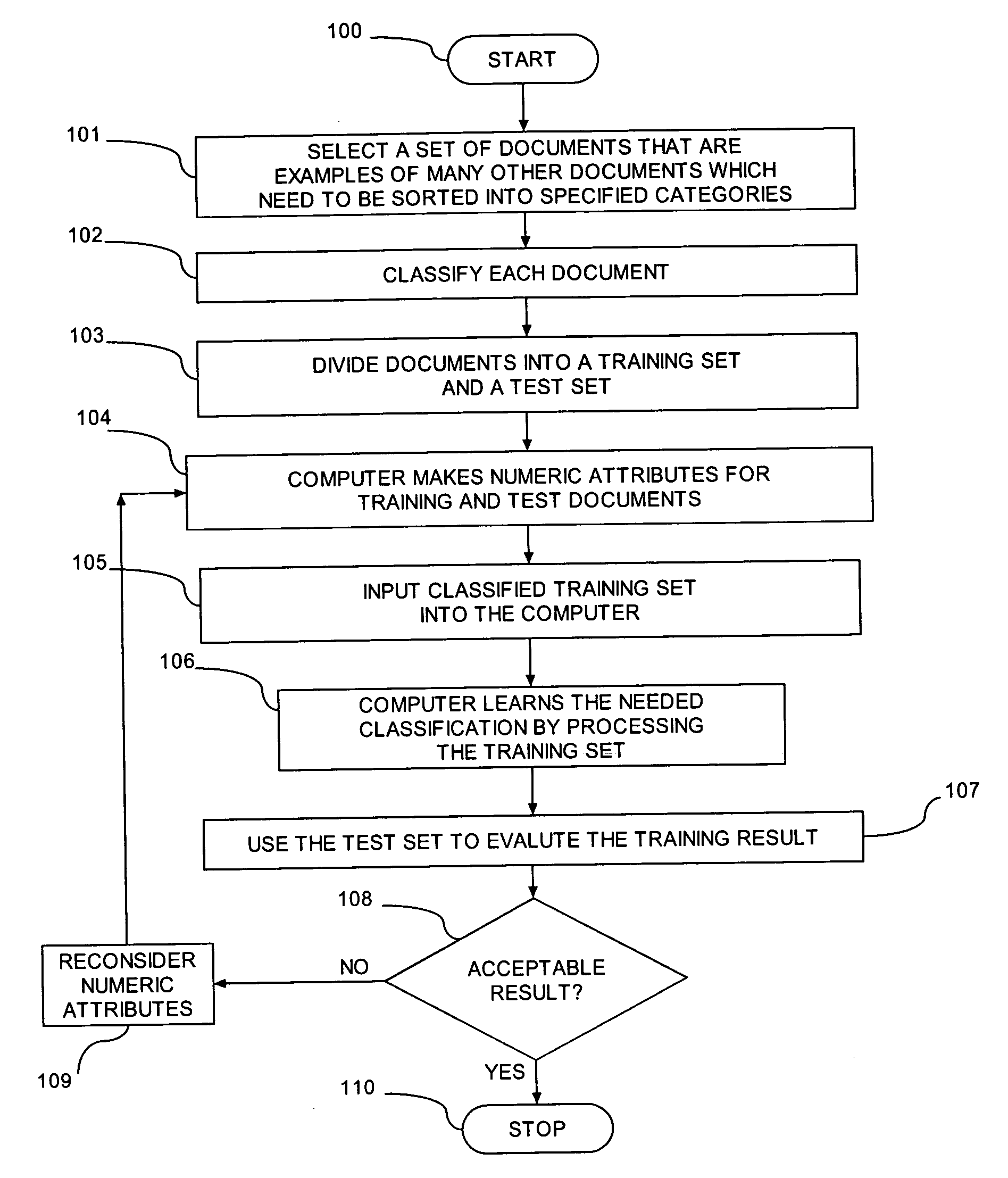

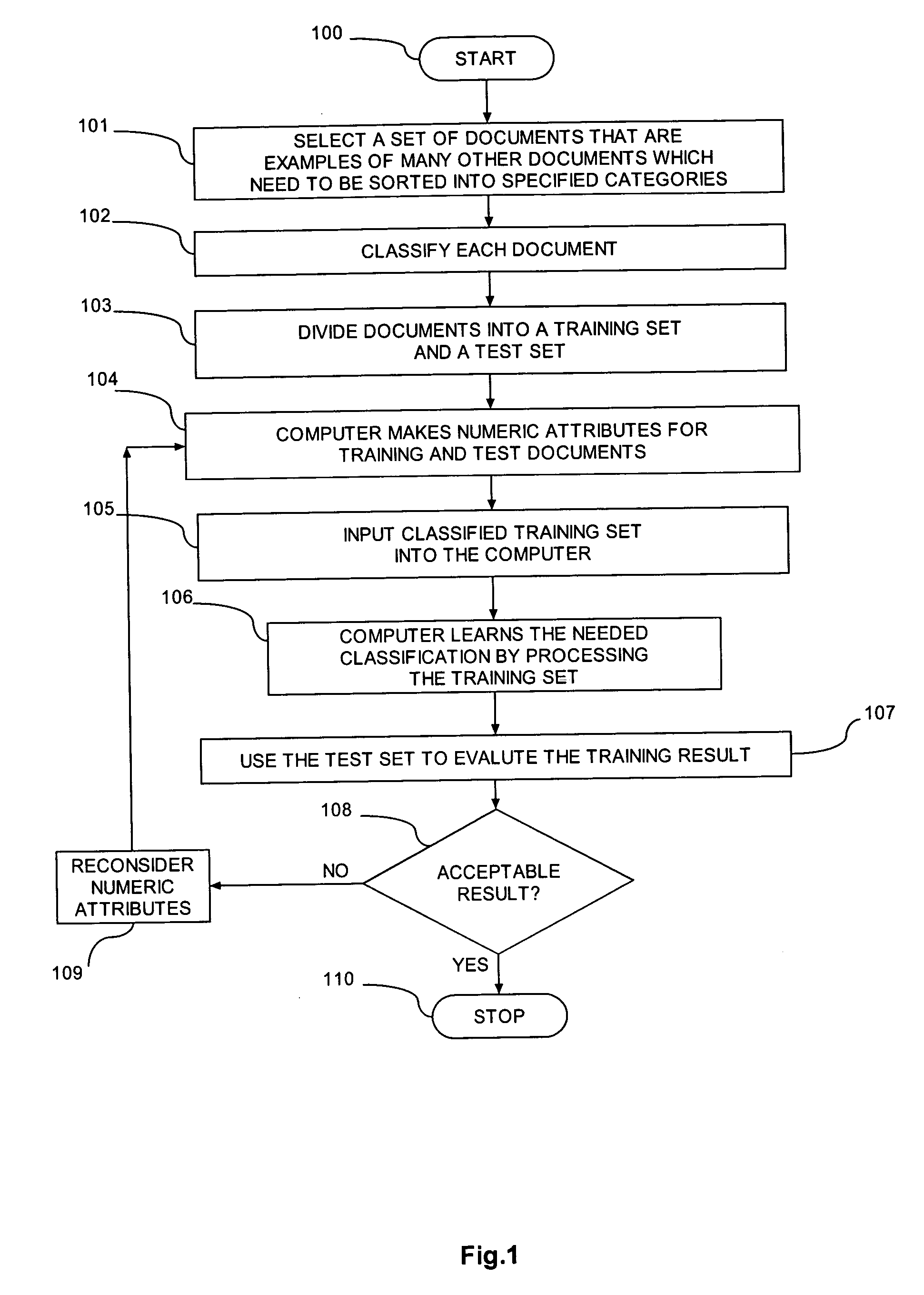

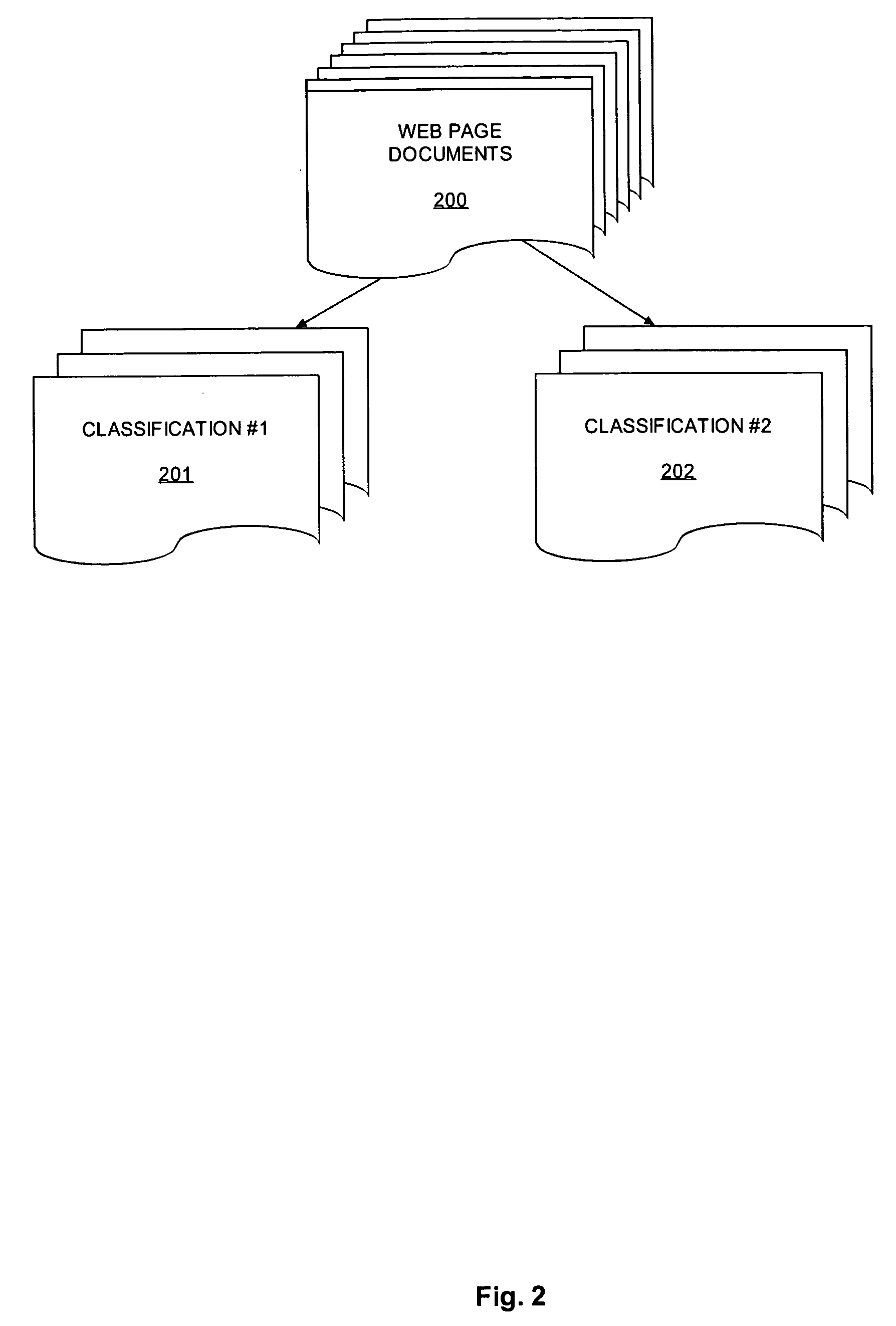

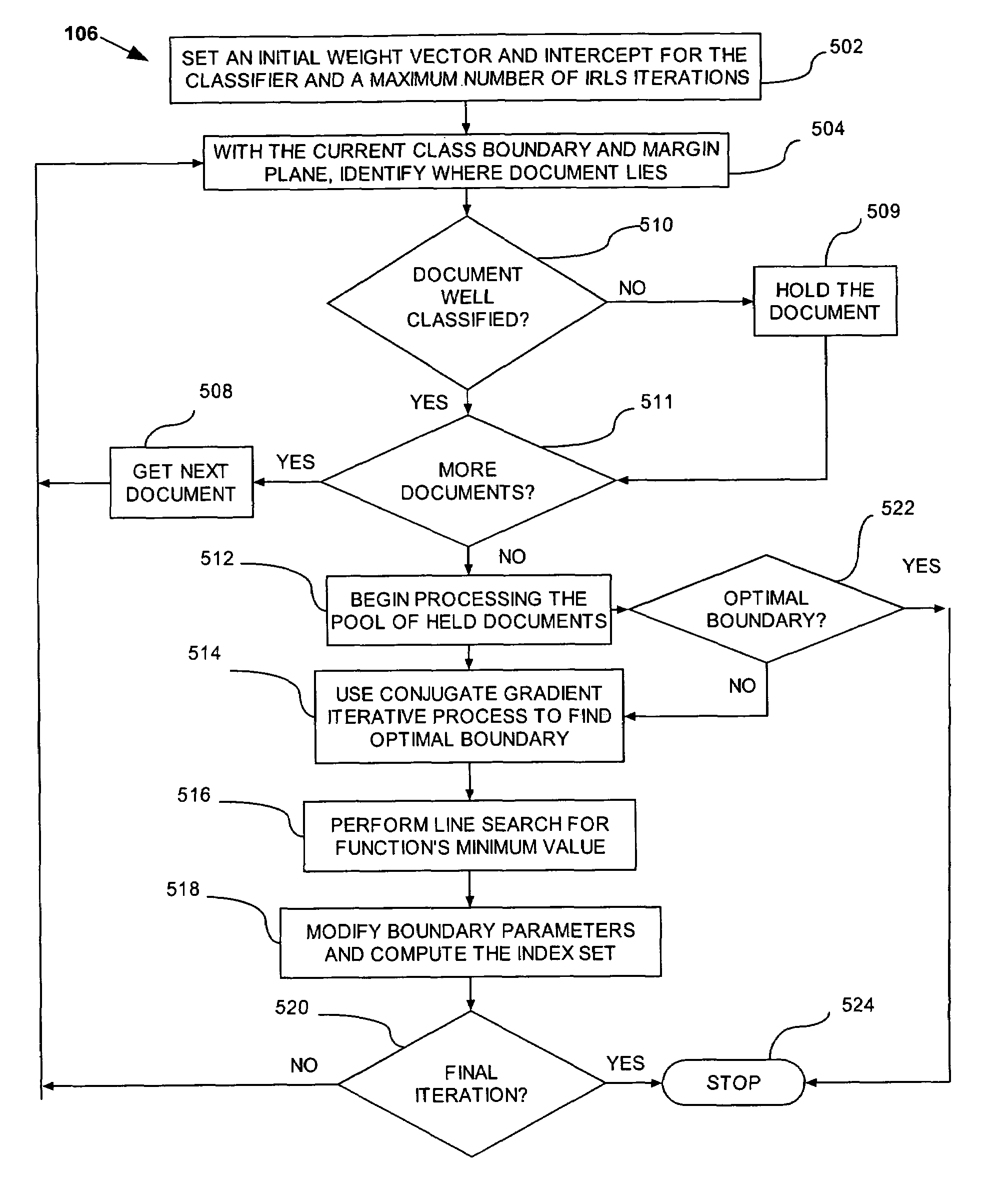

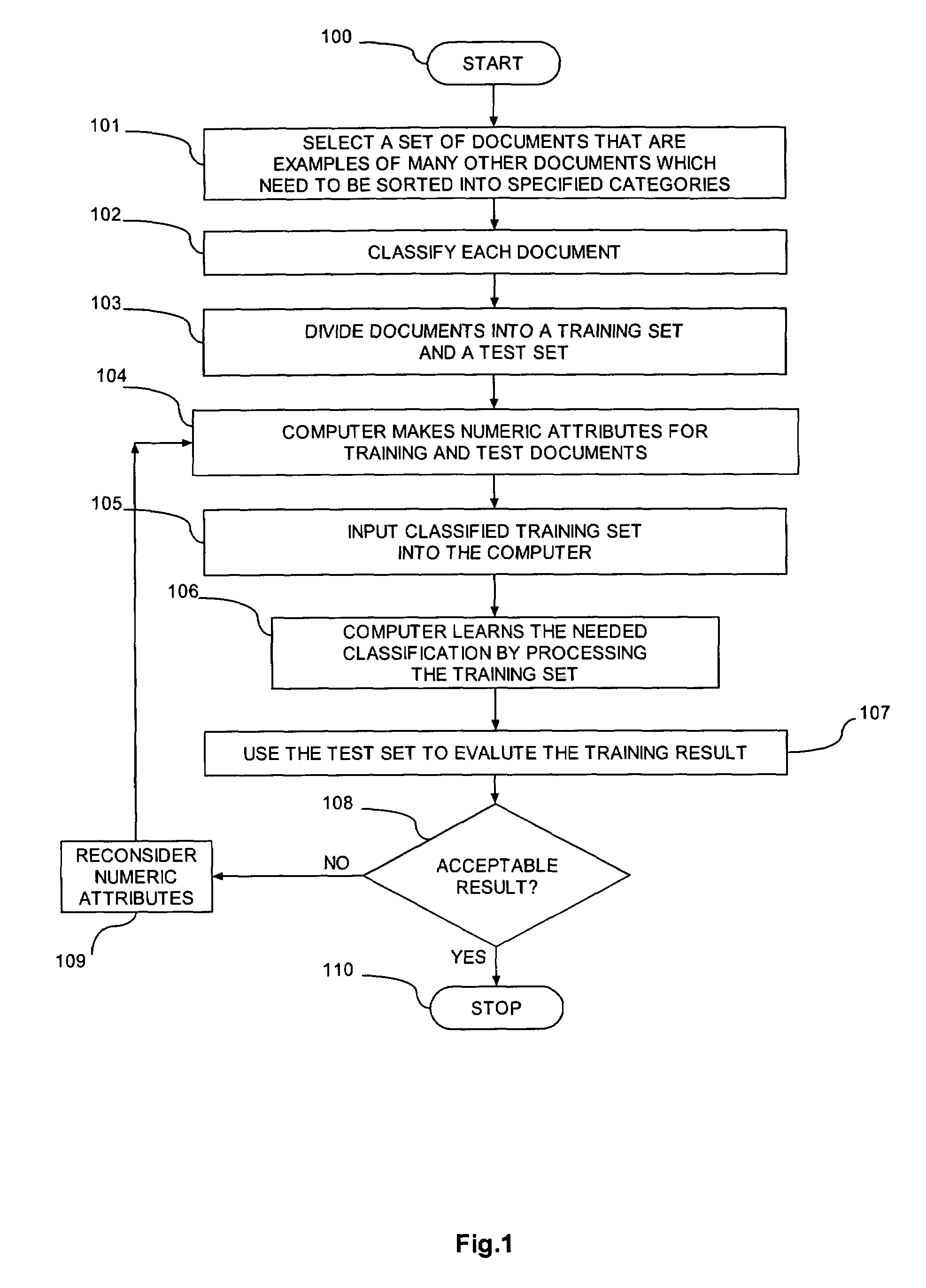

Method and apparatus for efficient training of support vector machines

ActiveUS20060074908A1Increase speedLearning speed of a support vector machine classifierDigital data information retrievalData processing applicationsLine searchSupport vector classifier

The present invention provides a system and method for building fast and efficient support vector classifiers for large data classification problems which is useful for classifying pages from the World Wide Web and other problems with sparse matrices and large numbers of documents. The method takes advantage of the least squares nature of such problems, employs exact line search in its iterative process and makes use of a conjugate gradient method appropriate to the problem. In one embodiment a support vector classifier useful for classifying a plurality of documents, including textual documents, is built by selecting a plurality of training documents, each training document having suitable numeric attributes which are associated with a training document vector, then initializing a classifier weight vector and a classifier intercept for a classifier boundary, the classifier boundary separating at least two document classes, then determining which training document vectors are suitable support vectors, and then re-computing the classifier weight vector and the classifier intercept for the classifier boundary using the suitable support vectors together with an iteratively reindexed least squares method and a conjugate gradient method with a stopping criterion.

Owner:R2 SOLUTIONS

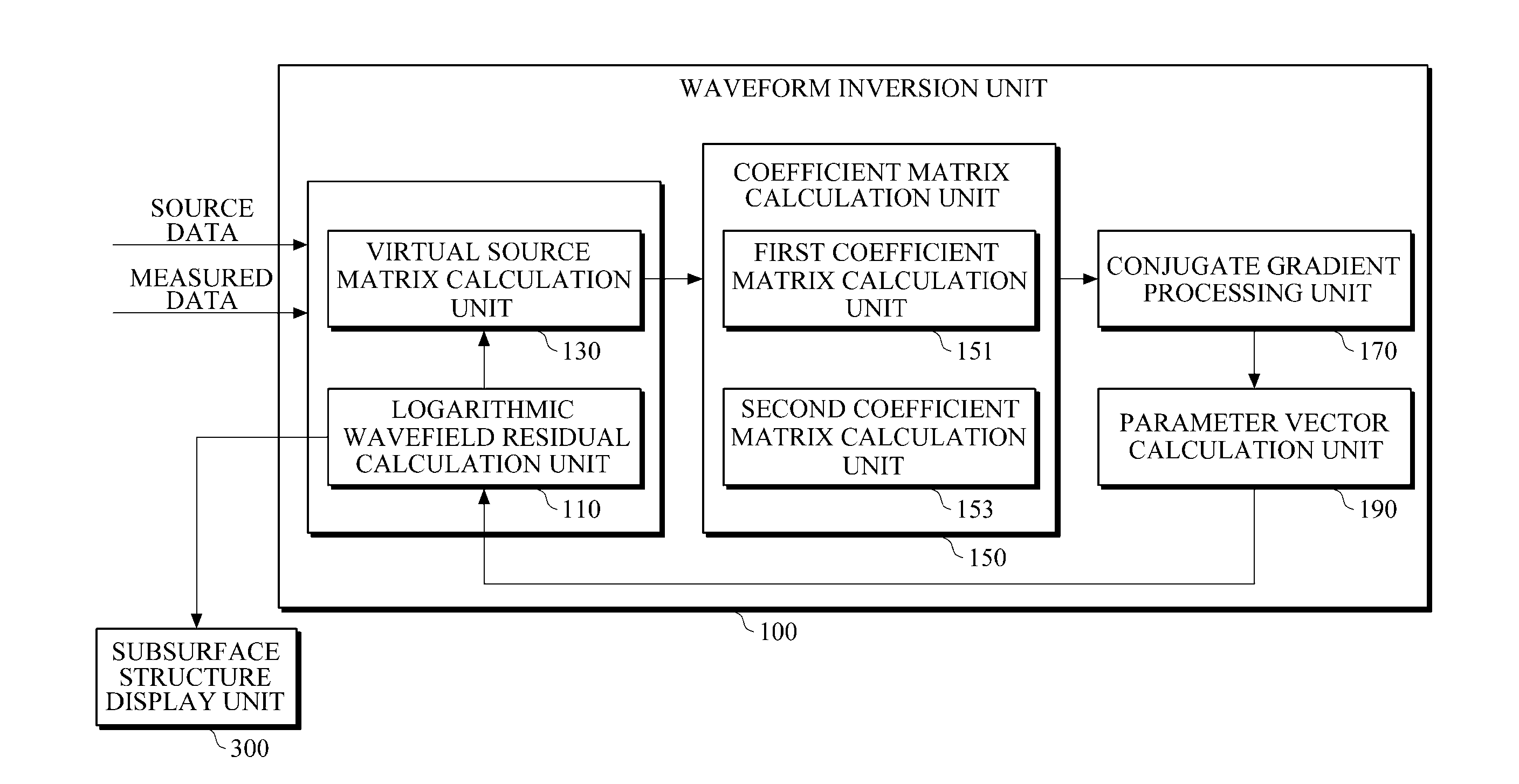

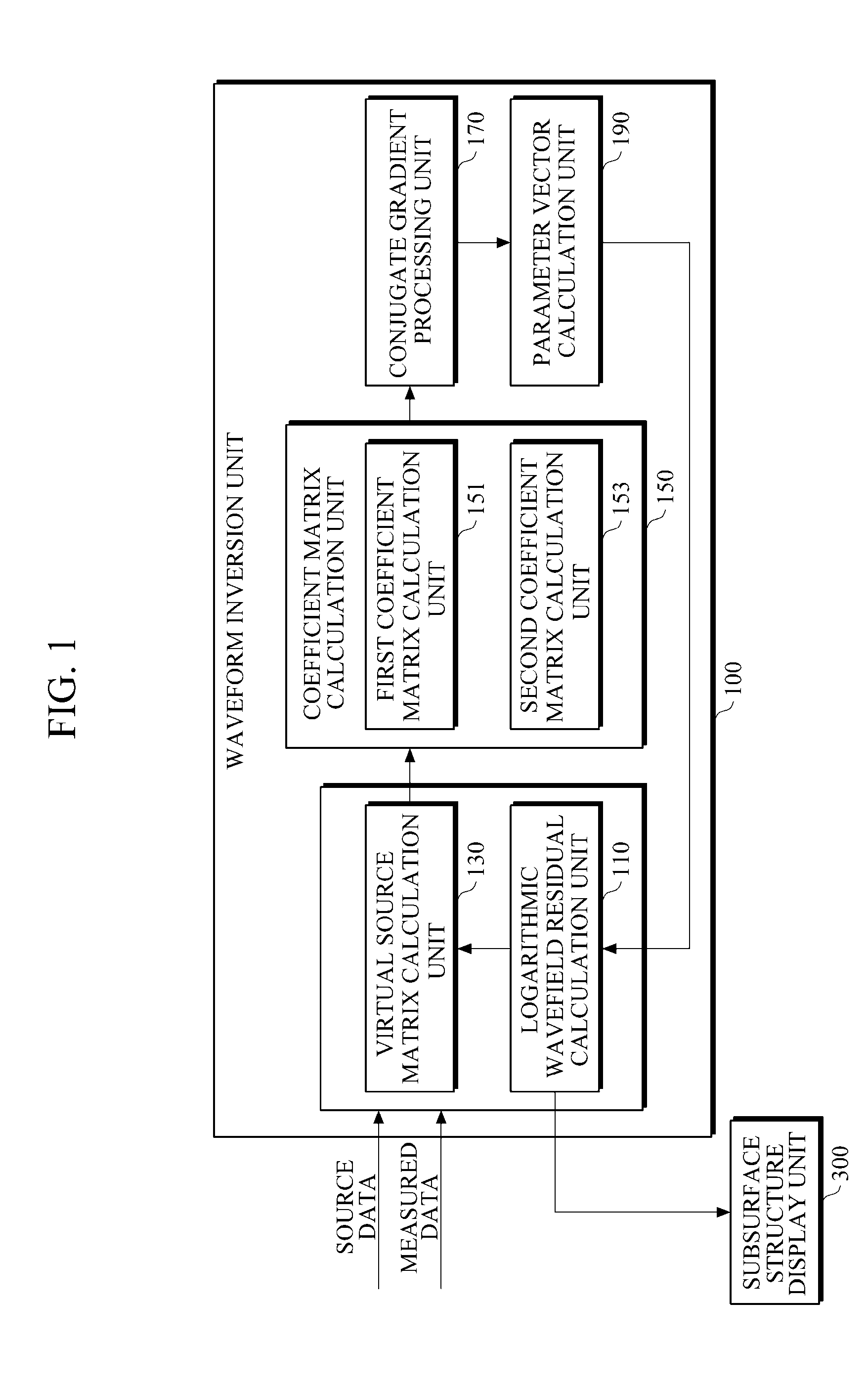

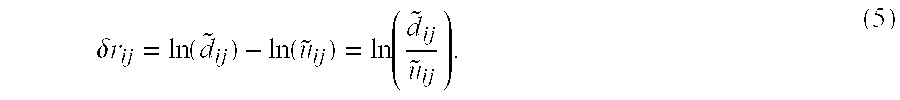

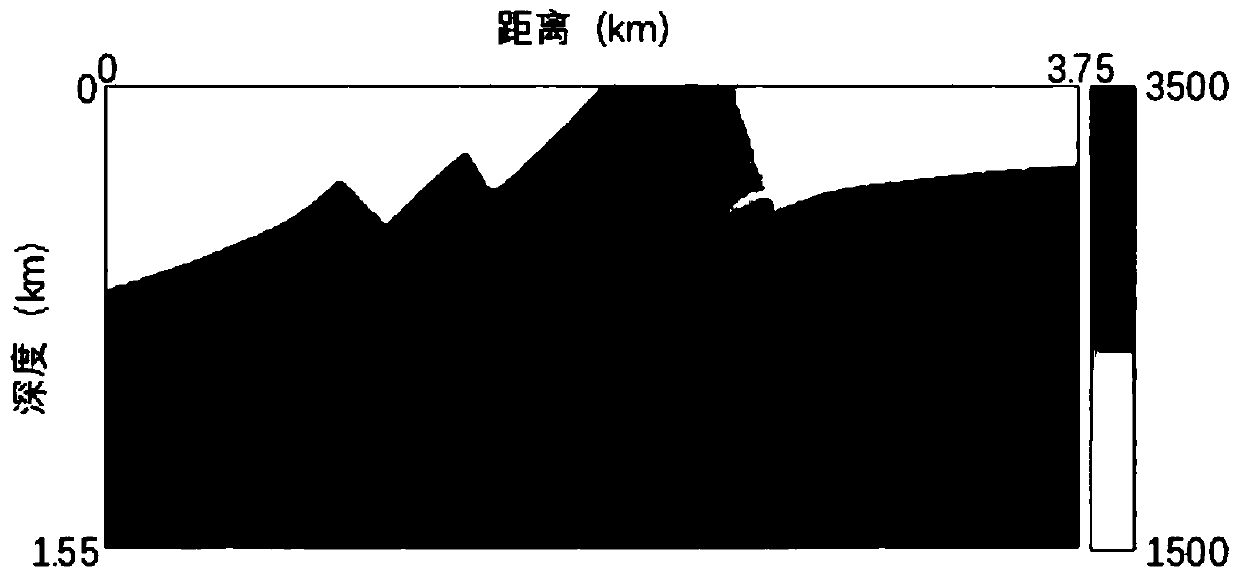

Apparatus and method for seismic imaging using waveform inversion solved by conjugate gradient least squares method

InactiveUS20110267923A1Seismic signal processingSeismology for water-loggingGauss newton methodWave field

Provided is an apparatus for seismic imaging by using waveform inversion in the frequency domain. The seismic imaging apparatus includes: a waveform inversion unit obtaining an equation by applying a Gauss-Newton method to an objective function consisting of residuals of logarithmic wavefields in frequency-domain waveform inversion and then obtaining a parameter vector, which minimizes the objective function, by solving the equation using a conjugate gradient method; and a subsurface structure display unit generating subsurface structure information using the parameter vector obtained by the waveform inversion unit and displaying the generated subsurface structure information.

Owner:SEOUL NAT UNIV R&DB FOUND

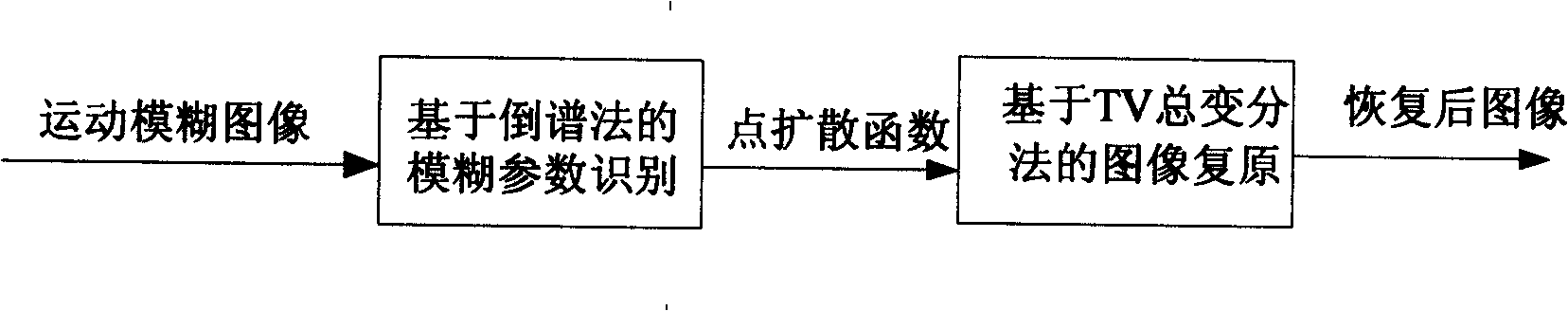

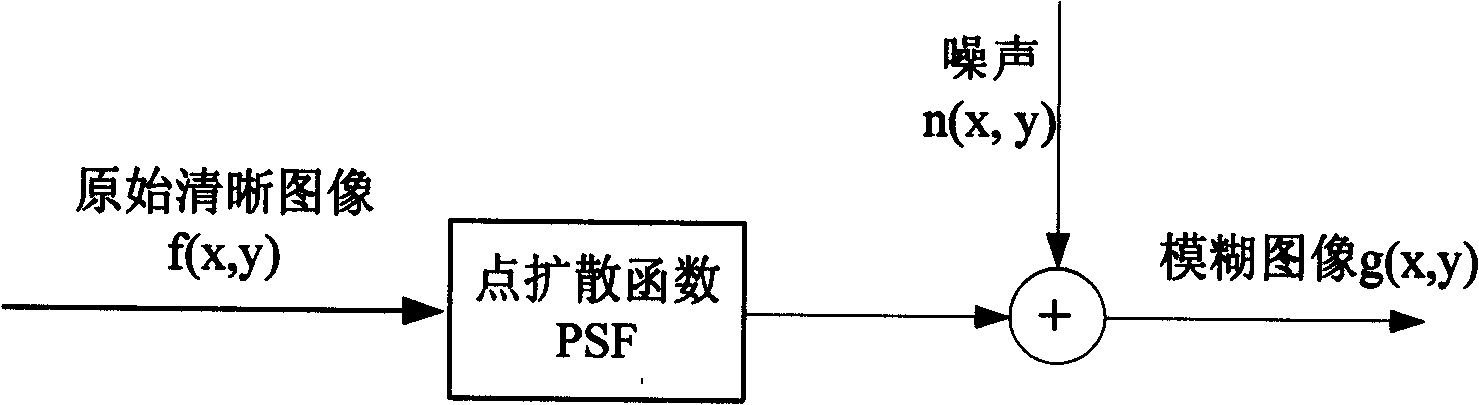

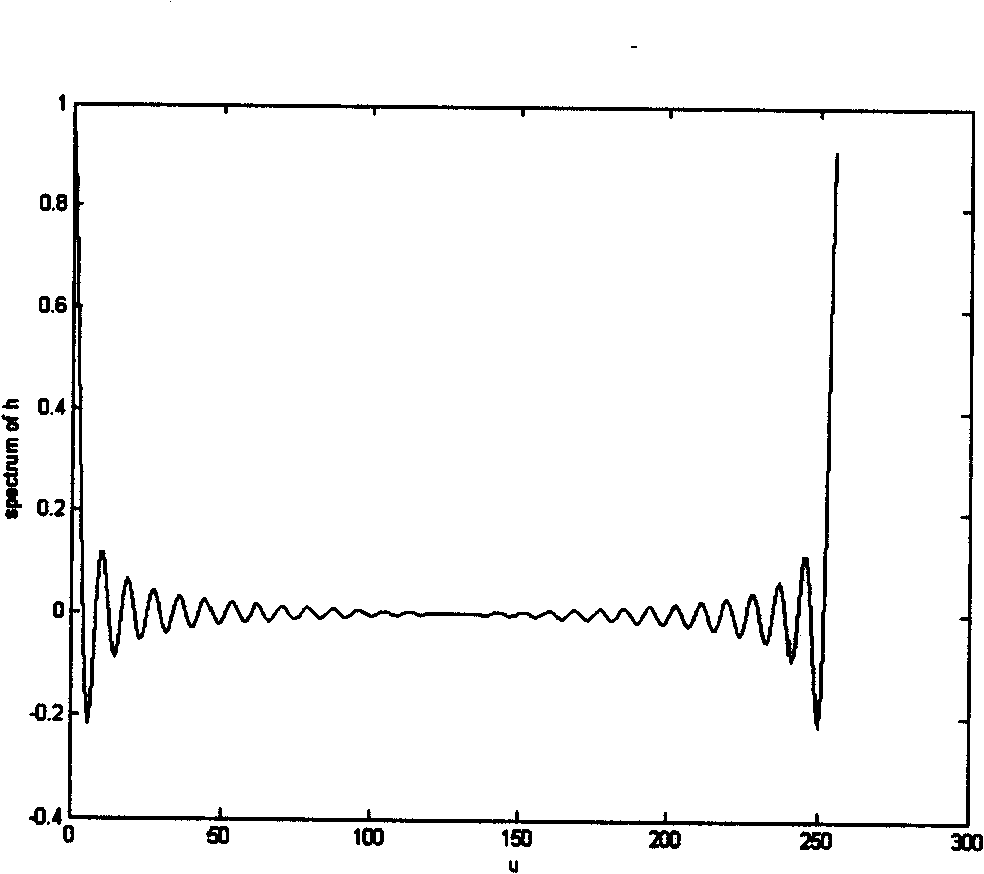

Blind restoration method for moving blurred image

InactiveCN101359398AImprove clarityOvercoming blurry smearing problemsImage enhancementComputer graphics (images)Inner loop

Disclosed is a blind restoration method for the motion blurred image; the steps are as follows: (1) the image is converted through the cepstrum method to figure out the blur extent and the blur direction of the blurred image; (2) the blur extent and the blur direction of the blurred image figured out in step (1), and the total variation (TV) method are adopted to process the restoration towards the blurred image. The method based on the total variation (TV) includes: the fixed-point iteration used as the outer-loop and the conjugate gradient method used as the inner-loop are adopted for loop iteration to obtain the restored image. The blind restoration method has the advantages of strong self-adaptation, strong anti-noise ability and good robustness; the blind restoration method has validity and practicality according to the processing effects of the simulation picture and the photographed picture.

Owner:BEIHANG UNIV

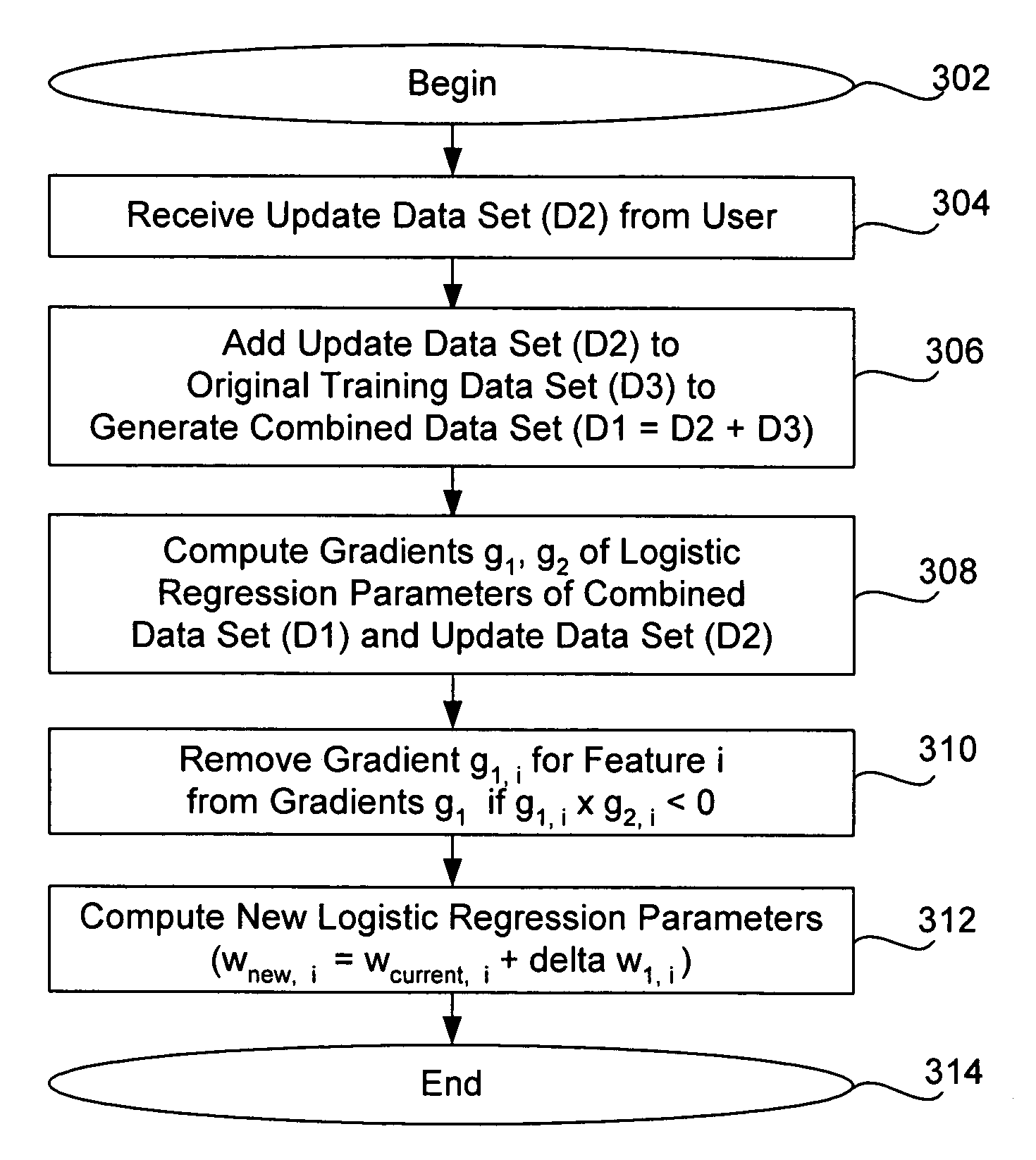

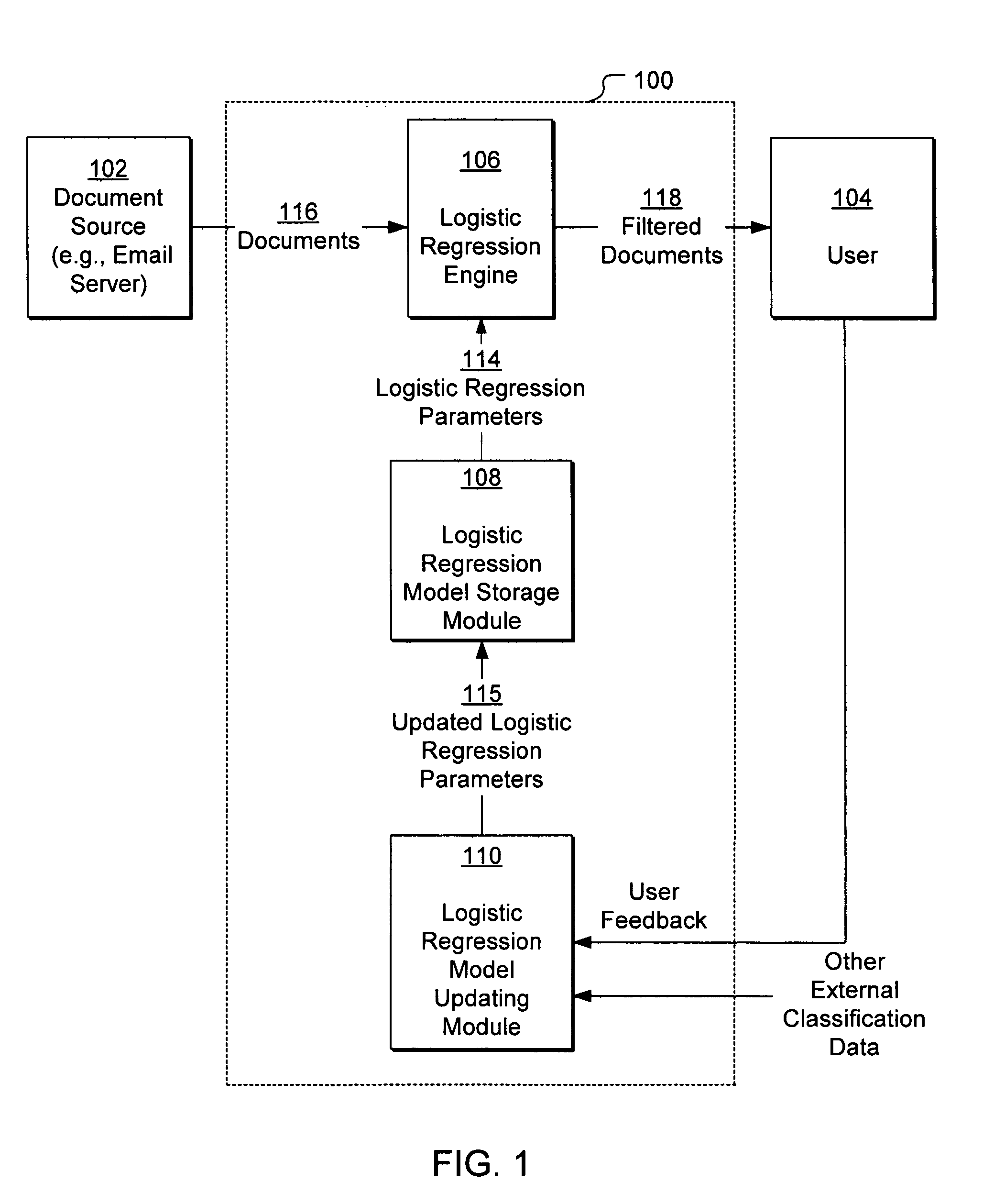

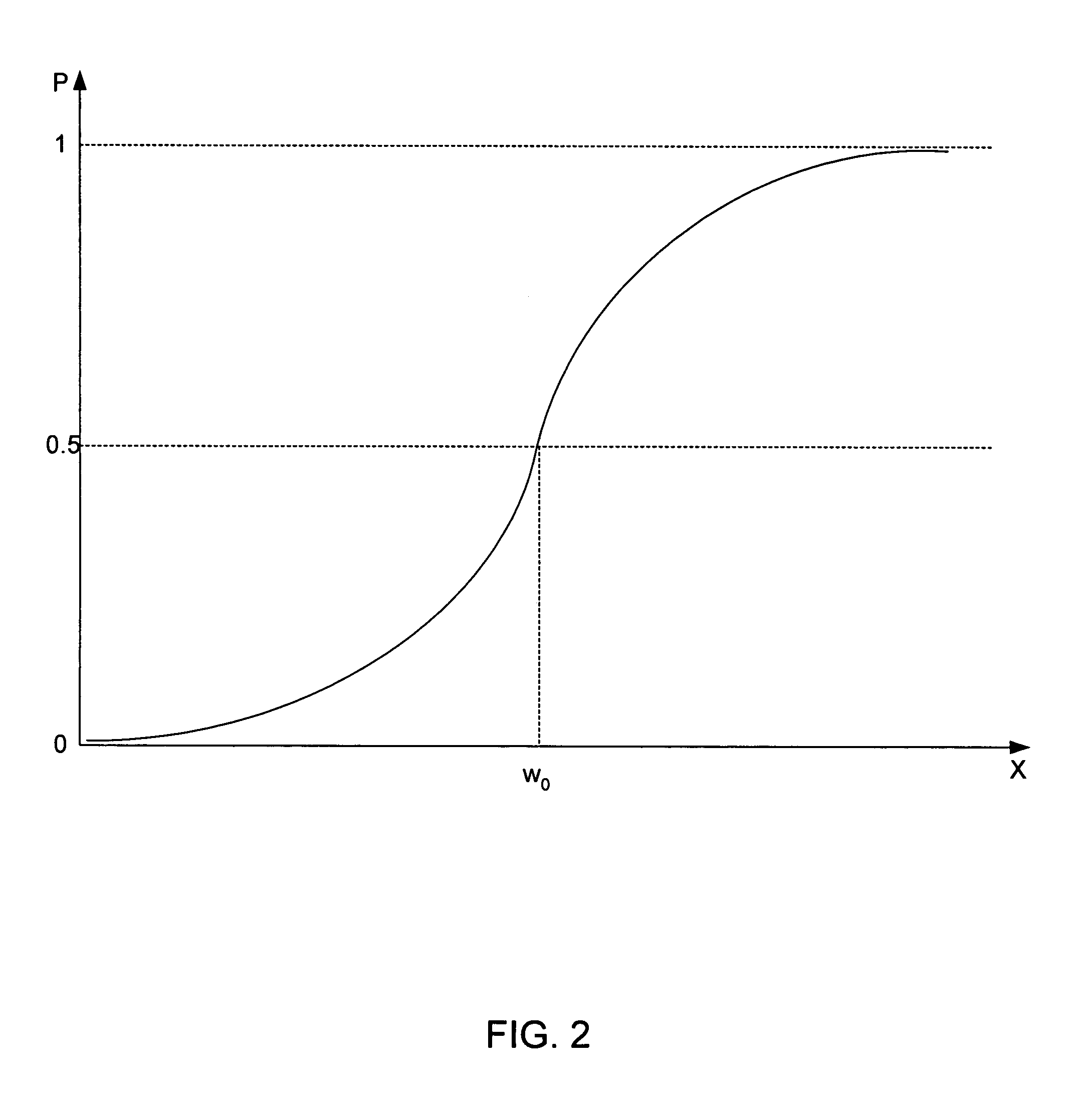

Updating logistic regression models using coherent gradient

ActiveUS7461063B1Avoid performance degradationData processing applicationsDigital data information retrievalOriginal dataFilter system

A document classification system updates the logistic regression parameters of the logistic regression algorithm used to classify the documents, using a coherent gradient method based upon the coherency between the update data regarding the classifications of the documents and the combined data including both the update data and the original data used to generate the original logistic regression parameters. The classification system can be applied to an email filtering system for filtering spam email.

Owner:PROOFPOINT INC

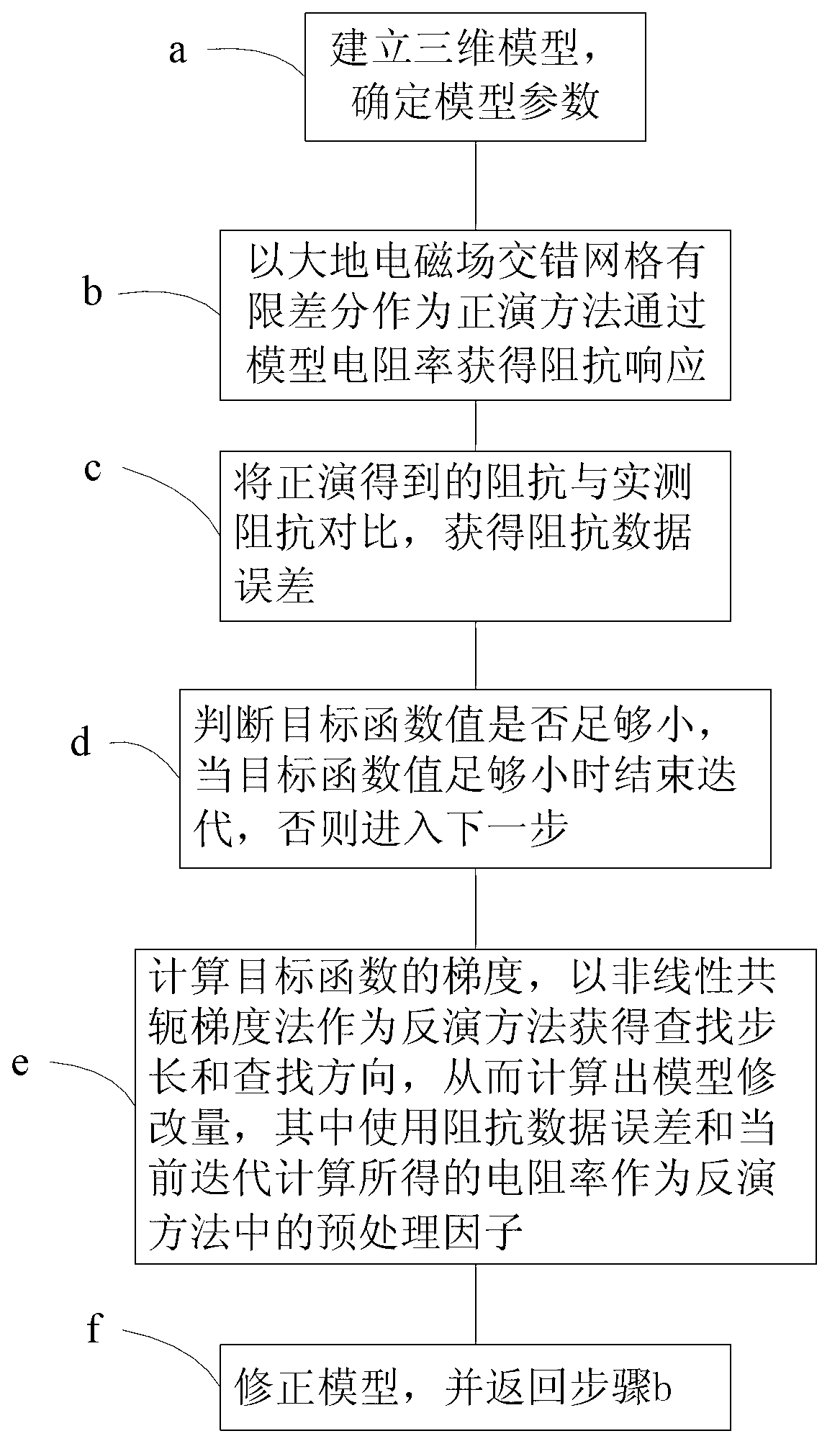

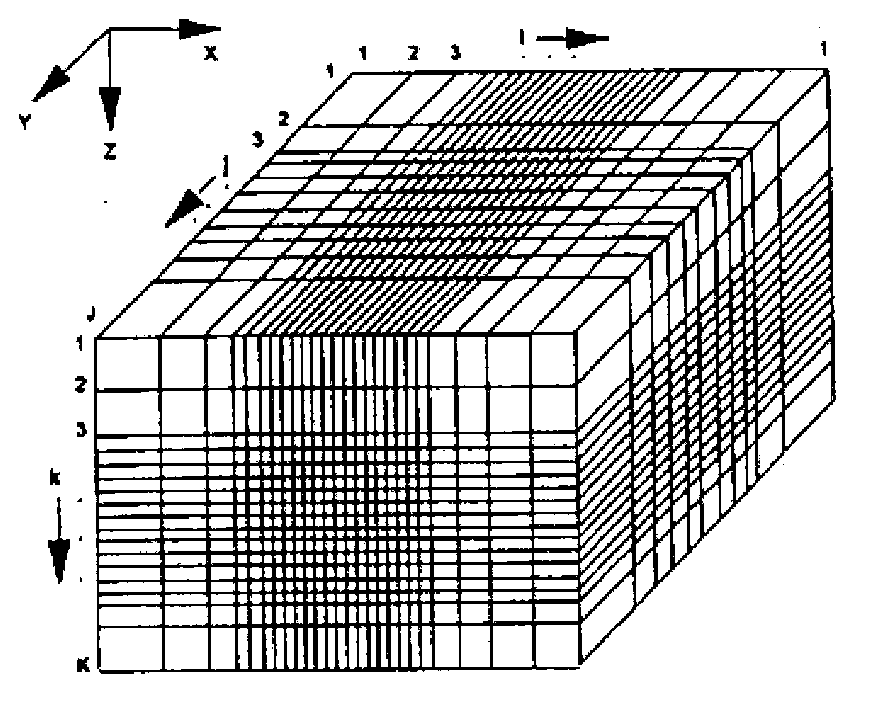

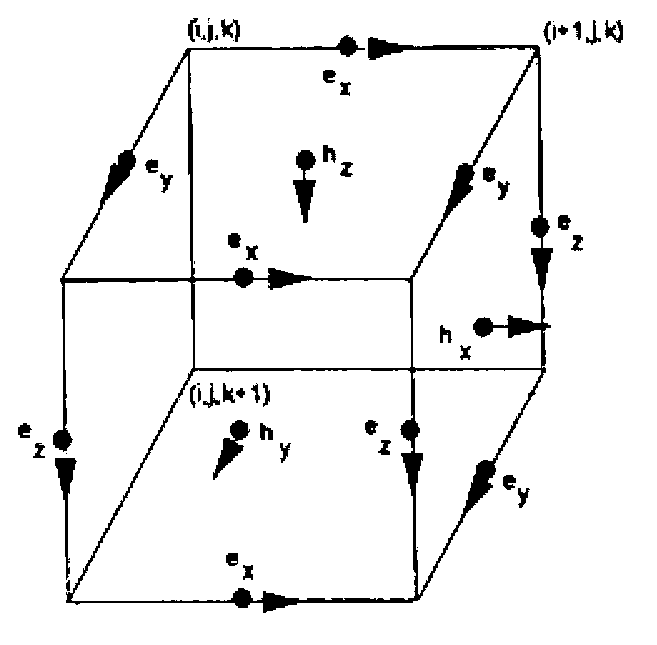

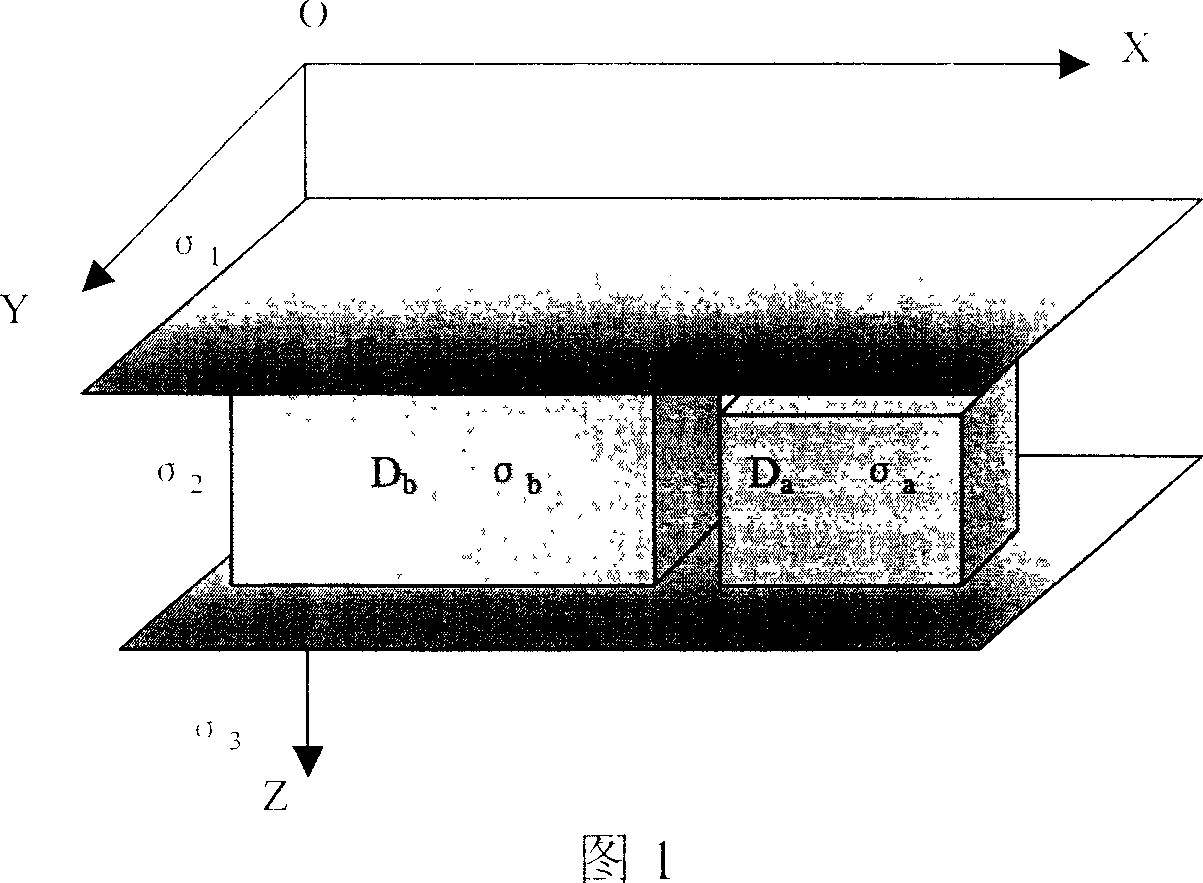

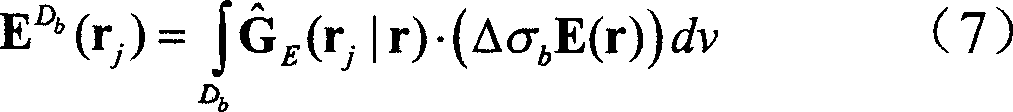

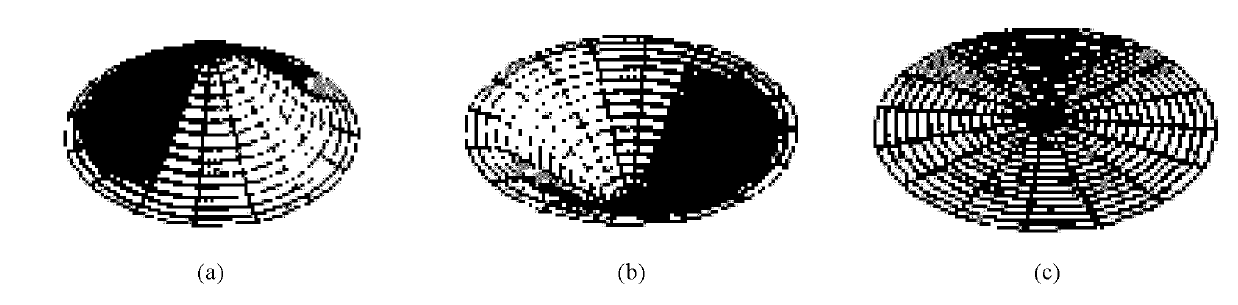

Non-linear conjugate gradient three-dimensional inversion method of magnetotelluric field

ActiveCN102798898AReduce 8 quasi-forward calculationsImprove computing efficiencyElectric/magnetic detectionAcoustic wave reradiationModel parametersData error

The invention discloses a non-linear conjugate gradient three-dimensional inversion method of a magnetotelluric field, which comprises the following steps of: a, establishing a three-dimensional model, and determining model parameters; b, acquiring impedance response through the model resistivity by using the staggered-grid finite difference of the magnetotelluric field as a forward modeling method; c, comparing the impedance which is acquired by forward modeling with an actually measured impedance to acquire an impedance data deviation; d, judging whether a target function value is enough small or not, finishing iteration when the target function value is small enough, otherwise entering the next step; e, calculating the gradient of a target function, and acquiring a search step-length and a search direction by using a non-linear conjugate gradient method as an inversion method so as to calculate a model modifier, wherein the resistivity calculated by using the impedance data error and current iteration is used as a preprocessing factor in the inversion method; and f, modifying the model, and returning to the step b. The non-linear conjugate gradient three-dimensional inversion method of the magnetotelluric field has the characteristics of high efficiency and high accuracy.

Owner:INST OF MINERAL RESOURCES CHINESE ACAD OF GEOLOGICAL SCI

3D electromagnetic fast inversion method of minimized target

ActiveCN101004454AInversion target is smallFast 3D InversionElectric/magnetic detection for well-loggingAcoustic wave reradiationPhase responseData treatment

A 3-D electromagnetic fast inversing method of object minimization includes confirming known object region according to known geologic data, setting up background conductivity combination according to known conductivity parameter and 3-D interpolation, calculating background field of said combination, inversing unknown region as per requirement of production, obtaining general field, carrying out 3-D interpolation on phase curve and actually measured conductivity curve, inversing frequency and fitting inversed frequency to obtain underground conductivity set of object.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

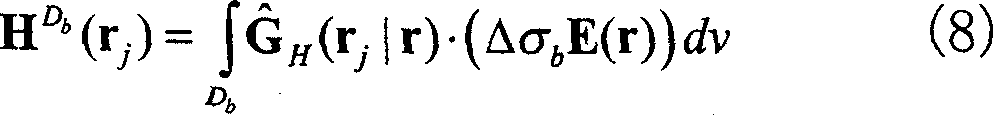

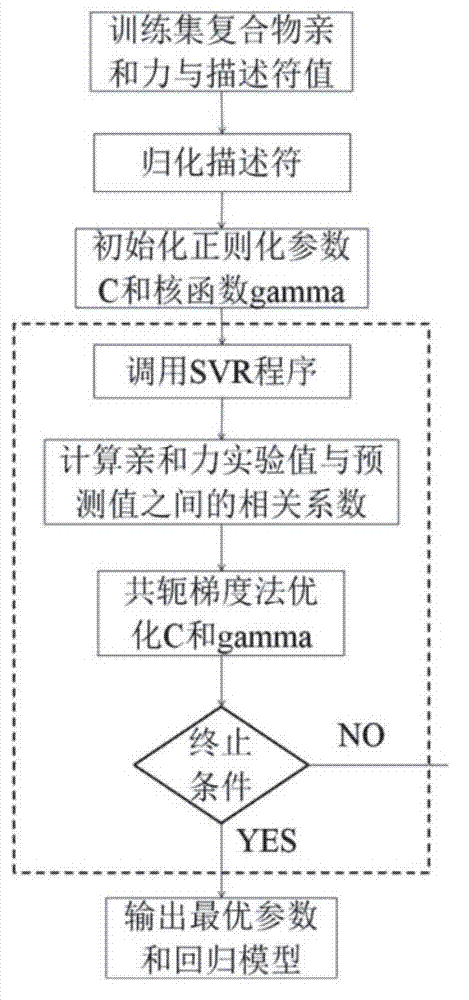

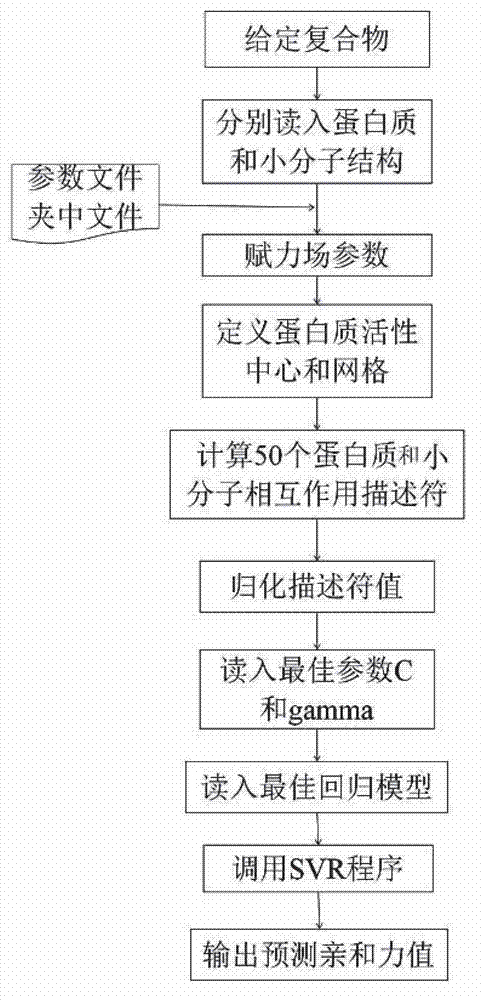

Protein-ligand affinity predicting method based on molecule descriptors

InactiveCN102930181AReduce dependenceImprove predictive abilitySpecial data processing applicationsCrystal structureConjugate gradient method

Disclosed is a protein-ligand affinity predicting method based on molecule descriptors. The protein-ligand affinity is reflected through construction of perfect and systematic molecule descriptors, and the relation between the descriptors and the affinity is constructed through a supporting vector regression (SVR) mode. The method includes the steps of training set preparation: preparing a large amount of data containing the crystal structure and the affinity of a protein-ligand complex; construction and calculation of the molecule descriptors: constructing 50 kinds of molecule descriptors which belong to nine categories, and calculating concrete values of all the complex descriptors in the training set; regression model construction: fitting the relation between the descriptors and the affinity through the SVR mode, and introducing a conjugate gradient method to optimize a penalty factor C and a kernel function parameter; and novel scoring function building which is used for predicting the affinity of the complex. The method has the advantages of being high in prediction capacity, small in target dependence, high in homolog sensitivity and the like.

Owner:SICHUAN UNIV

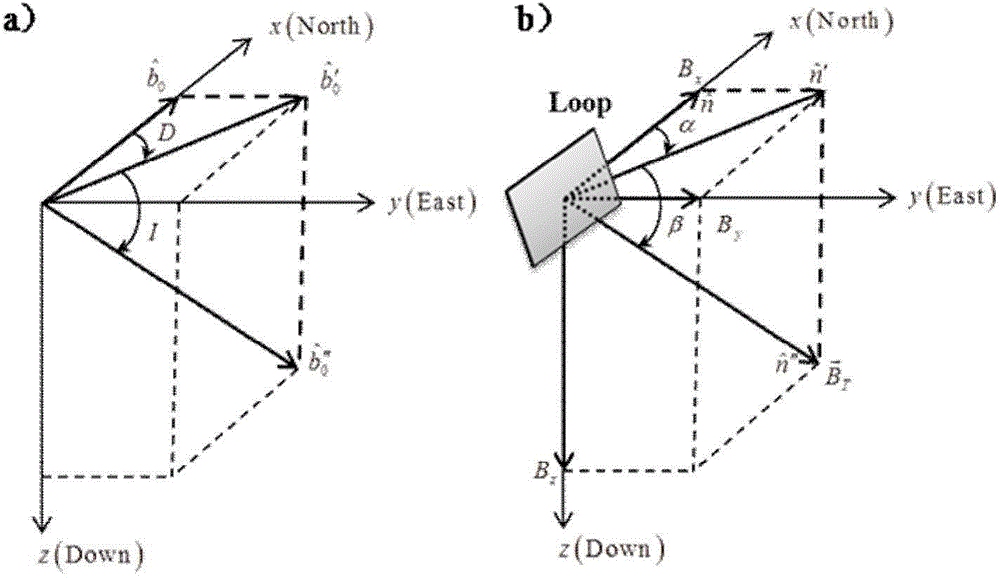

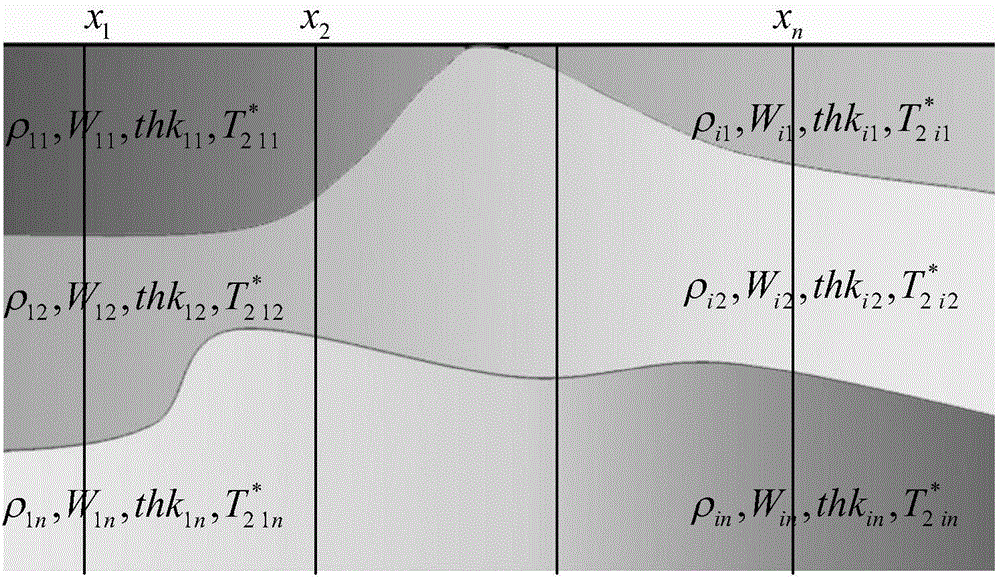

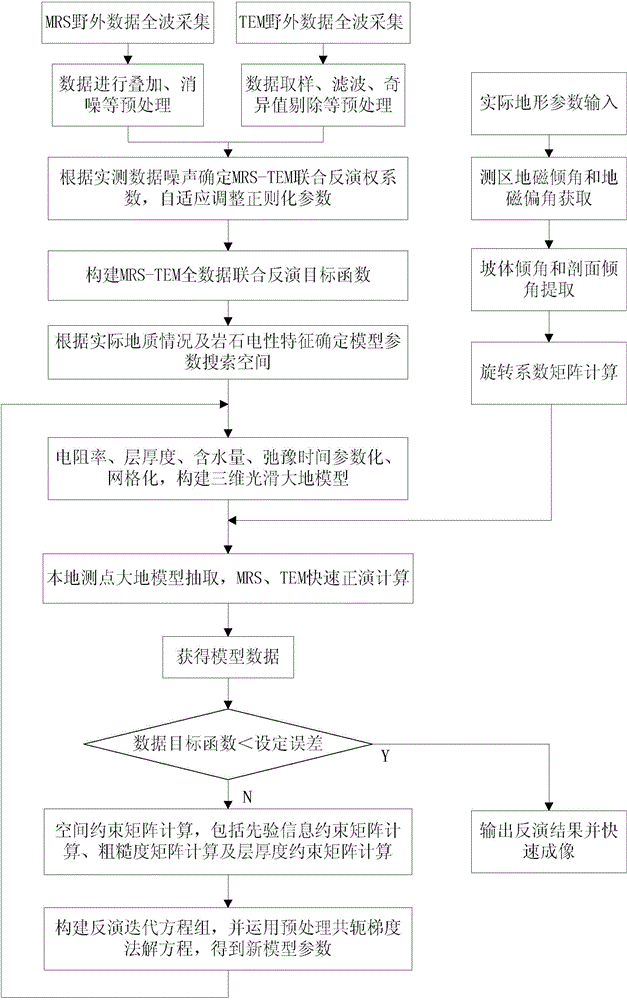

Magnetic resonance and transient electromagnetic spatial constraint joint inversion method

ActiveCN104537714AImplement smooth continuous constraintsSolve the problem of non-uniqueness3D modellingLayer thicknessConjugate gradient method

The invention relates to a high-precision magnetic resonance and transient electromagnetic spatial constraint joint inversion method. The joint inversion method is based on a forward modeling method combining a continued fraction expansion numerical integration equivalent transformation method and a digital filtering method. The magnetic field calculation precision and speed are both taken into account, an original model and a simplest model are provided, a rotary coefficient matrix equation is designed, and exciting field distribution is simulated and detected when different slope dip angles appear and profile angles change. According to a forward modeling result obtained under the condition of changed dip angle parameters, the forward modeling result is combined with a hierarchical full collection data inversion method, a joint inversion objective function, an iterative equation and a three-dimensional ground model are constructed, a prior information constraint matrix, a roughness matrix, a layer thickness constraint matrix and other spatial constraint matrices are introduced to construct an inversion iterative equation set, based on a large scale matrix of a preconditioning conjugate gradient method, smooth and continuous constraint for the specific resistance, the layer thickness, the water content and the relaxation time is achieved, the problem of inversion non-uniqueness is solved, and the problem that optimization and calculation of a large-scale matrix for spatial constraint inversion involves mass data is solved.

Owner:JILIN UNIV

Method for increasing calculation speed of SMP cluster system through MPI and OpenMP in hybrid parallel mode

ActiveCN104461467AReduce synchronizationAvoid interactionConcurrent instruction executionCalculation errorInitialization vector

The invention discloses a method for increasing the calculation speed of an SMP cluster system through an MPI and an OpenMP in a hybrid parallel mode. The method comprises the steps that the number of MPI processes which can be called and the number of OpenMP threads are determined according to the number of calculation nodes and the number of usable CPU kernels in the nodes; an existing sub sparse matrix, a sub initial vector, a block vector and the maximum calculation tolerance are read in each process; a multi-thread compiling instruction is started for each process; circulation calculation of a precondition conjugate gradient method is conducted on all the processes, and the number of OpenMP barriers in circulation calculation is only three; if calculation errors are smaller than an allowable value, circulation is over, and otherwise circulation continues; calculation results of all the processes are reduced, and solutions of questions are output; when parallel calculation is conducted, firstly, MPI processes are started, multi-process decomposition is conducted on the questions, parallel among the nodes is started, each MPI process is allocated to one calculation node, and information is exchanged between the processes trough message transmission; then, in each MPI process, OpenMP guidance instructions are used for establishing one set of threads, and the threads are allocated to different processors of the calculation nodes to conduct parallel execution.

Owner:INST OF SOFTWARE APPL TECH GUANGZHOU & CHINESE ACAD OF SCI

Composite reconstruction method for self-adaptation quantitative magnetisability distribution diagram based on structural feature

InactiveCN104267361AAccurate calculationSuppression of Prior Weighting ErrorsMeasurements using NMR imaging systemsMagnetic susceptibilityReconstruction method

The invention provides a composite reconstruction method for a self-adaptation quantitative magnetisability distribution diagram based on the structural feature, and relates to quantitative magnetisability imaging. According to the priori magnetisability distribution diagram base reconstruction based on the amplitude image structural feature, a reconstruction model comprises a fidelity item with a compression perception characteristic and an amplitude priori regularization bound item with a sparse feature, a region of interest is added to extract a binary weighting matrix from an amplitude image, and binary weighting is conducted on original magnetisability distribution; according to magnetisability distribution diagram composite reconstruction based on the magnetisability distribution structural feature, the reconstruction model comprises a least square fidelity item, a structural feature regularization bound item, acquired by base reconstruction, of a magnetisability distribution diagram structure, and a smooth item used for improving a reconstruction magnetisability distribution effect, the magnetisability structural feature is defined as the ladder degree information of 3D image data in three directions in a priori mode; for a l1 norm optimization problem, an iterative threshold value method is used for processing; then, based on the convex function character of a l2 norm, a conjugate gradient method is used for solving.

Owner:XIAMEN UNIV

Fixed-point conjugate gradient digital pre-distortion (DPD) adaptation

A predistortion method and apparatus are provided which use a DPD actuator (225) to apply a memory polynomial formed with first DPD coefficients to a first input signal x[n], thereby generating a first pre-distorted input signal y[n] which is provided to the non-linear electronic device (253) to produce the output signal, where the memory polynomial may be adaptively modified with a digital predistortion adapter (224) which computes second DPD coefficients u[n] with an iterative fixed-point conjugate gradient method which uses N received digital samples of the first pre-distorted input signal y[n] and a feedback signal z[n] captured from the output signal to process a set of conjugate gradient parameters (u, b, v, r, ω, α, β) at each predetermined interval, thereby updating the first DPD coefficients with the second DPD coefficients u[n] generate a second pre-distorted input signal which is provided to the non-linear electronic device.

Owner:NXP USA INC

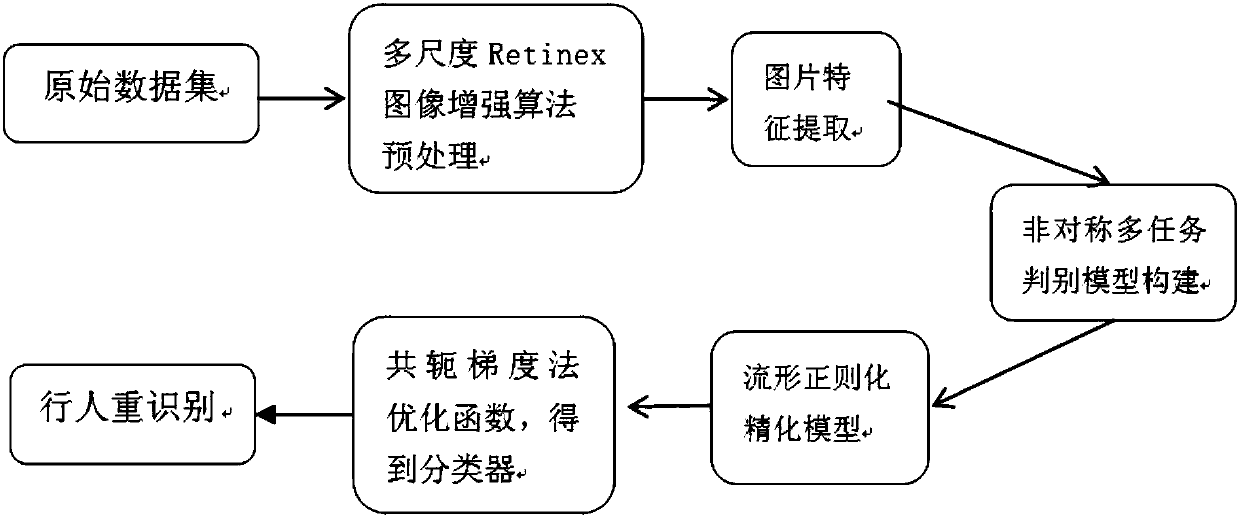

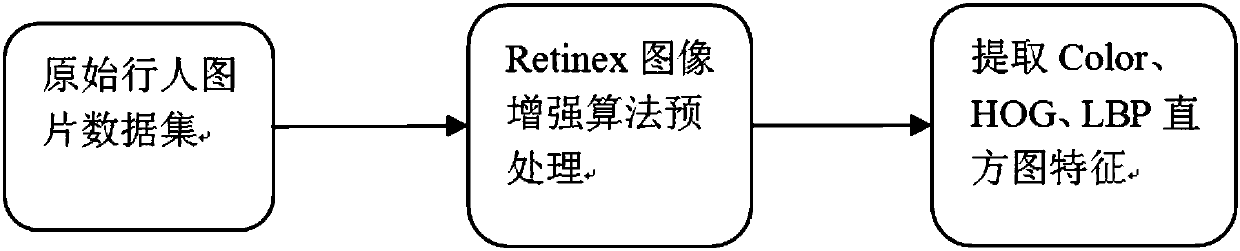

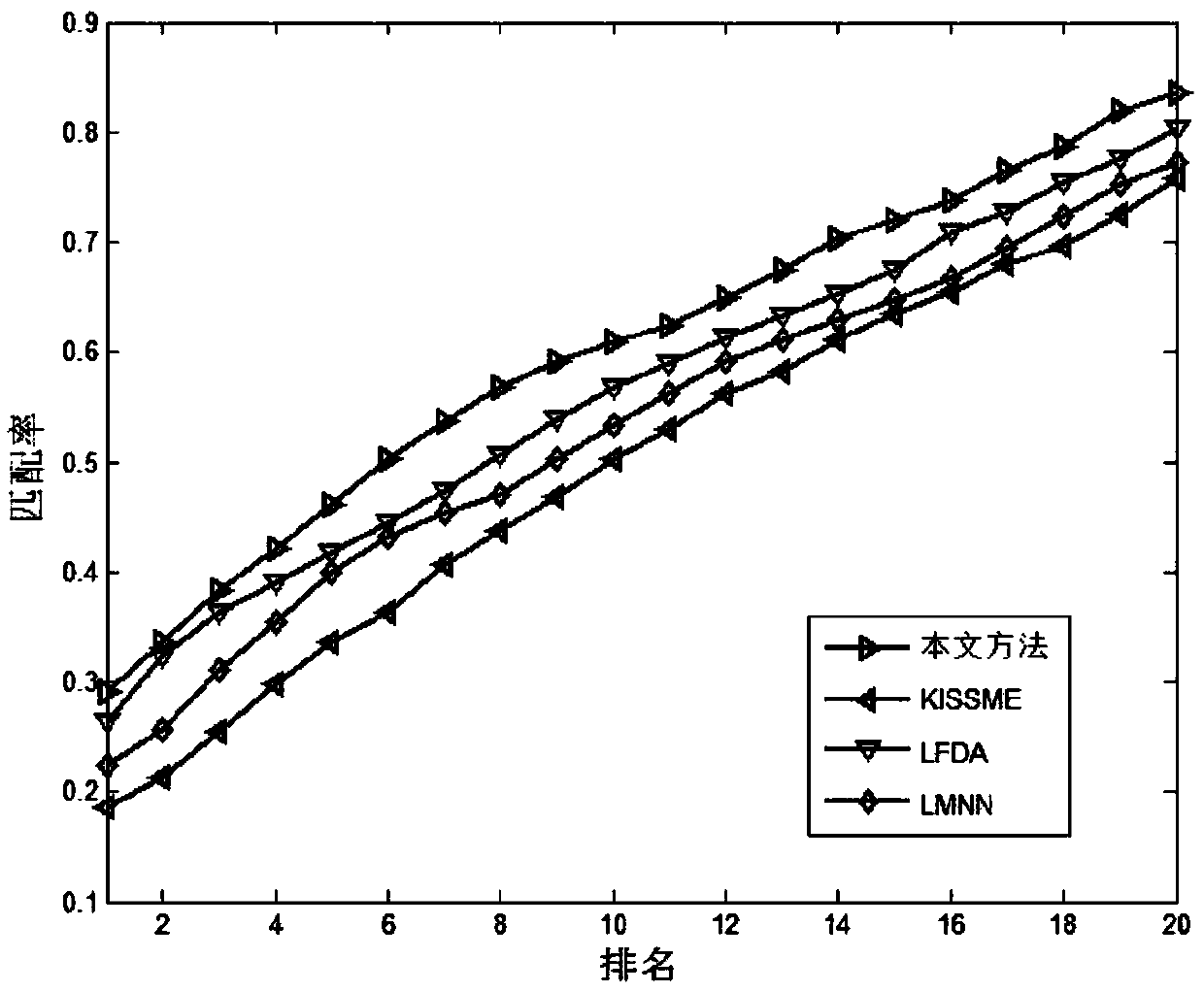

Pedestrian re-recognition method based on migration learning

InactiveCN107832711AReduce overfittingAlleviate the imbalance problemCharacter and pattern recognitionColor imageData set

The invention discloses a pedestrian re-recognition method based on migration learning. The pedestrian re-recognition method includes the steps of 1) preprocessing pictures in a data set by using a multi-scale Retinex color image enhancement algorithm to remove the influence caused by illumination; 2) concentrically extracting relevant features of pedestrians from the preprocessed data set; 3) establishing an asymmetric multi-task discriminant model; 4) refining the model by using a flow-shaped structure without label data; 5 ) optimizing the objective function by using a conjugation gradientmethod to obtain a final classifier; and 6 ) testing the pedestrian re-recognition rate on the classifier based on the pedestrian re-recognition standard database. Few label data and the label-free data are reasonably applied, and the model obtained through training can well improve the pedestrian re-recognition rate.

Owner:CHANGZHOU UNIV

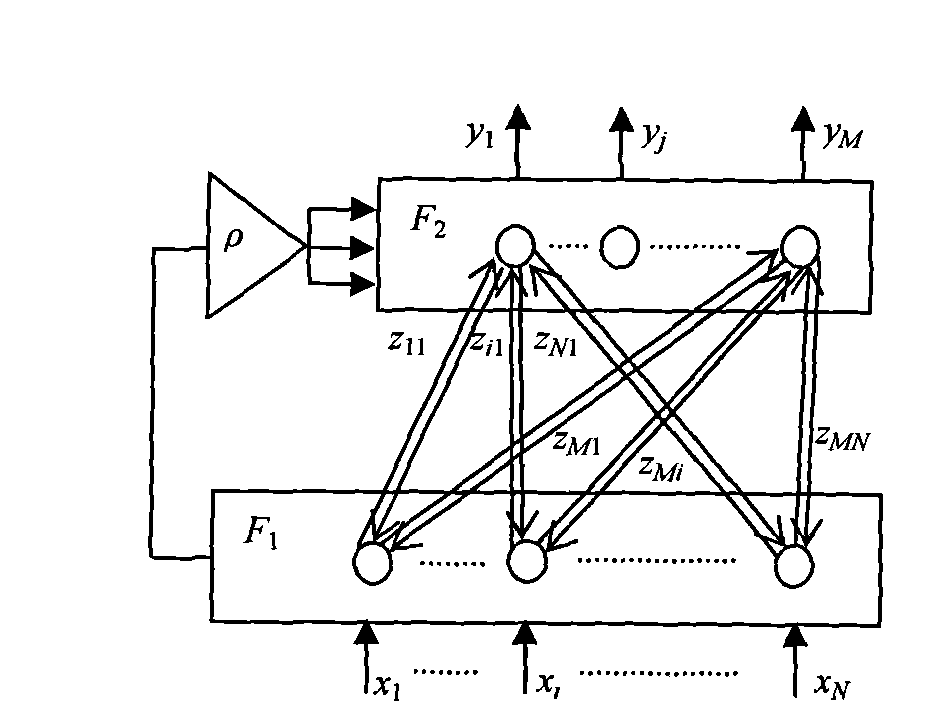

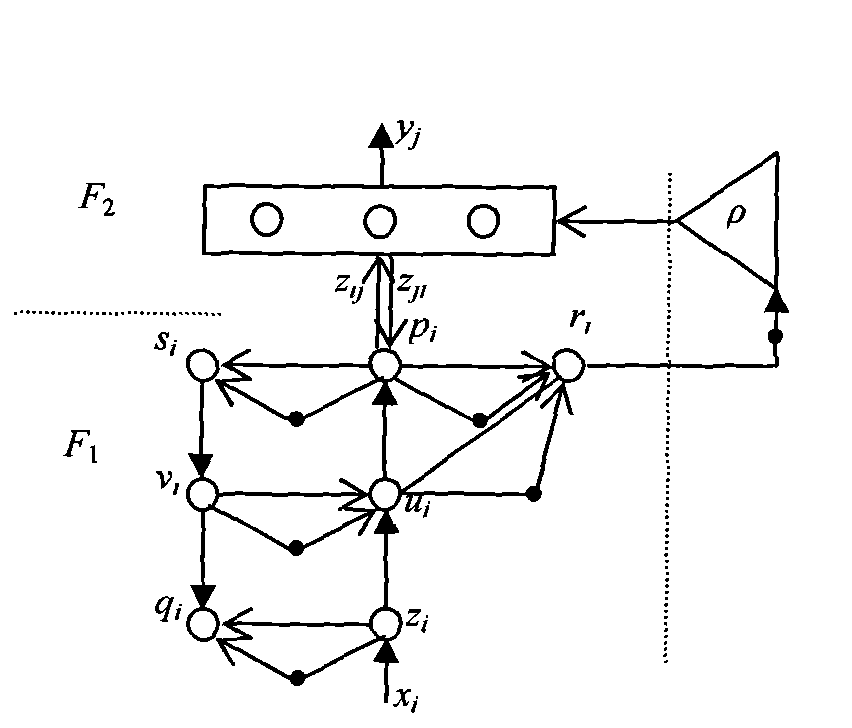

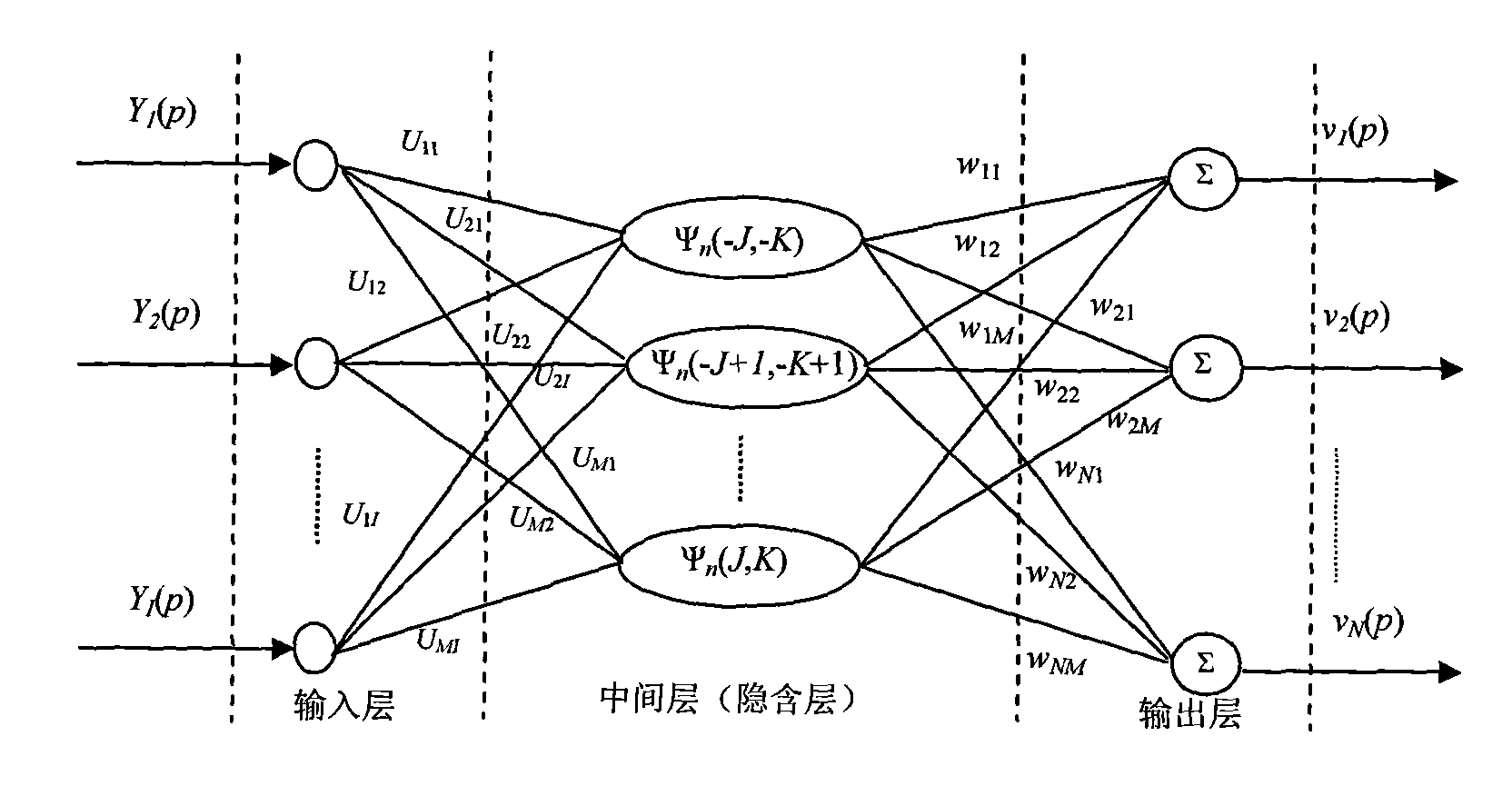

Classification and identification method for communication signal modulating mode based on ART2A-DWNN

InactiveCN101667252ASimple calculationAccurate identificationModulated-carrier systemsCharacter and pattern recognitionTime domainNerve network

The invention relates to a classification and identification method for a communication signal modulating mode based on ART2A-DWNN, belonging to the field of classification and identification of communication signal modulating modes and solving the problem that single neural network has long period and low accuracy for classifying and identifying communication signals. In the method, an ART2A-E algorithm based on an ART2A network is taken as a first layer of a combined neural network, and similar modes is roughly classified by selecting relatively smaller vigilance parameters; a DWNN is directly connected with the output layer with the corresponding type of the ART2A network, Morlet mother wavelet Phi(x) with higher resolution in frequency domain and time domain are adopted, learning is carried out by utilizing error back-propagation algorithm, a synaptic weight can be modified with a conjugate gradient method till output is within the error range, and the number of modes in each typeis reduced after rough ART2-E classification, so that the DWNN can quickly converge. The invention is used for classification and identification of communication signals.

Owner:HARBIN INST OF TECH

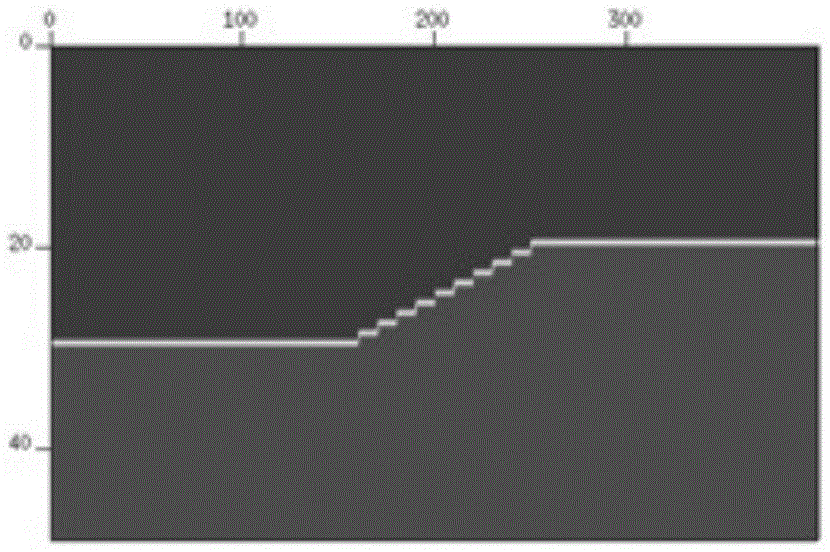

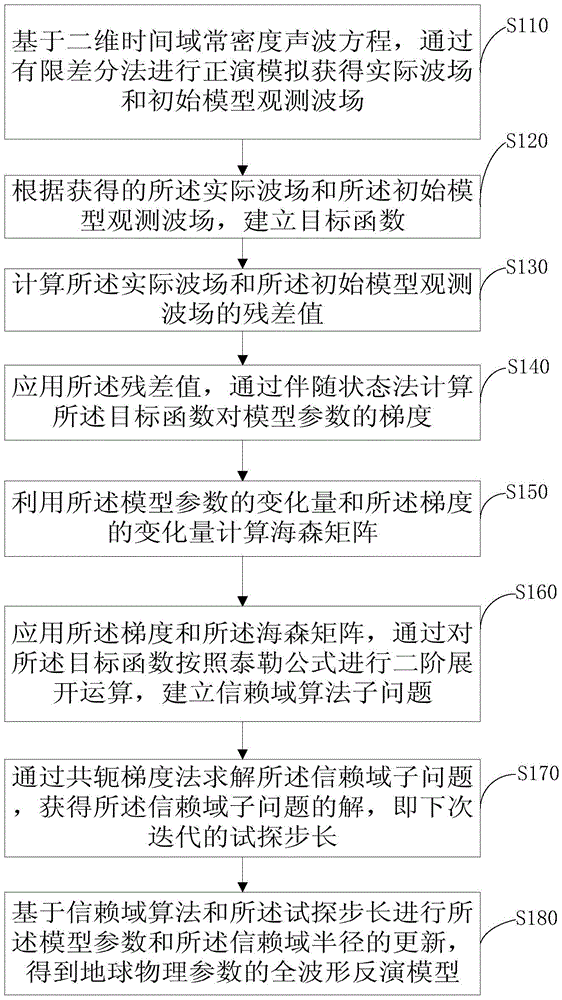

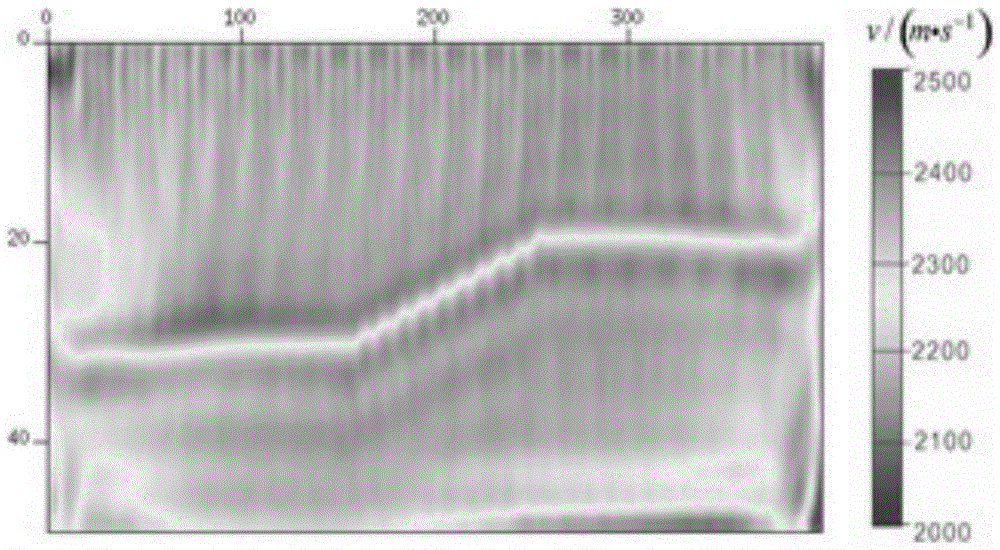

Method and device for establishing full-waveform inversion model for geophysics parameters

InactiveCN105549079AImprove inversion accuracyImprove efficiencySeismic signal processingAdjoint state methodWave field

The invention provides a method and device for establishing a full-waveform inversion model for geophysics parameters. The method comprises following steps: residual values of real wave-fields and initial model observation wave-fields are calculated; by use of the residual values, gradients of an objective function to model parameters are calculated through an adjoint state method; A Hessian matrix is calculated by use of variations of the model parameters and variations of the gradients By use of the gradients and the Hessian matrix, trust region sub-problems are established through performing second-order expansion calculation to the objective function according to Taylor's formula; the trust region sub-problems are solved through a conjugate gradient method to obtain solutions, namely the probe step length of the next iteration, of the trust region sub-problems; updates of the model parameters and trust region radii are performed on the basis of the trust region algorithm to obtain the full-waveform inversion model of geophysics parameters. By use of the method and device, a high fidelity velocity model is obtained.

Owner:CHINA UNIV OF MINING & TECH (BEIJING)

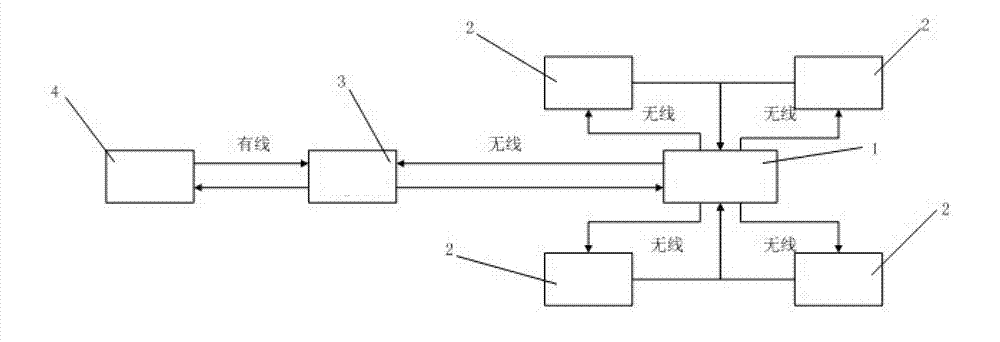

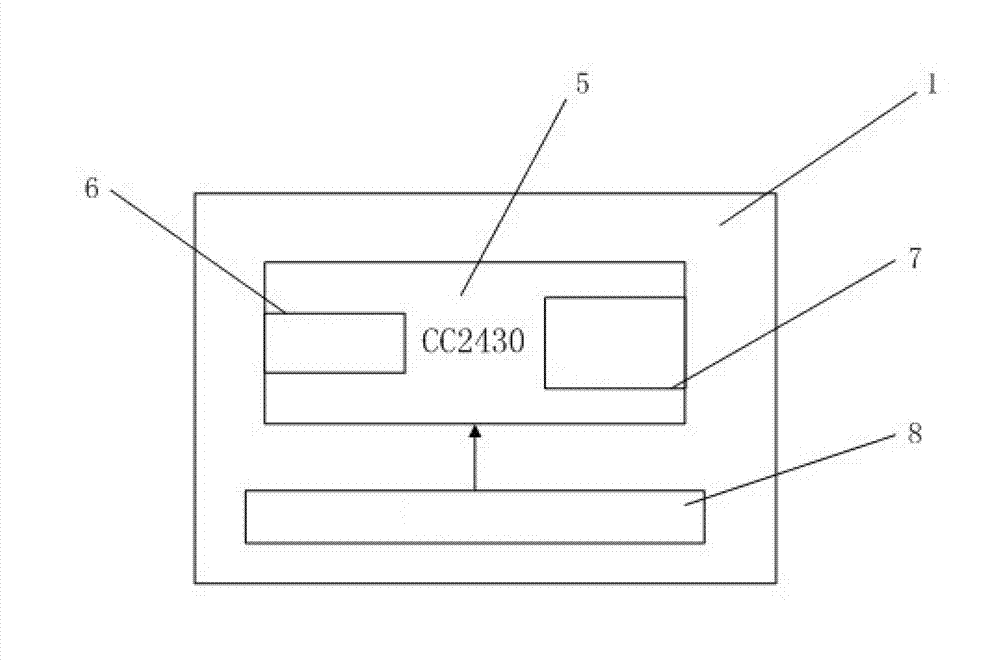

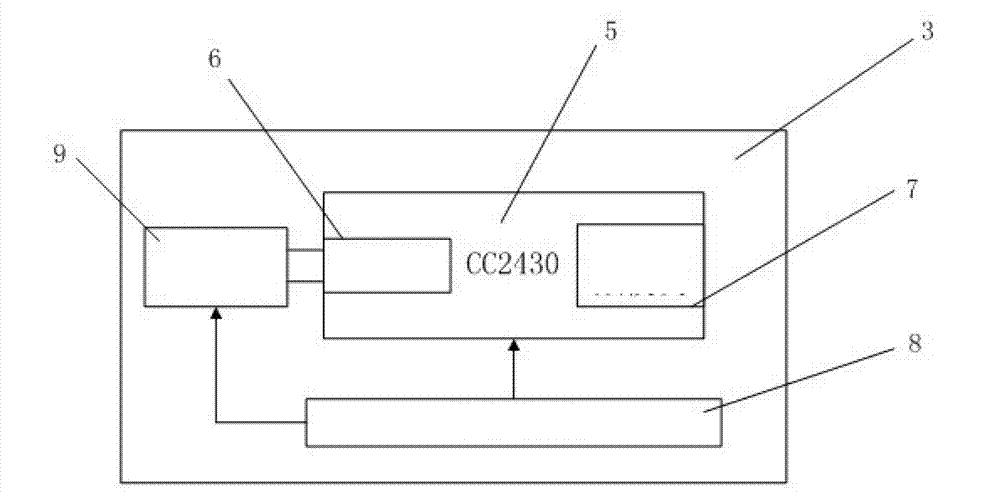

Self-adaptive positioning method and system based on resonance gradient method of received signal strength indicator (RSSI)

InactiveCN102890263AWith adaptive positioningFast positioningPosition fixationResonancePersonal computer

The invention discloses a self-adaptive positioning method based on a conjugate gradient method of a received signal strength indicator (RSSI). The method comprises the following steps of: firstly, performing Gauss processing on a measured RSSI value to eliminate the influence of environmental factors; secondly, weighting the measured RSSI value; and finally, searching an optimal unknown node coordinate through the conjugate gradient method. A positioning system automatically detects the RSSI value at fixed time, so positioning parameters can be automatically adjusted and repositioned. The positioning system comprises at least three reference node modules, a to-be-positioned module, a gateway node module and a personal computer (PC), wherein the reference node modules are arranged in a detection area and used for providing position information; the gateway node module is connected with the to-be-positioned module and used for establishing a network and transmitting information; and the PC is connected with the gateway node module and used for determining the position of the to-be-positioned module according to the information which is sent by the gateway node module.

Owner:SHANGHAI JIAO TONG UNIV

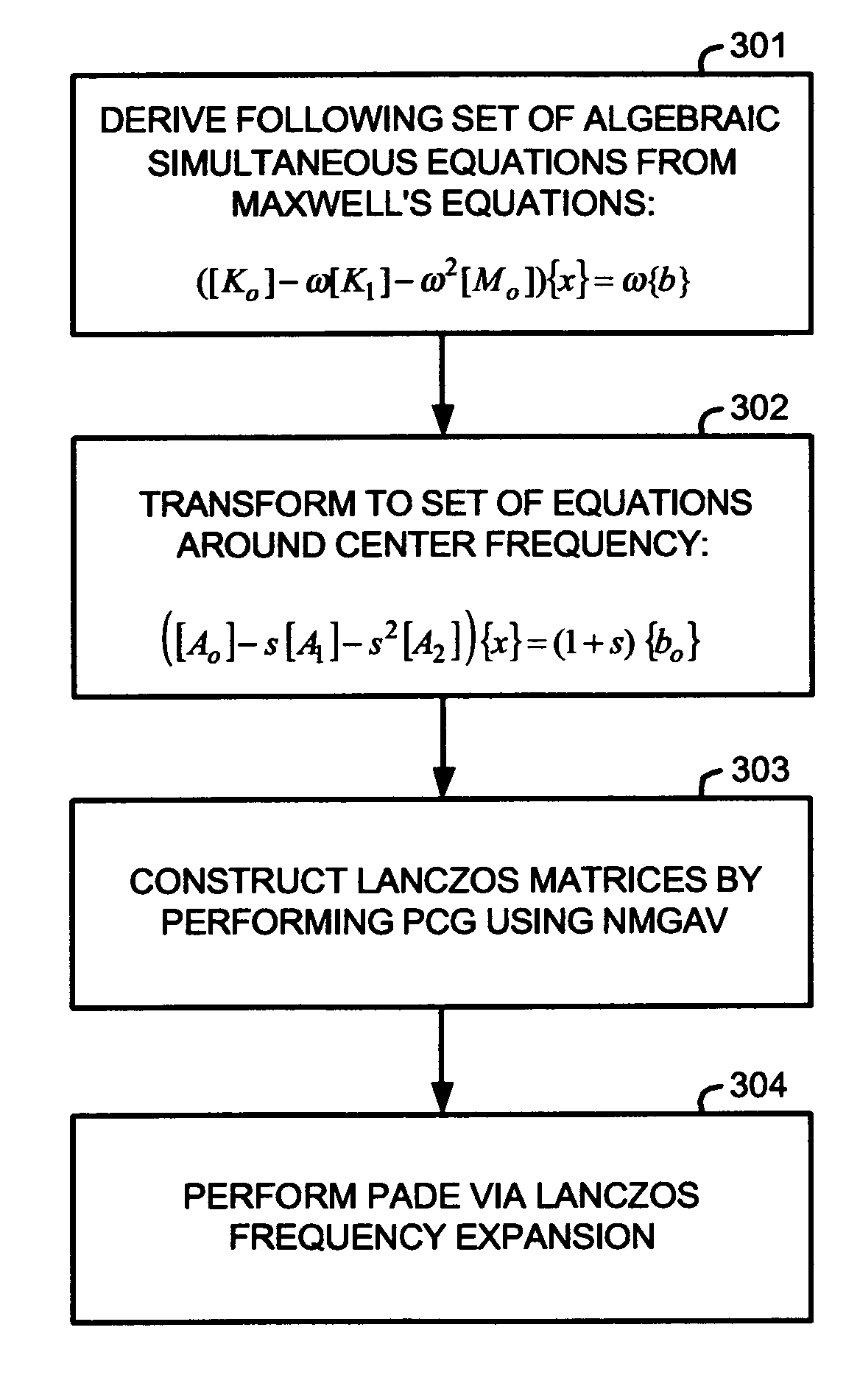

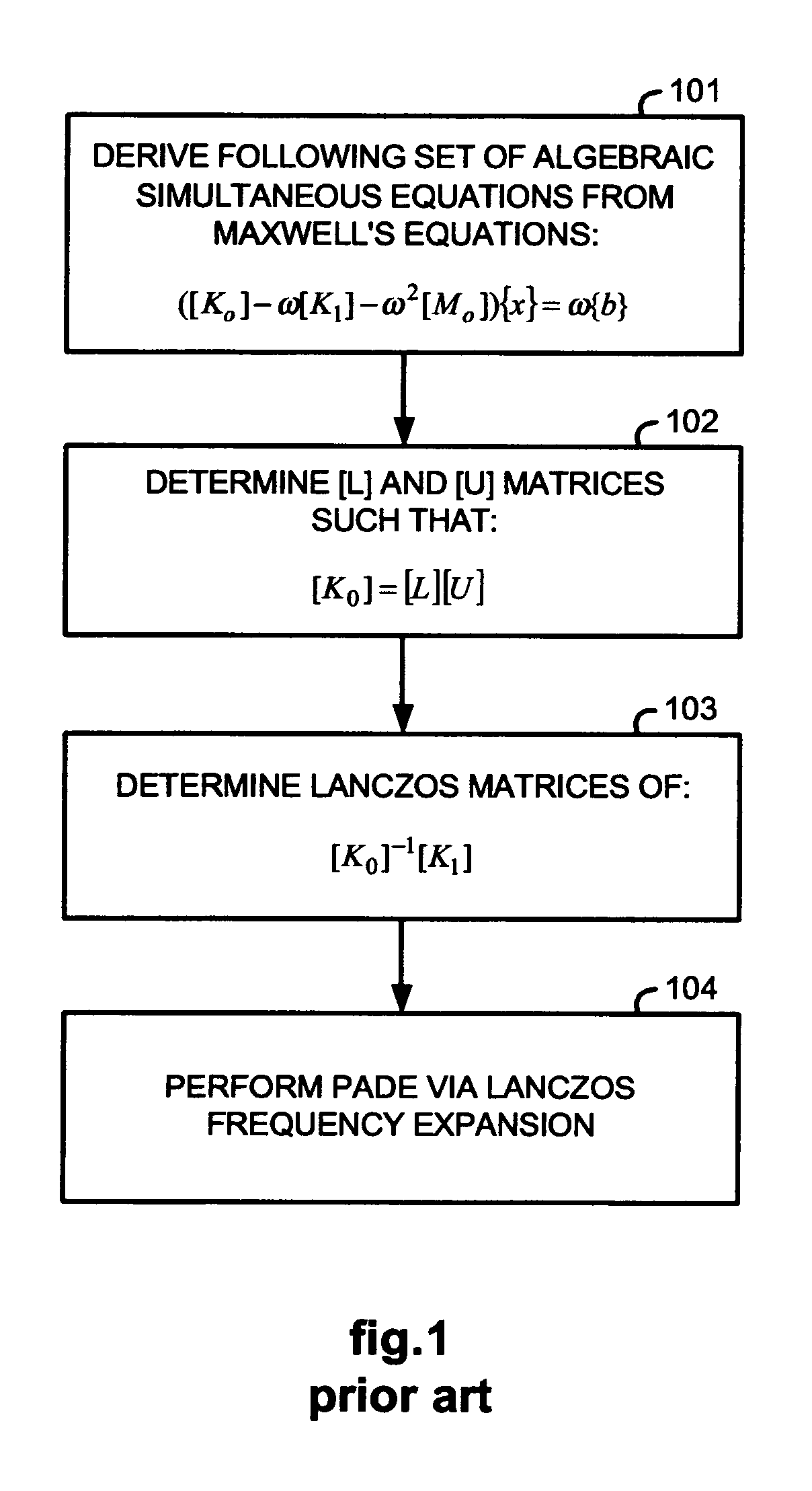

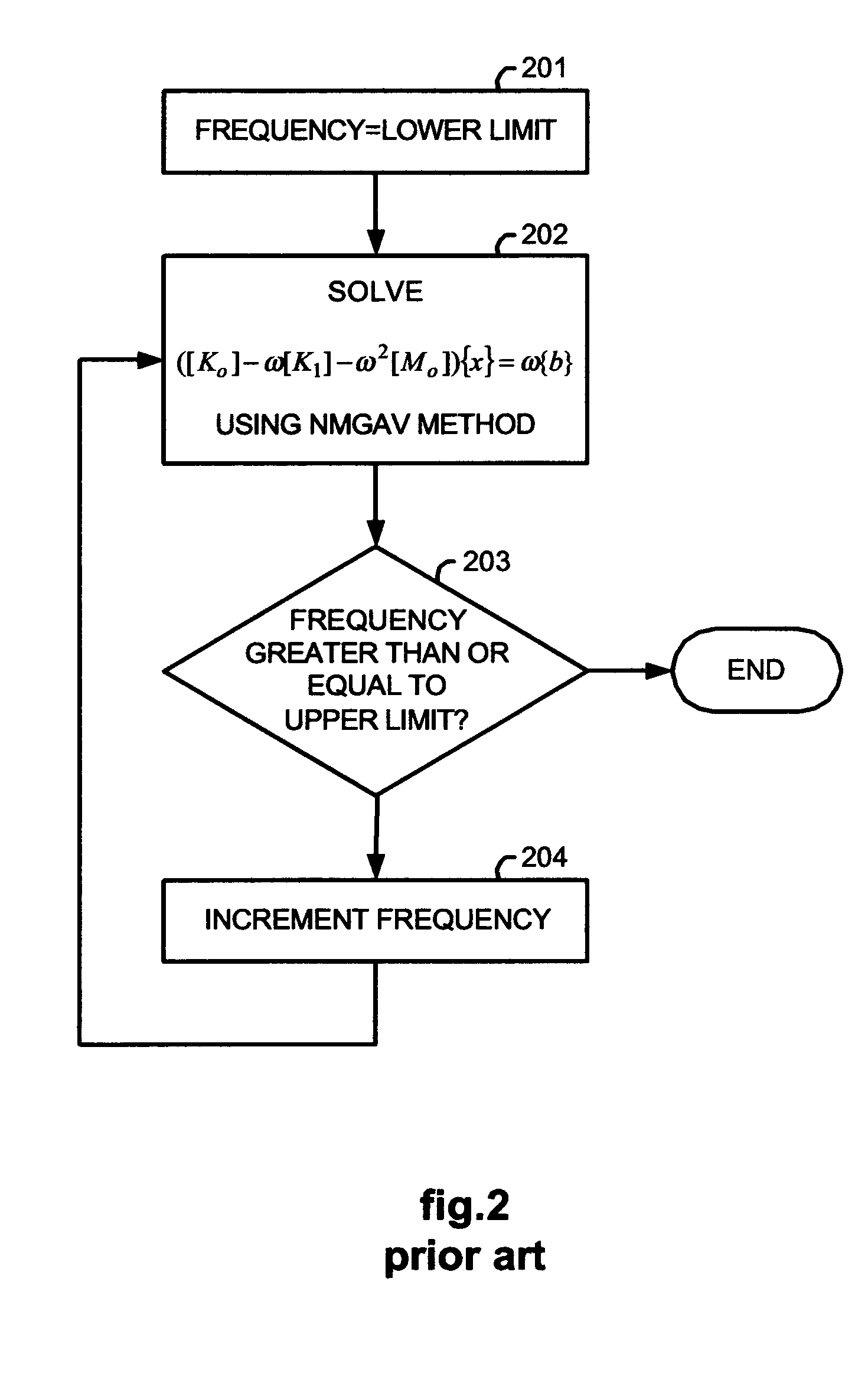

Method for determining electrical and magnetic field effects

InactiveUS20050197808A1Computation using non-denominational number representationComplex mathematical operationsMatrix decompositionScalar potential

A method for determining electrical and magnetic field effects determines Lanczos matrices by performing a preconditioned conjugate gradient method using a nested multi-grid, vector and scalar potential preconditioner so that Pade via Lanczos frequency expansion may be used to determine the electrical and magnetic field effects over a frequency range without having to perform computationally slow and memory intensive matrix decomposition.

Owner:OPTIMAL CORP

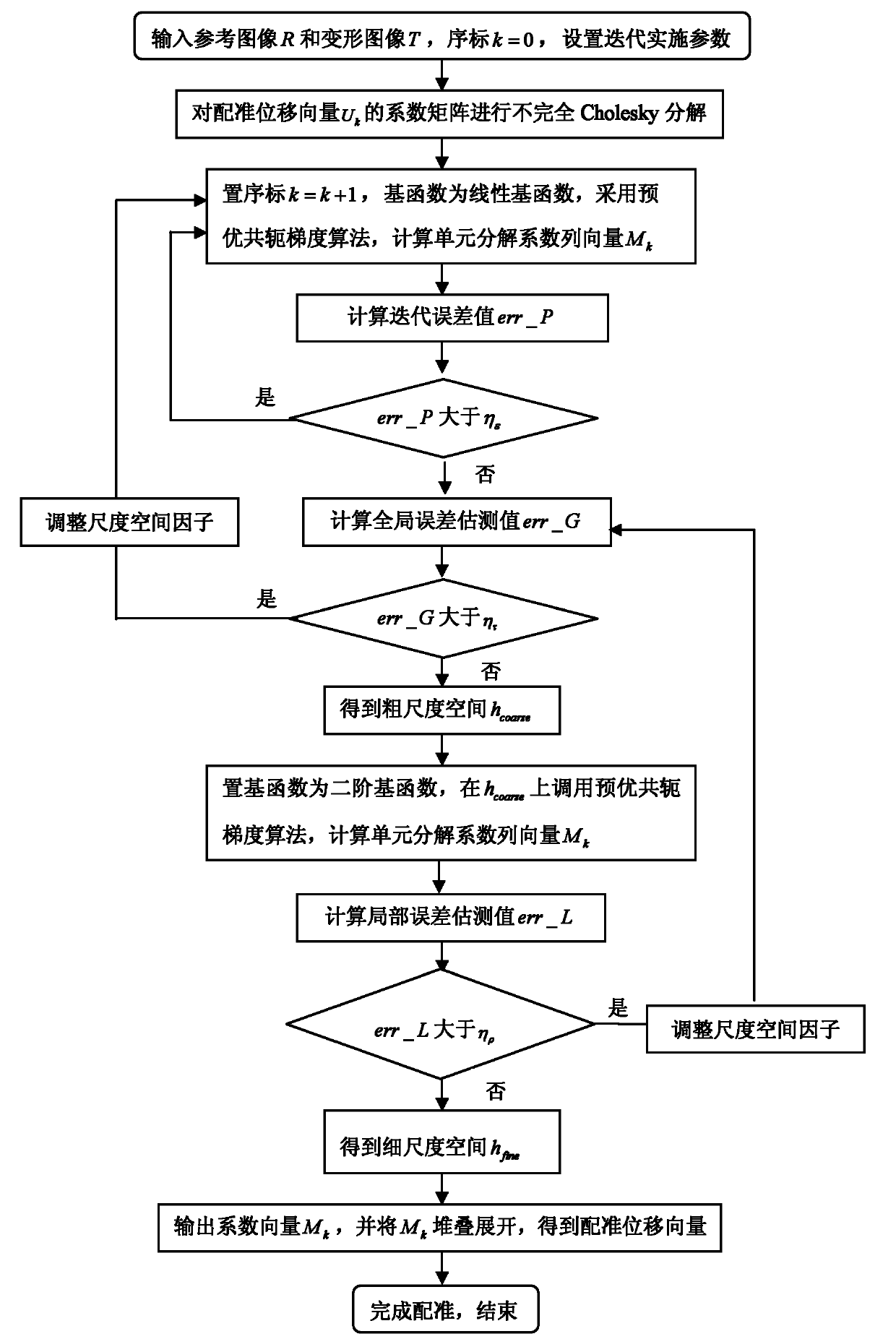

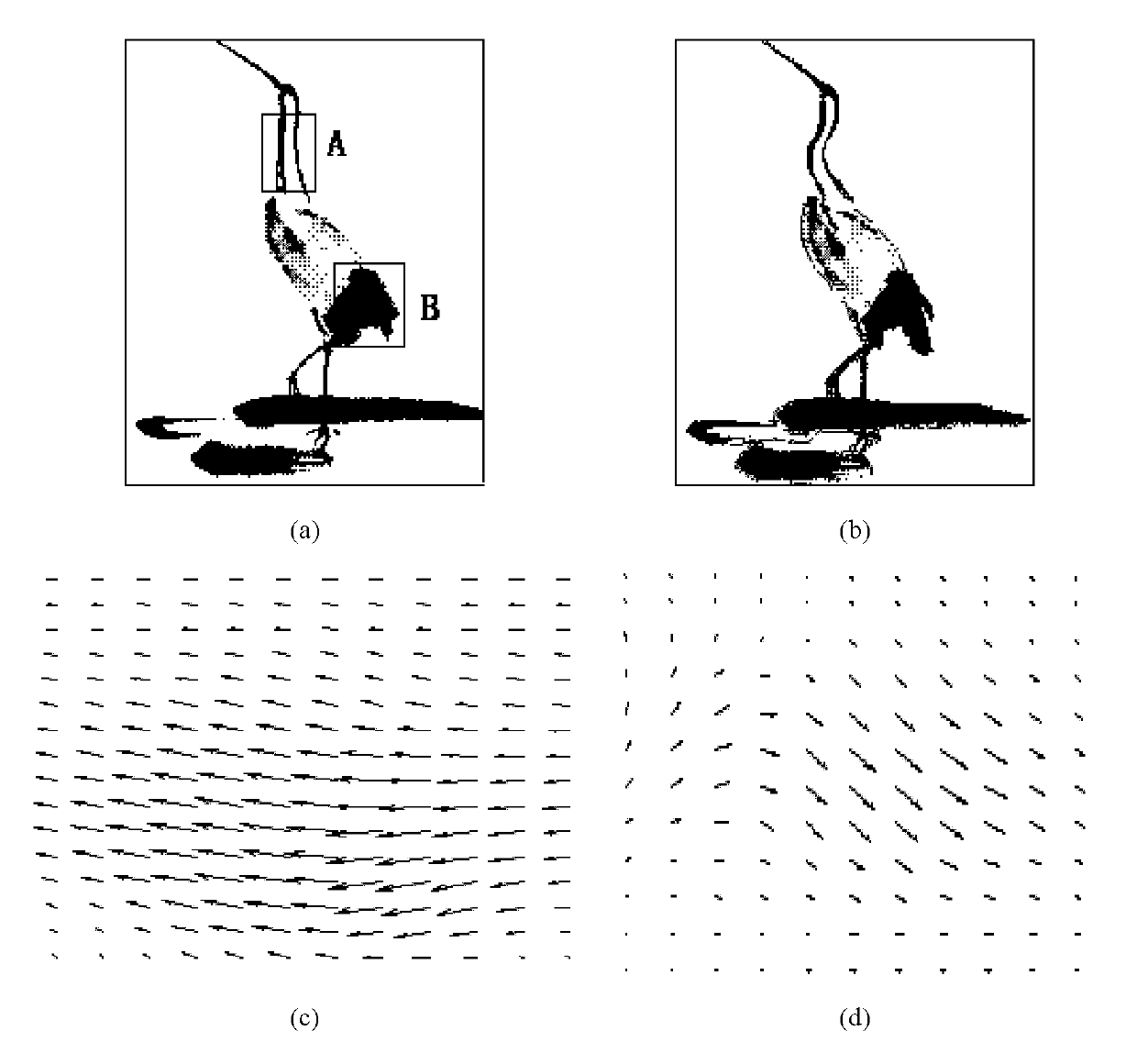

A Method for Inkjet Printing Texture Image Registration Based on Cell Decomposition Optical Flow Field

ActiveCN102262781AReduce bias defectsAvoid difficultiesImage analysisPattern recognitionIncomplete Cholesky factorization

The invention relates to a method for the registration of an ink-jet printing texture image based on a unit decomposition optical flow field. The method comprises the following steps of: 1, inputting a reference image and a distorted image and setting iteration implementation parameters; 2, performing incomplete Cholesky decomposition on a coefficient matrix of a registration displacement vector;3, taking a primary function as a linear primary function, and solving a unit decomposition coefficient column vector by a preconditioned conjugate gradient method according to an iteration error value; 4, calculating an overall error estimation value, and adjusting a scale space to obtain a rough scale space; 5, taking the primary function as a second order primary function, and solving the unitdecomposition coefficient column vector on the rough scale space according to a local error estimation result to obtain a fine scale space; and 6, stacking and expanding the unit decomposition coefficient column vector on the fine scale space to obtain the registration displacement vector and complete registration. By the method, the registration representation capability of a feature texture curve can be effectively improved, the registration precision in noise environment is improved, and the registration speed in noise environment is increased. Therefore, the method is applicable for the registration of the ink-jet printing texture image.

Owner:ZHEJIANG UNIV OF TECH

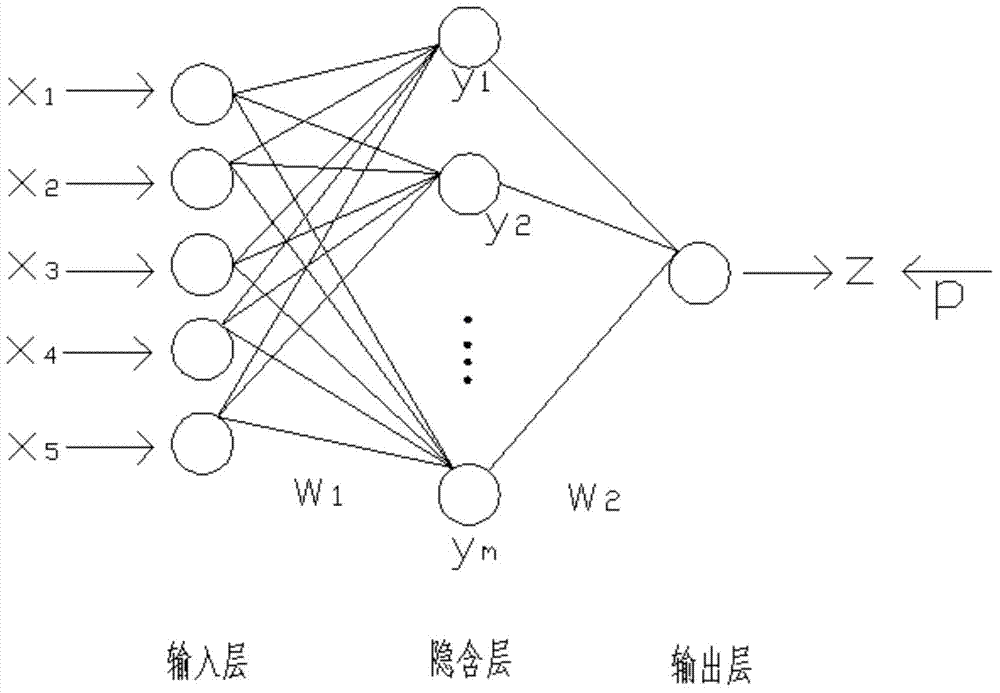

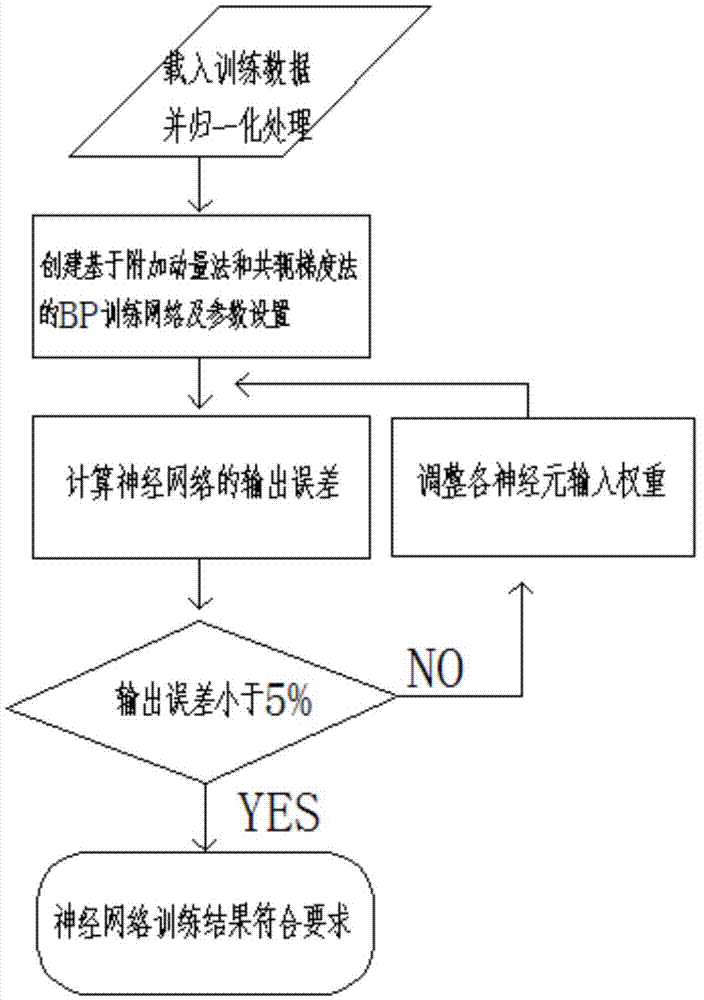

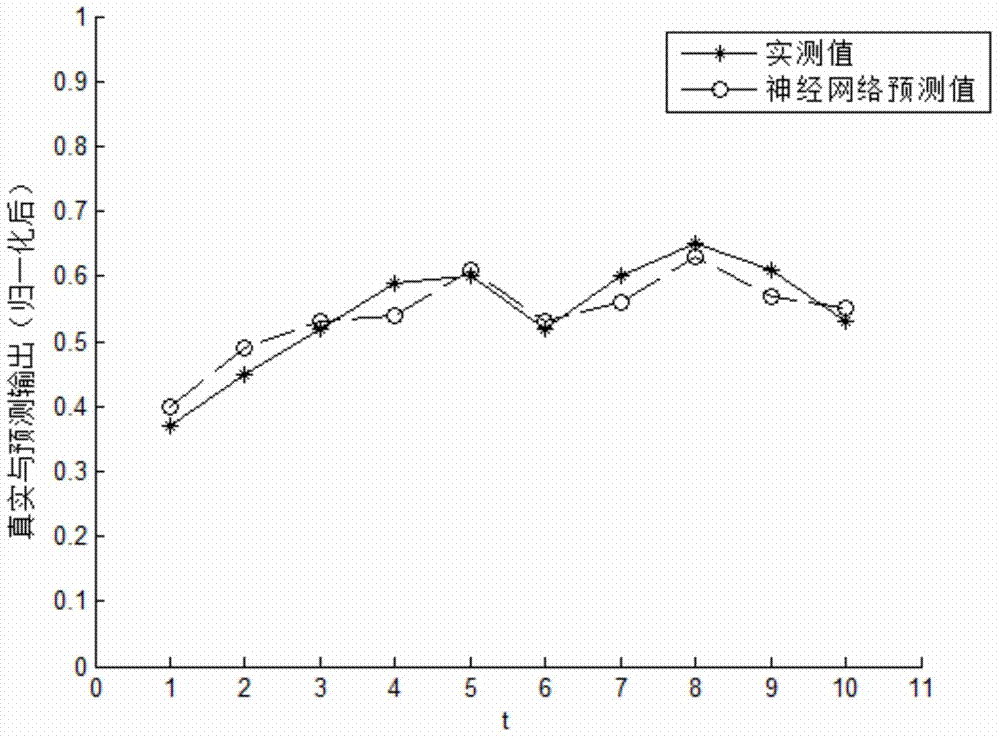

High-speed cold-rolling mill third octave flutter prediction method based on BP neural network

ActiveCN103886373AImprove learning effectHigh precisionBiological neural network modelsSpecial data processing applicationsMomentumOctave

A high-speed cold-rolling mill third octave flutter prediction method based on a BP neural network is a method for predicting the machine frame vibration situation in the rolling process of a high-speed cold-rolling mill by utilizing the neural network and belongs to the field of material engineering computer neural network techniques. An additional momentum method and a conjugate gradient method are introduced to improve a BP neural network prediction mode. By adopting the additional momentum method, the network local minimum problem in rational neural network application can be solved, the algorithmic accuracy can be effectively improved, and the network leaning capacity can be improved. Due to the fact that the number of network parameters is large and considering the problems of large storage capacity and low convergence rate, the conjugate gradient method is selected, and good training effect is obtained. The high-speed cold-rolling mill third octave flutter prediction method is effectively applied to third octave flutter prediction of the high-speed cold-rolling mill and used for guiding production.

Owner:TIANJIN HAIGANG STEEL SHEET

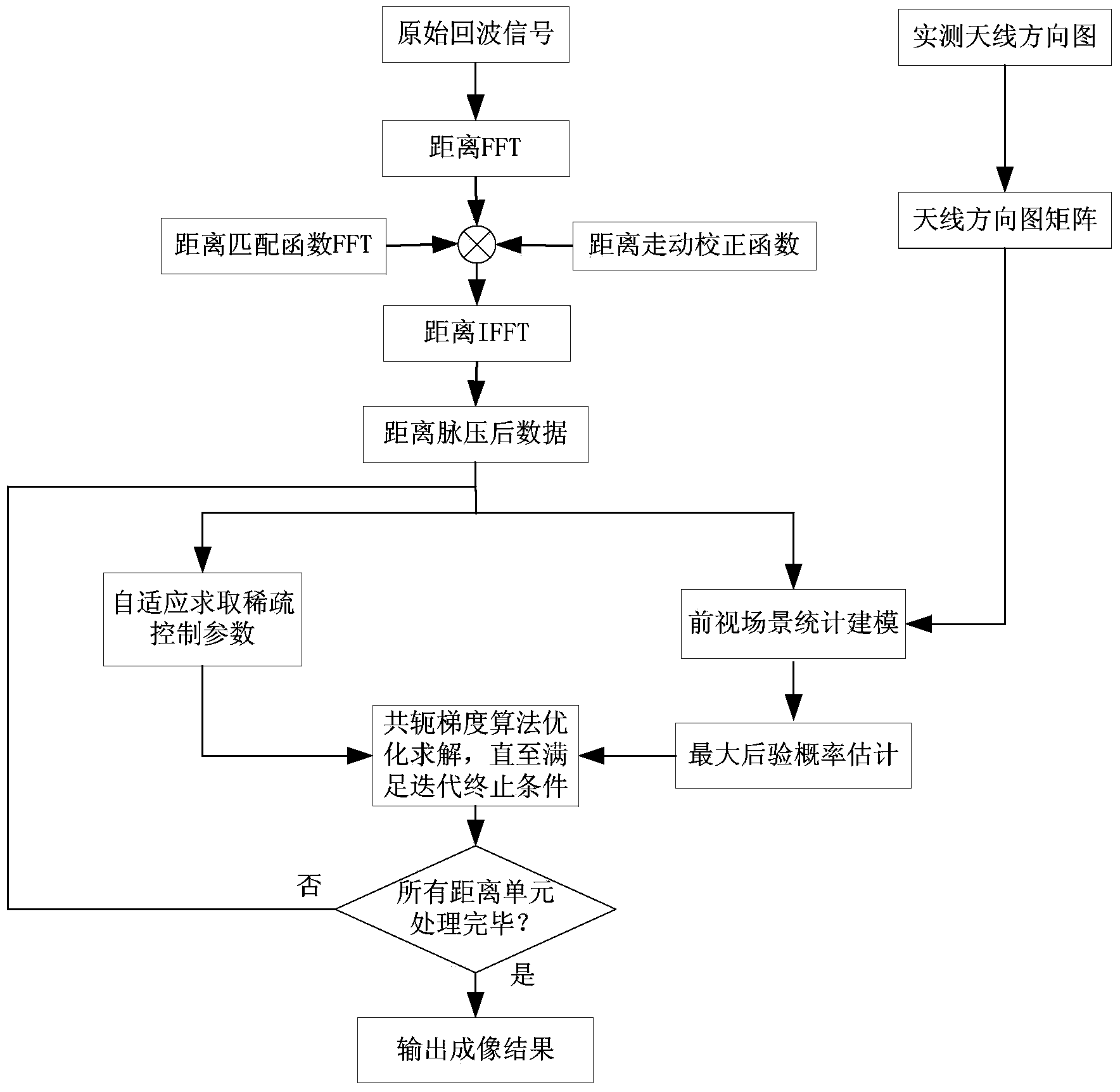

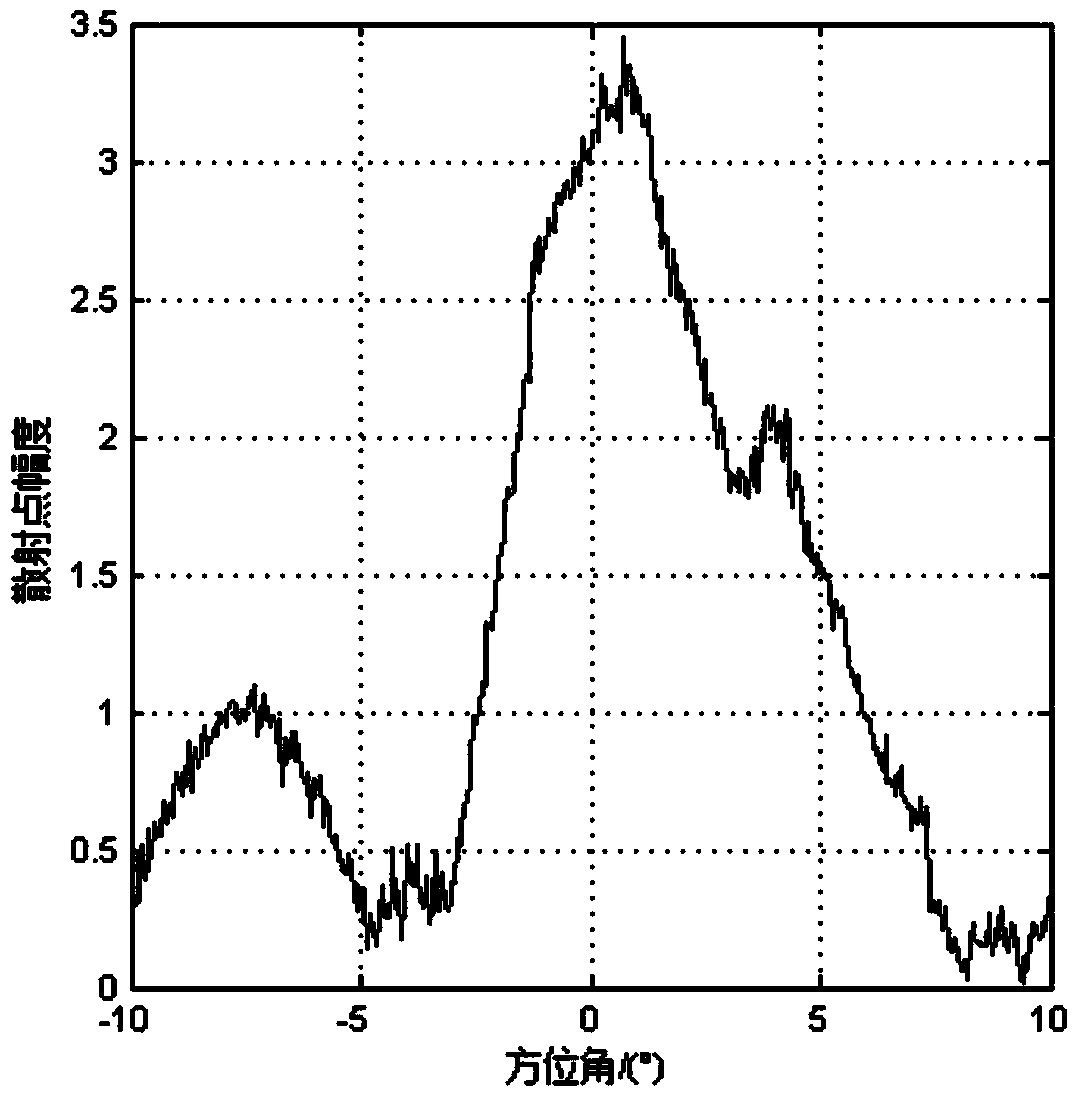

Airborne radar foresight super-resolution imaging method utilizing sparse statistical property

ActiveCN103885058AIterative solution robustnessPromote engineering applicationSpecial data processing applicationsRadio wave reradiation/reflectionRange migrationImaging technique

The invention belongs to the technical field of airborne radar foresight super-resolution imaging and discloses an airborne radar foresight super-resolution imaging method utilizing sparse statistical property. The method comprises the steps that an antenna pattern matrix H of data s obtained after range migration correction is obtained; airborne radar comprises M distance units; in the data s obtained after range migration correction, the datum corresponding to the ith distance unit is si, and i is a number between 1 and M; si can be represented as the format: si = H.sigma i + n, wherein sigma i represents the foresight scene target scattering coefficient corresponding to the ith distance unit to be solved, and n is set noise; sigma 1 to sigma M are obtained based on the conjugate gradient method according to the Bayes criterion and the airspace sparse property of a target scene, and then super-resolution imaging of the airborne radar under the foresight scene is achieved.

Owner:XIDIAN UNIV

Method and apparatus for efficient training of support vector machines

ActiveUS7440944B2Increase speedLearning speed of a support vector machine classifierData processing applicationsDigital data information retrievalSupport vector classifierLine search

The present invention provides a system and method for building fast and efficient support vector classifiers for large data classification problems which is useful for classifying pages from the World Wide Web and other problems with sparse matrices and large numbers of documents. The method takes advantage of the least squares nature of such problems, employs exact line search in its iterative process and makes use of a conjugate gradient method appropriate to the problem. In one embodiment a support vector classifier useful for classifying a plurality of documents, including textual documents, is built by selecting a plurality of training documents, each training document having suitable numeric attributes which are associated with a training document vector, then initializing a classifier weight vector and a classifier intercept for a classifier boundary, the classifier boundary separating at least two document classes, then determining which training document vectors are suitable support vectors, and then re-computing the classifier weight vector and the classifier intercept for the classifier boundary using the suitable support vectors together with an iteratively reindexed least squares method and a conjugate gradient method with a stopping criterion.

Owner:R2 SOLUTIONS

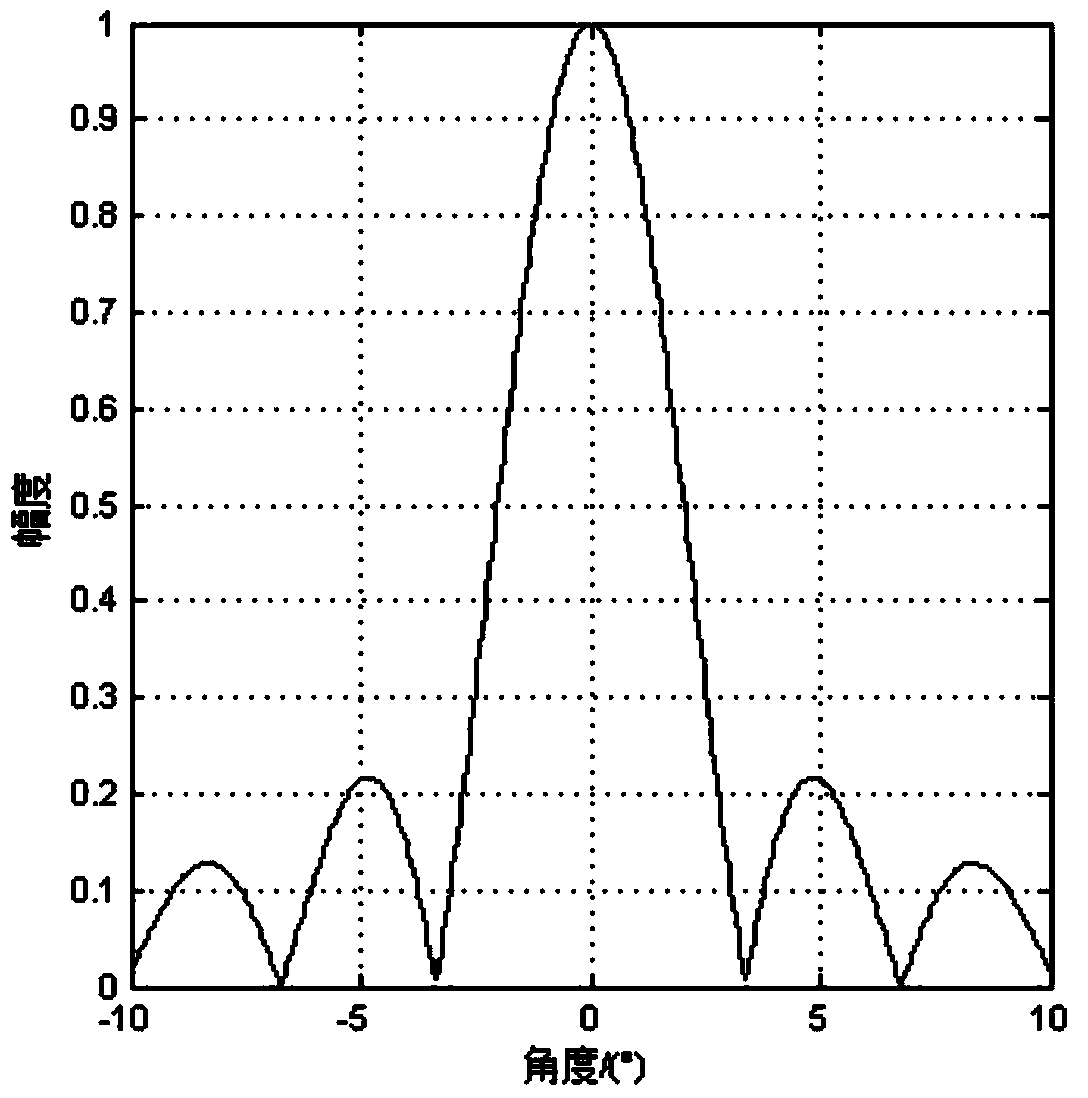

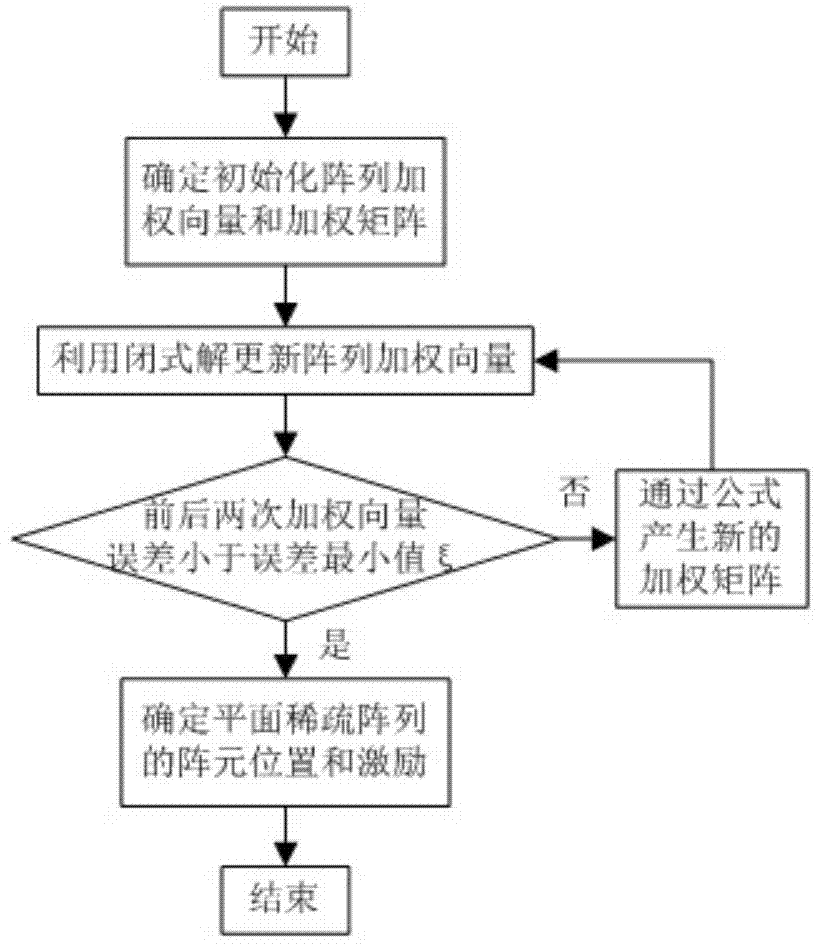

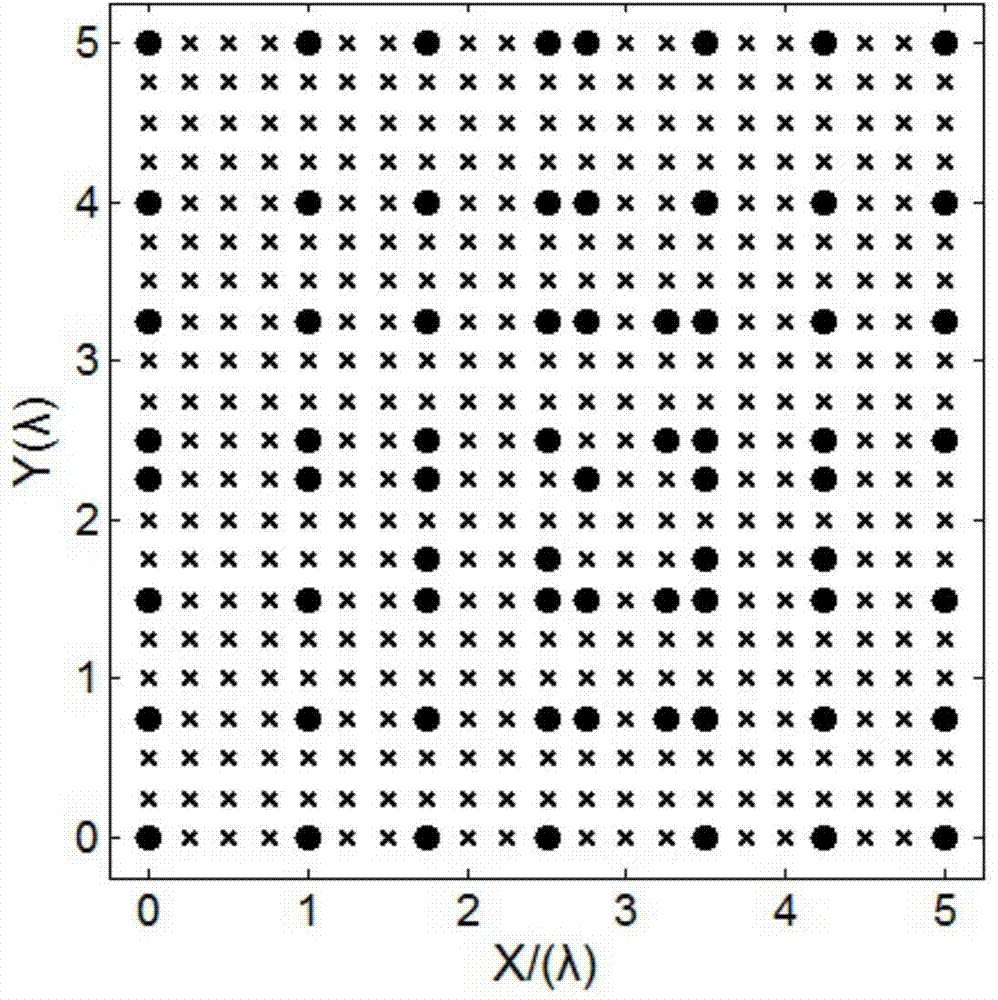

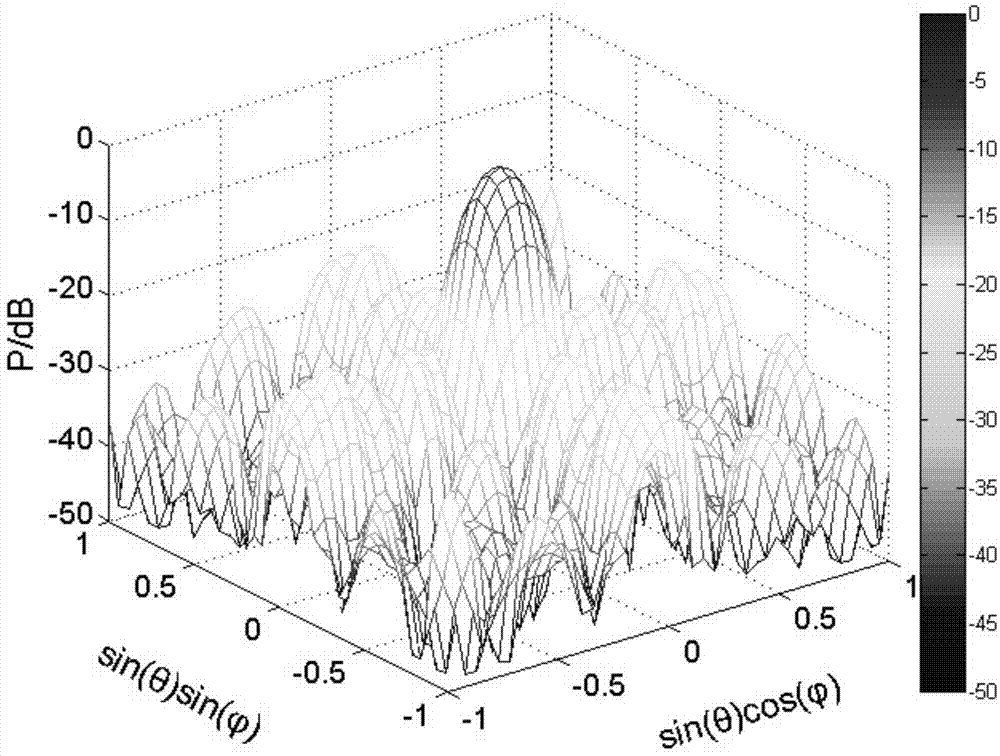

Rapid planar sparse array synthesis method

InactiveCN104750944AAvoiding Computational Ill Conditioning ProblemsVersatilitySpecial data processing applicationsConjugate gradient solverSynthesis methods

The invention discloses a rapid planar sparse array synthesis method. The method has the advantages that a conventional planar array synthesis constraint optimization model is converted into an unconstraint optimization problem by constructing a Lagrange function, so that calculation ill-posed problems in the iterative optimization process of a planar array are avoided, an array weight vector can be updated by the aid of closed-form solution in each time of iteration, planar array synthesis problems can be solved without an optimization tool, the method is more universal and transportability, an inverse matrix in the closed-form solution is quite large in scale as a two-dimensional space angle sample number of the planar array is increased in a quadratic manner, the inversion problem of the large-scale matrix is solved by introducing a conjugate gradient method, and convergence of planar array synthesis is accelerated, so that the method is higher in real-time performance and particularly applicable to occasions with high requirements on array optimization real-time performance and universality.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

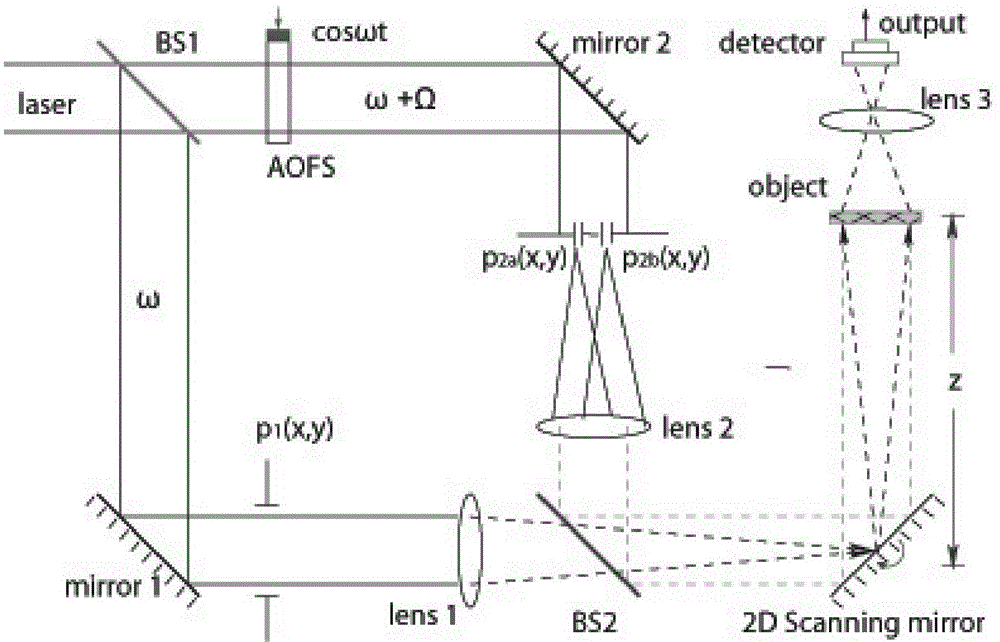

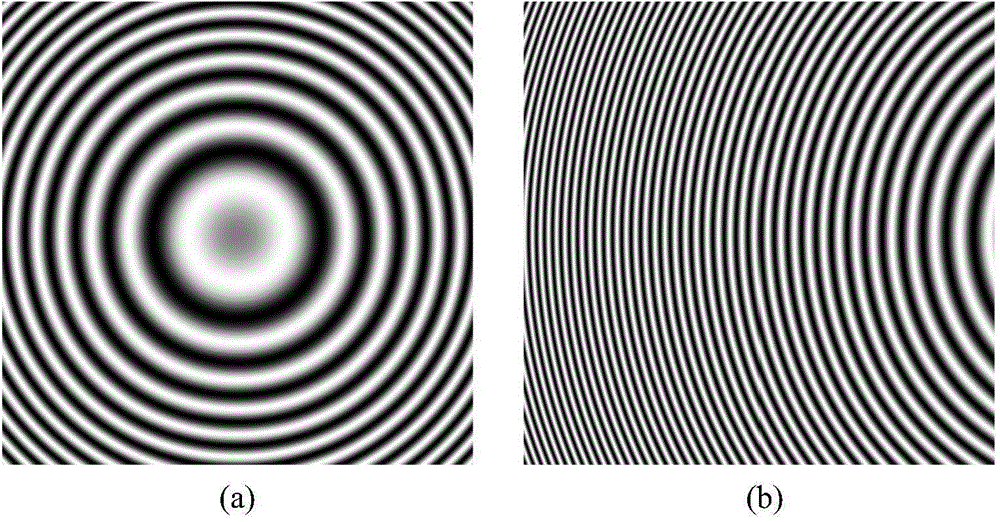

Optical scanning holographic image edge extracting method based on double-hole pupil

InactiveCN104614970AExtract clearSimple structureInstrumentsOptical scanning holographyEdge extraction

An optical scanning holographic image edge extracting method based on a double-hole pupil belongs to the technical field of the optical scanning holographic technology. The method includes the following steps: 1 arranging the double-hole pupil to be that P2a (x, y)= sigma (x-x1, y-y1) to obtain a first Fresnel zone plate h1 and conduct first two-dimensional holographic scanning to obtain a hologram s1; 2 arranging the double-hole pupil to be that P2b (x, y)= sigma (x-x2, y-y2) to obtain a second Fresnel zone plate h2 and conduct second two-dimensional holographic scanning to obtain a hologram s2 to record more object high frequency information; 3 conducting Fourier transform on the holograms obtained through the two-dimensional holographic scanning, and a conjugate gradient method is introduced to conduct inverse problem solving. The method is simple in structure and easy to operate, has high practicability, can achieve edge extraction of clear objects and has high application value.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

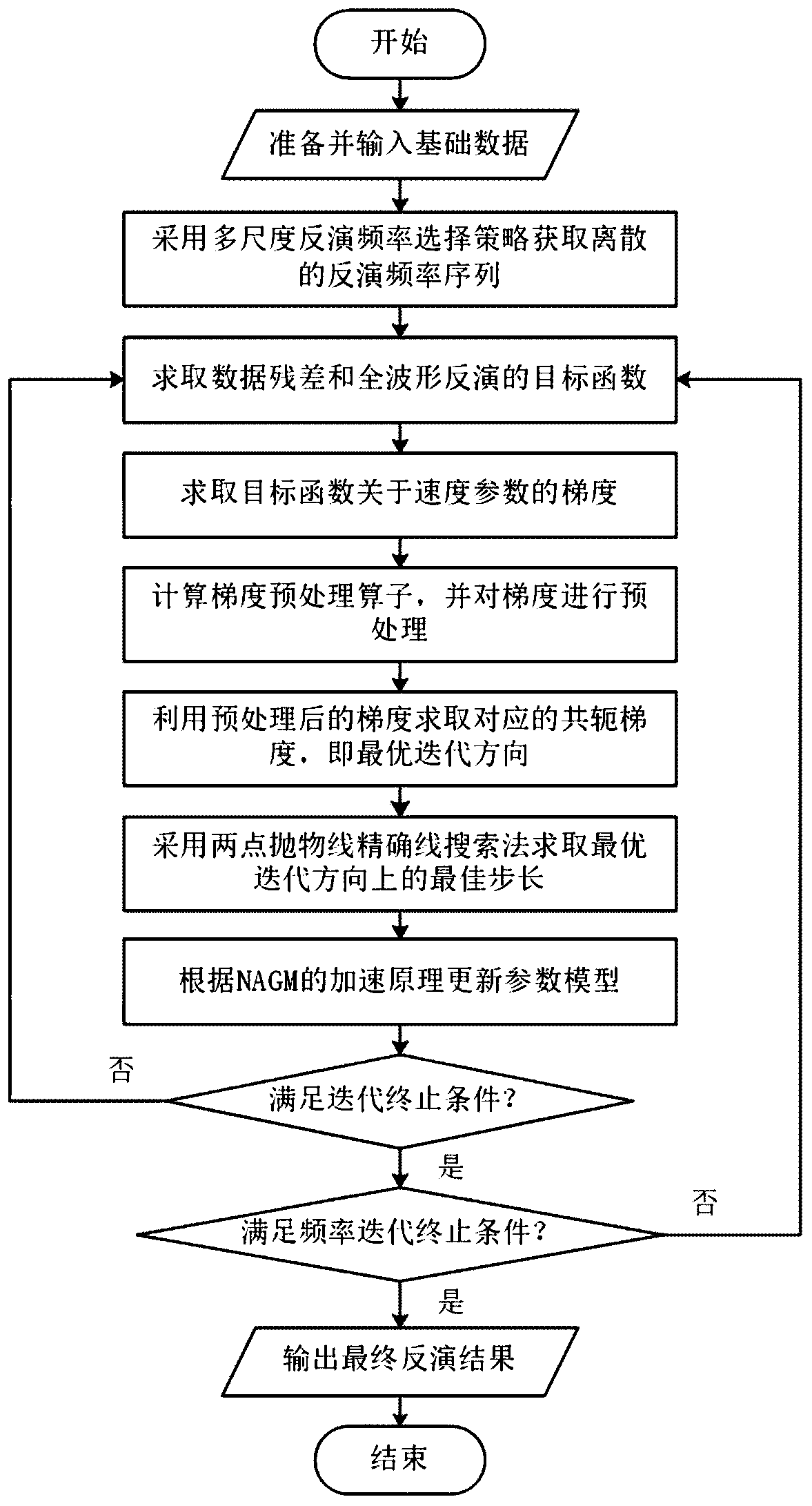

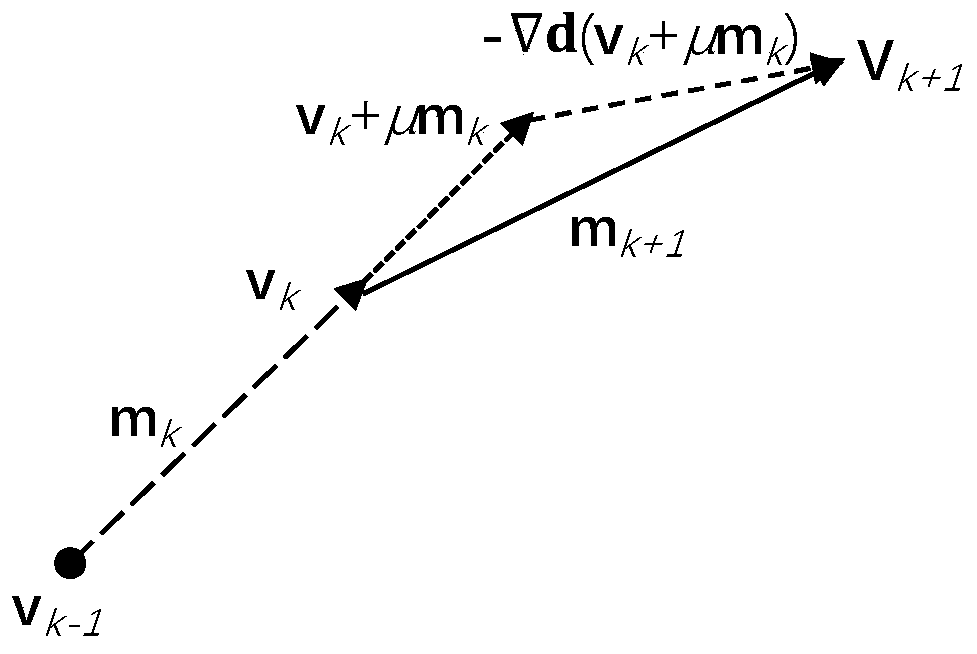

Full waveform inversion method based on preconditioned conjugate gradient acceleration algorithm

InactiveCN110058302AImprove stabilityHigh precisionSeismic signal processingClassical mechanicsFull waveform

The invention discloses a full waveform inversion method based on preconditioned conjugate gradient acceleration algorithm, and belongs to the technical field of seismic exploration inversion imaging.According to the method, the shortcomings of slow convergence speed and low deep inversion accuracy of conjugate gradient full waveform inversion methods are overcome. The advantages of a gradient preconditioning operator and a Nesterov acceleration gradient descent method are combined, while the deep inversion accuracy of the conjugate gradient full waveform inversion method is improved, the convergence speed is effectively increased, thus the calculation amount of full-waveform inversion is reduced, and the technical support is provided for practical application of the full-waveform inversion.

Owner:SICHUAN INST OF GEOLOGICAL ENG INVESTIGATION

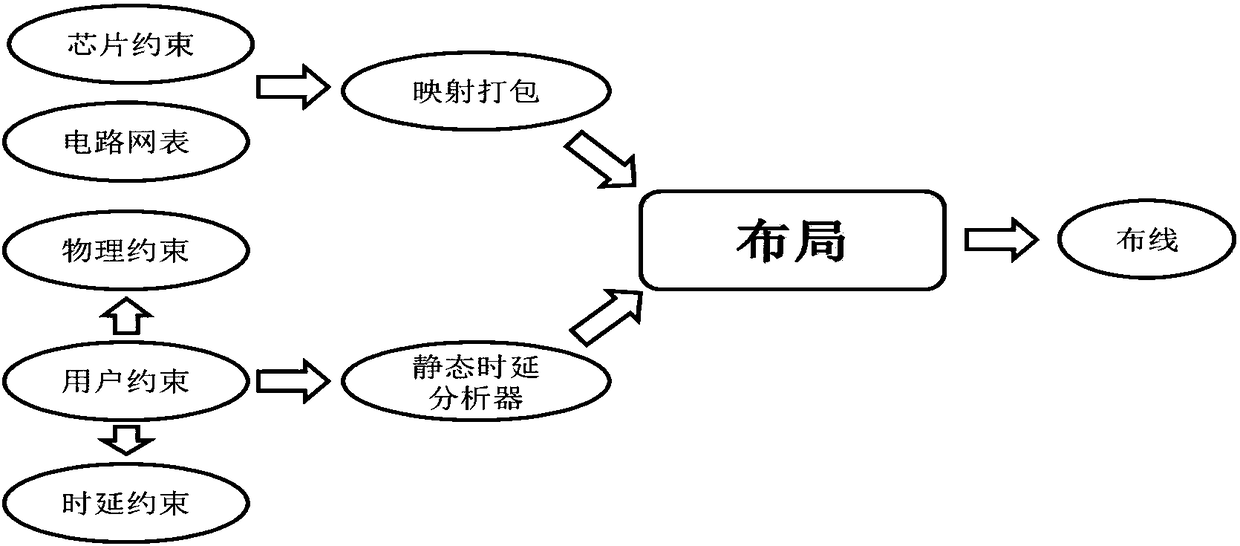

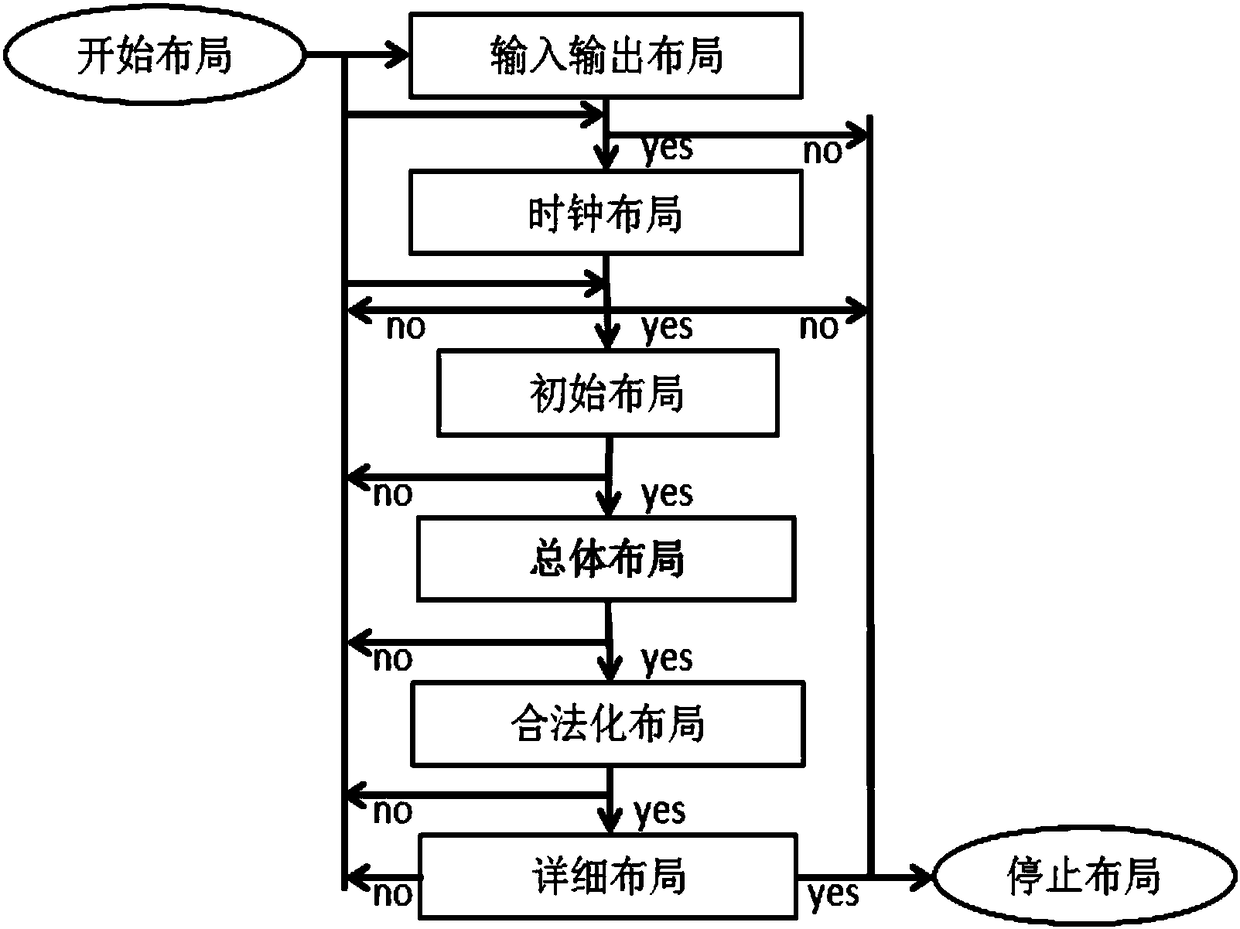

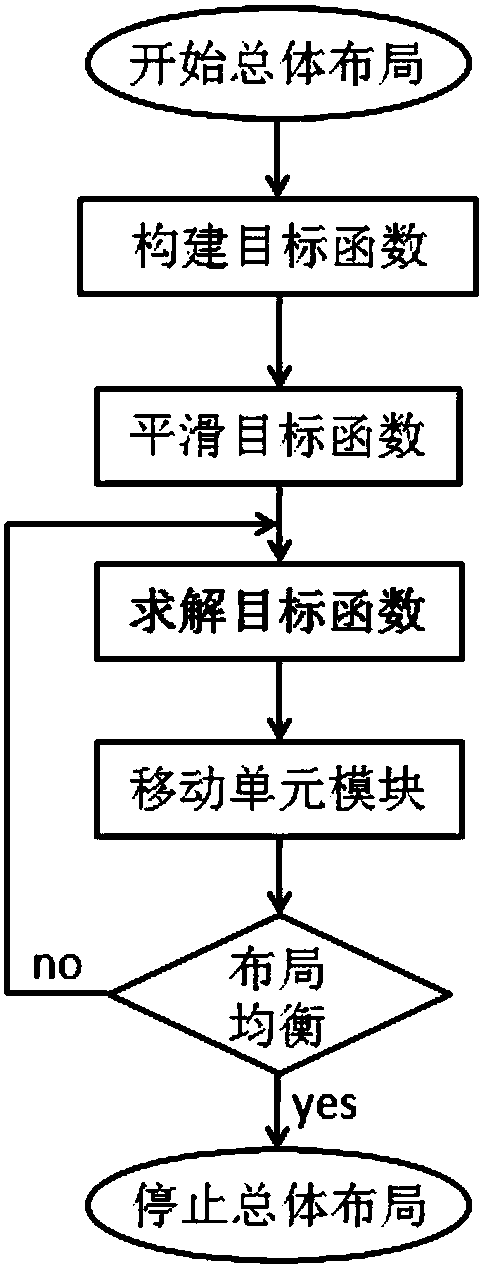

Overall FPGA automated layout method based on analytical method

ActiveCN108287932AAutomated layout is fastReduce constraintsSpecial data processing applicationsComputer moduleConjugate gradient method

Disclosed is an overall FPGA automated layout method based on an analytical method. The layout method comprises the steps that S1, constraint information and circuit netlist information are packed andinput through mapping; S2, time delay information of user constraints is input through a static time delay analyzer; S3, each circuit unit module is automatically laid out in corresponding positionsin a physical design of a chip according to physical constraints designated by a user, and an input and output layout, a global clock layout, an initial layout, an overall layout, a legitimation layout and a detailed layout are involved; according to the overall layout, a conjugate gradient method based on a mixed step-length adjustment strategy is adopted for solving according to the initial positions of the circuit unit modules and circuit topological connection, a step-length calculation manner is dynamically adjusted aiming at the circuit unit modules of different levels and layout states,and the circuit unit modules are distributed; S4, the circuit netlist information is output. By means of the layout method, rapid automated layout is conducted on a chip layout, so that the line length and time delay of a network meet the user constraints; by adjusting a step-length optimization strategy of the overall layout, the quality and speed of the layout are optimized.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP