Patents

Literature

191 results about "Permissible Value" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The exact names, codes and text that can be stored in a data field in an information management system.

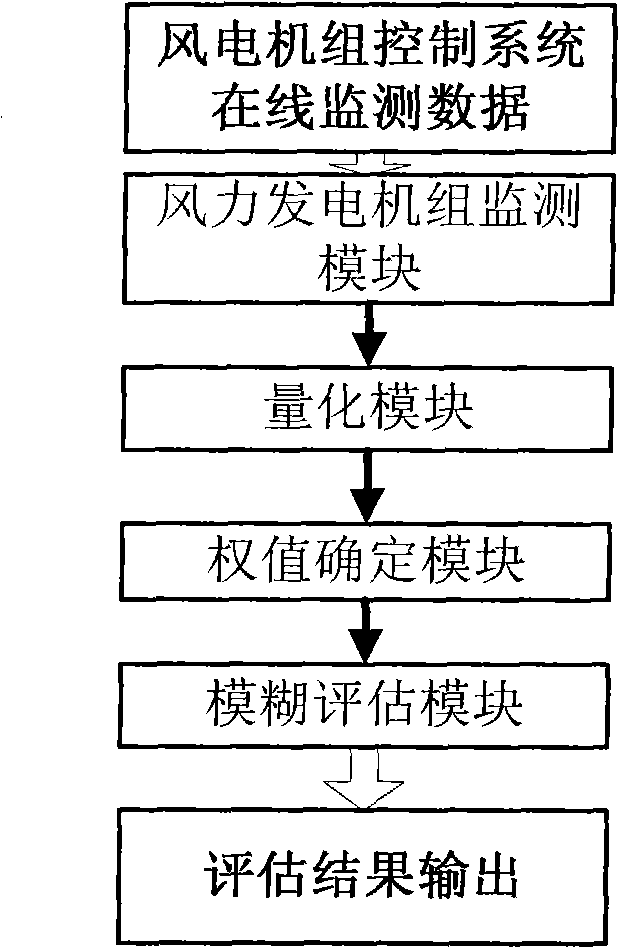

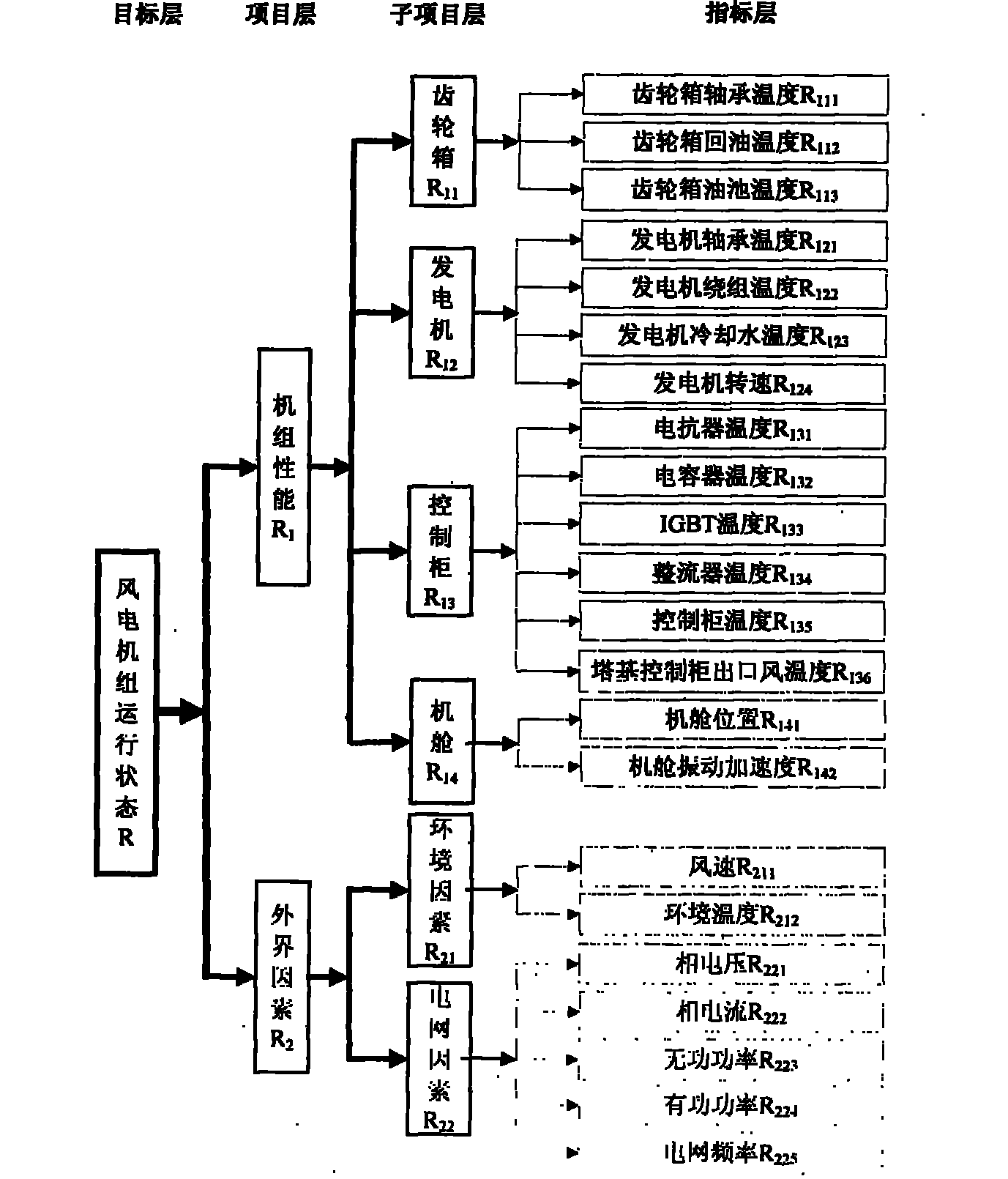

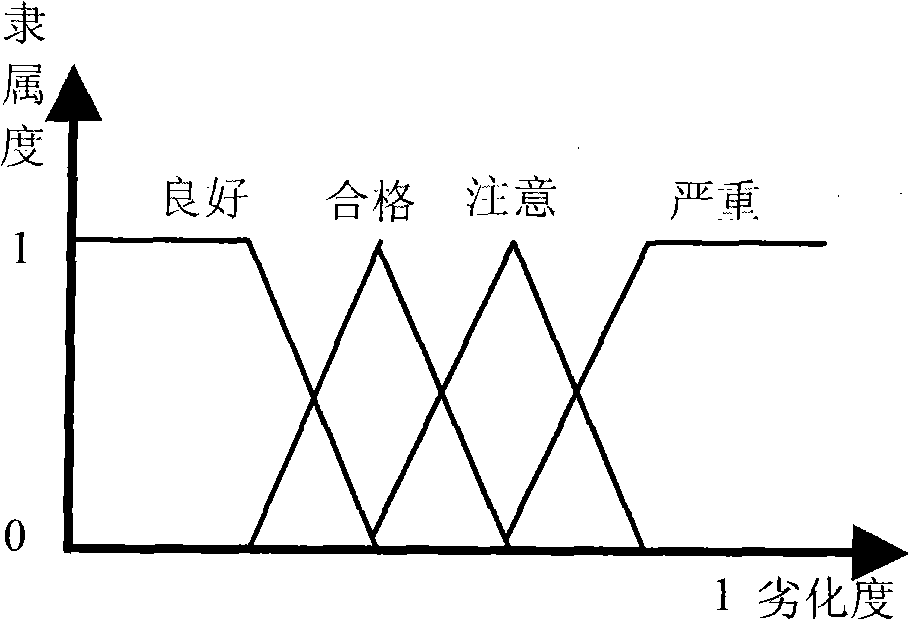

System and method thereof for evaluating real-time running state of wind generating set

ActiveCN101858312AGuaranteed uptimeAvoid the problem of invalid variable weightsEngine testingWind motor combinationsElectric power systemEngineering

The invention relates to the technical field of running state monitoring of wind generating sets, in particular to a system and a method for evaluating the running state of a wind generating set. The evaluating system mainly comprises a monitoring module, a quantifying module, a weight confirmation module and an evaluating module; data monitored in real time by a wind generating set control system are utilized as the input of the evaluating system of the real-time running state; then the data are quantified to obtain a real time deterioration degree of each evaluating index; finally, when the deterioration degree of a single item evaluating index and a permissible value have greater deviation, the serious evaluating result is directly given, otherwise, the weight module and the evaluating module are used for calculating an evaluating result of the running state of the generating set, and the evaluating result is used as the output of the system. The invention provides scientific basis for state maintenance of the wind generating set, and provides technological supports for ensuring high-efficient, reliable and safe running of the wind generating set, evaluating and forecasting the operational reliability of an electric power system of a windy electric field, and has important engineering application value.

Owner:CHONGQING UNIV +1

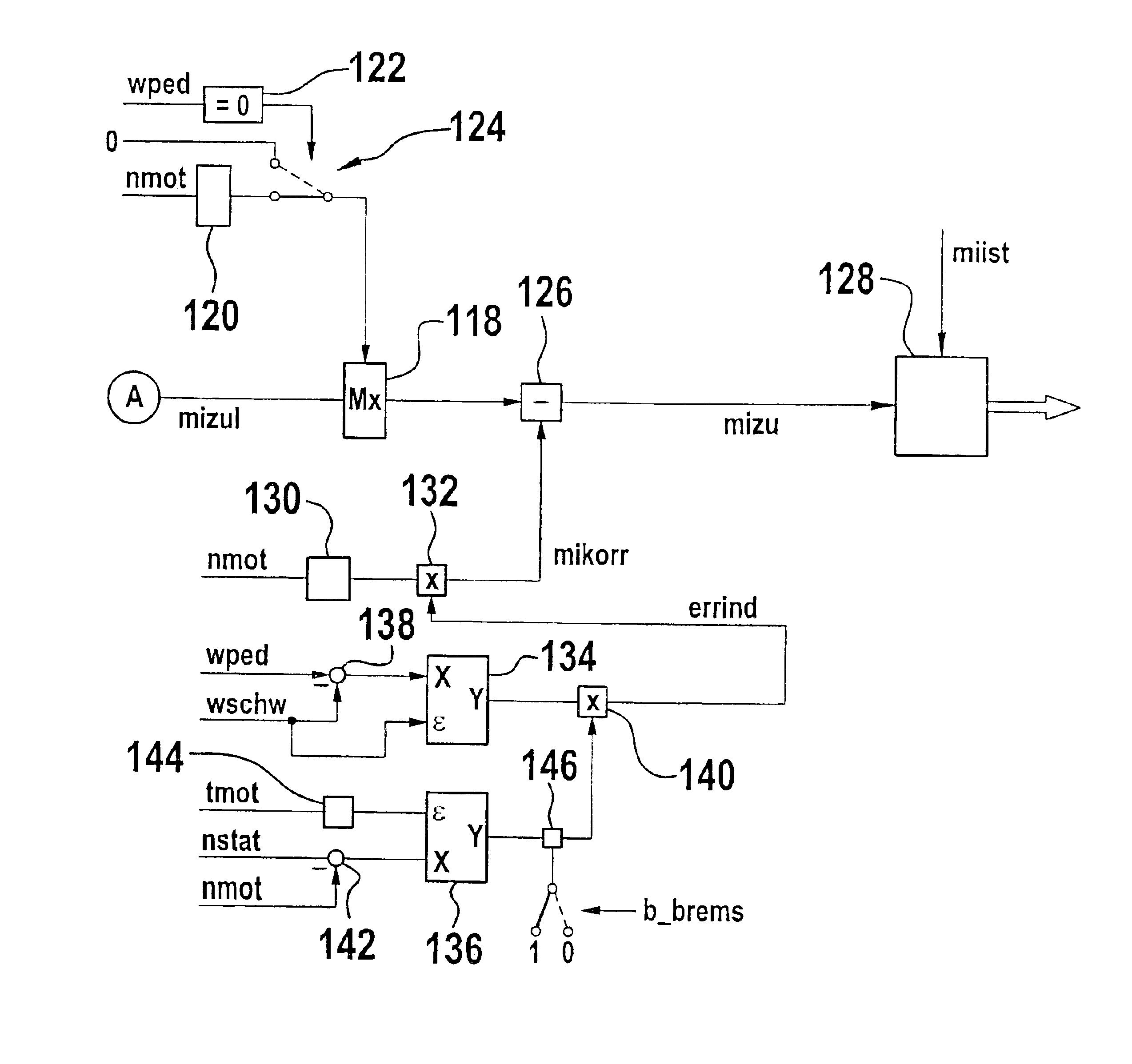

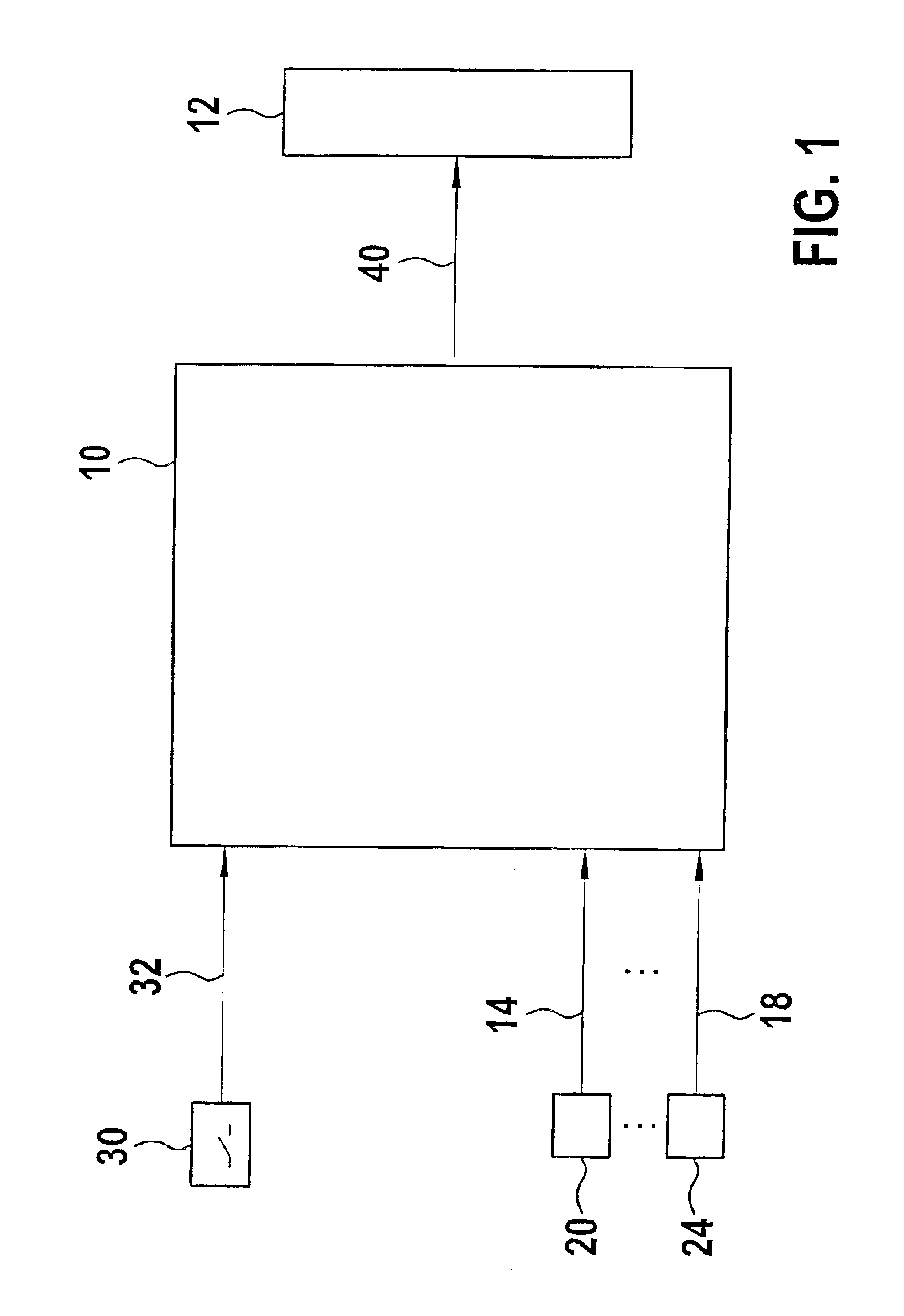

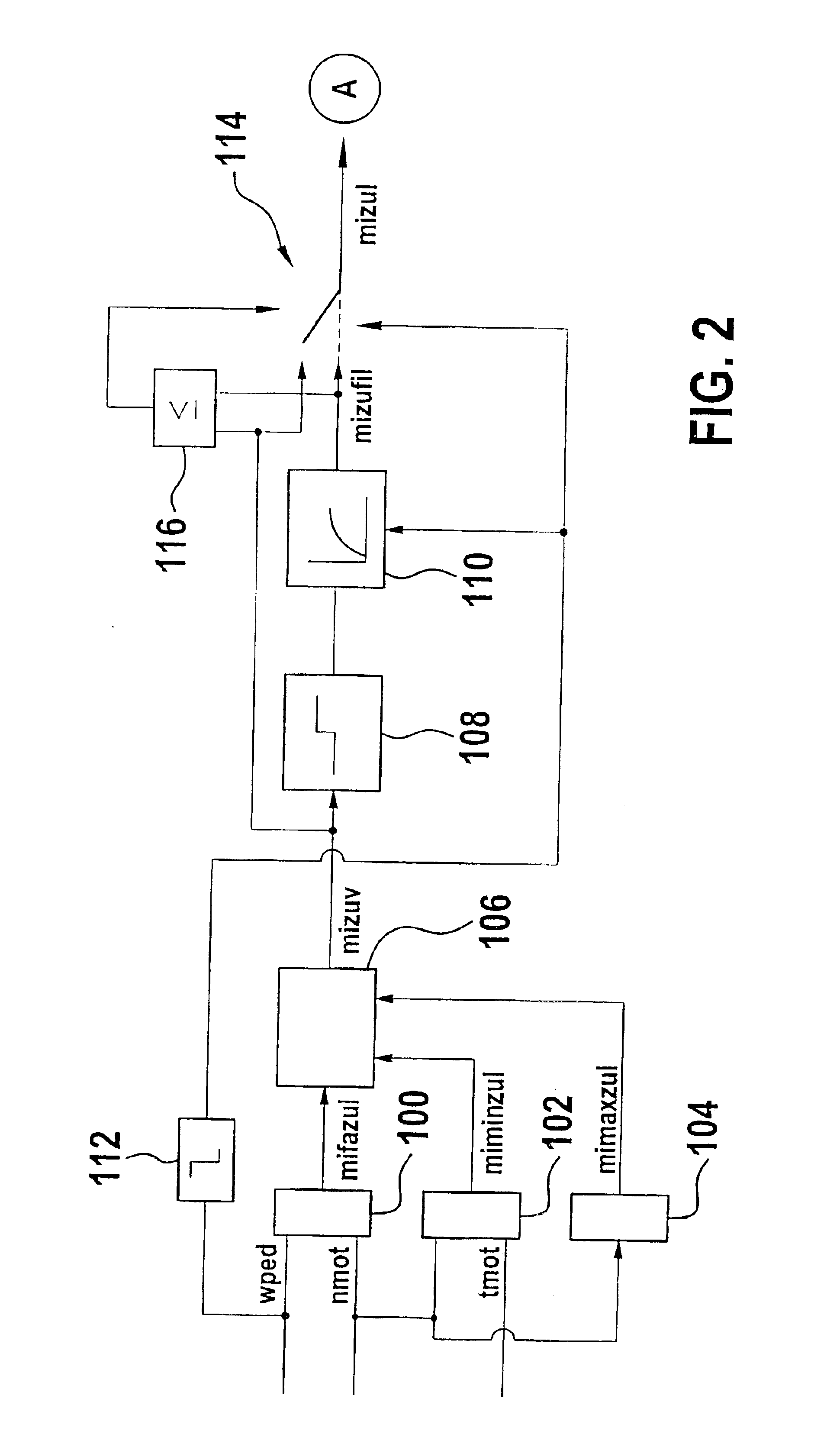

Method and device for controlling a drive unit

InactiveUS6854444B2Improve usabilityImprove monitoring accuracyElectrical controlFuel injection apparatusLimit valueControl theory

A method and an arrangement for controlling a drive unit are suggested wherein a maximum permissible value of an output quantity is determined. This maximum permissible value is compared to the actual value and, when the permissible value is exceeded by the actual value, reaction measures are initiated. The maximum permissible value is filtered at least in one operating state in accordance with filter means including a filter and a dead zone member. Furthermore, the maximum permissible value is continuously reduced in dependence upon the approaching of at least one quantity to a limit value. This quantity represents an operating state.

Owner:ROBERT BOSCH GMBH

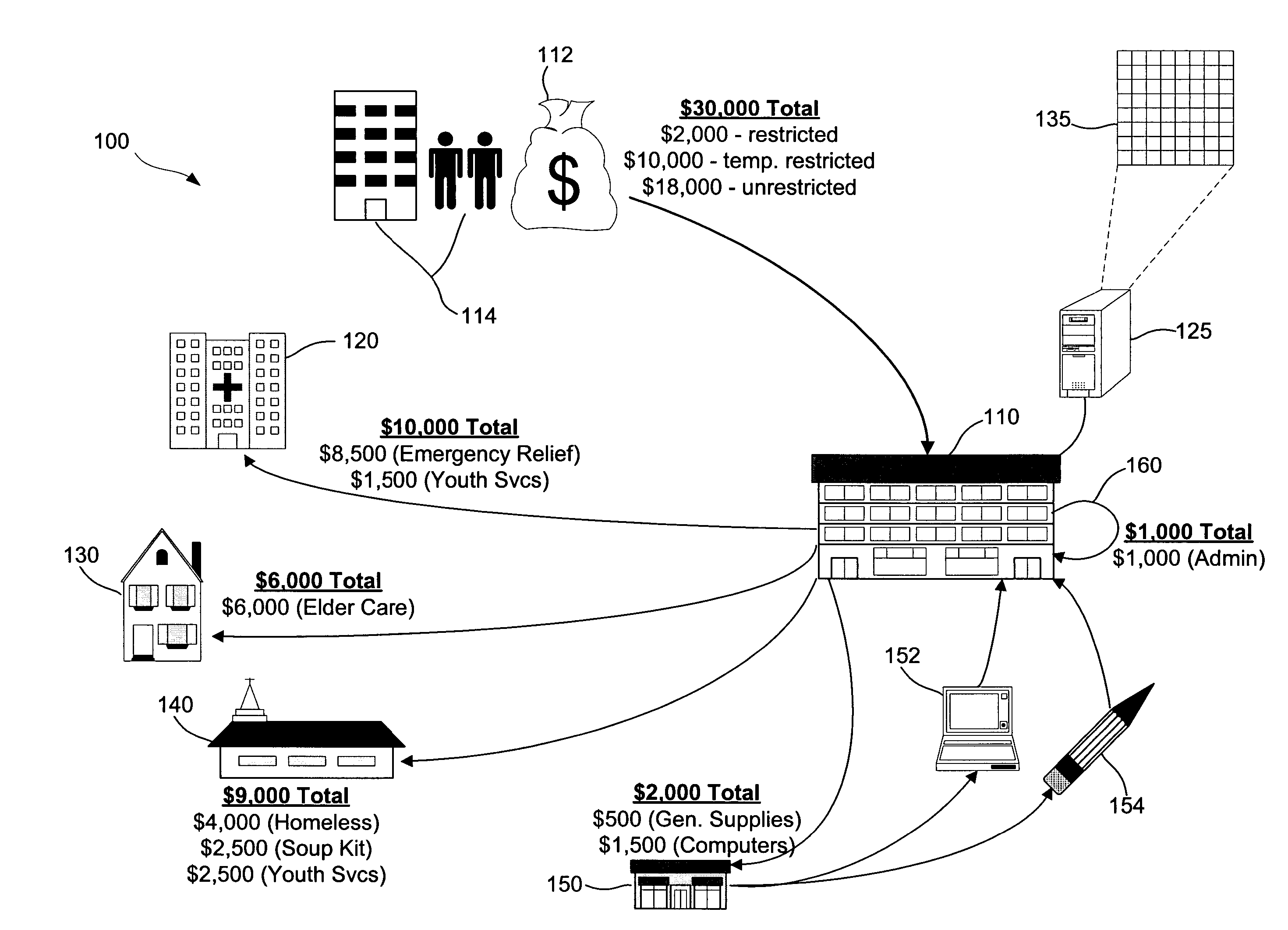

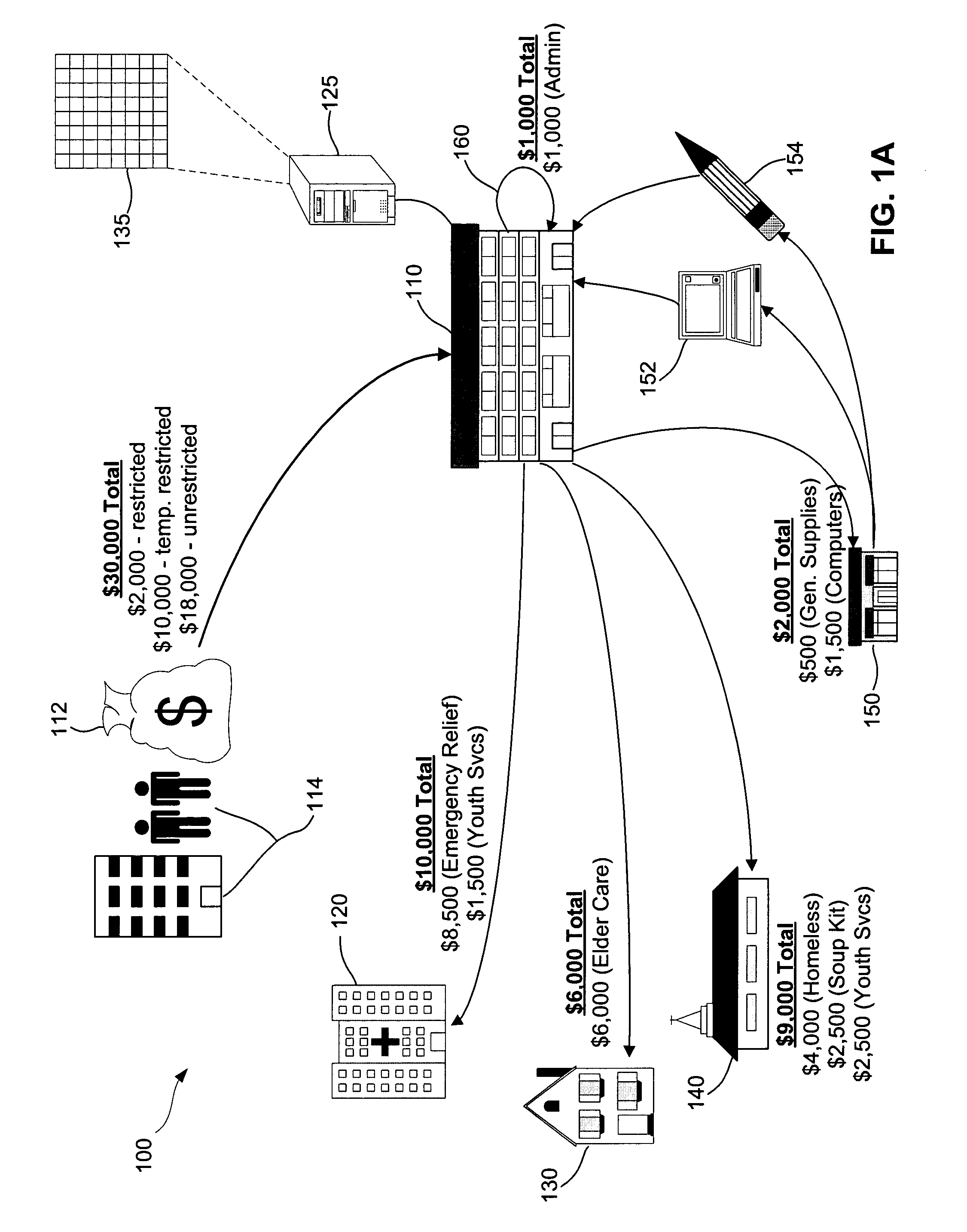

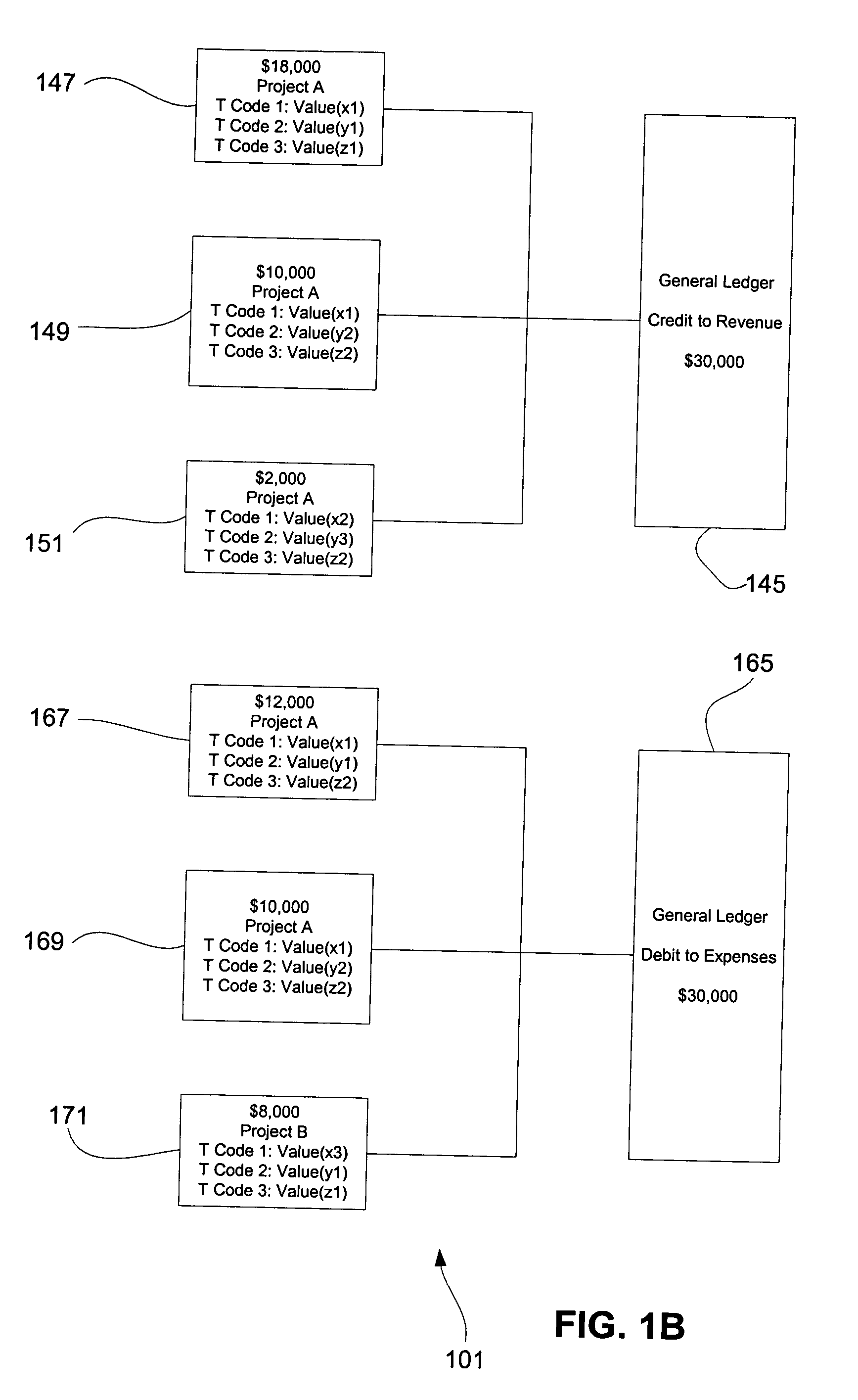

Method for tracking transactions in a not-for-profit accounting system

In a computerized accounting system, a method of tracking and analyzing financial transaction information associated with accounts, without the need for addition account segments to define the account number of each account, includes defining at least one transaction code, each transaction code having a plurality of permissible values, receiving a transaction having an amount and being associated with an account, and associating the transaction with a project and with a value from the plurality of permissible values for the at least one transaction code. Another method includes subdividing the total amount of the transaction into two or more portions, each portion being associated with a project and with respective values of the permissible values for a plurality of transaction codes. Use of the transaction codes results in improved reporting and enhanced data analysis.

Owner:BLACKBAUD

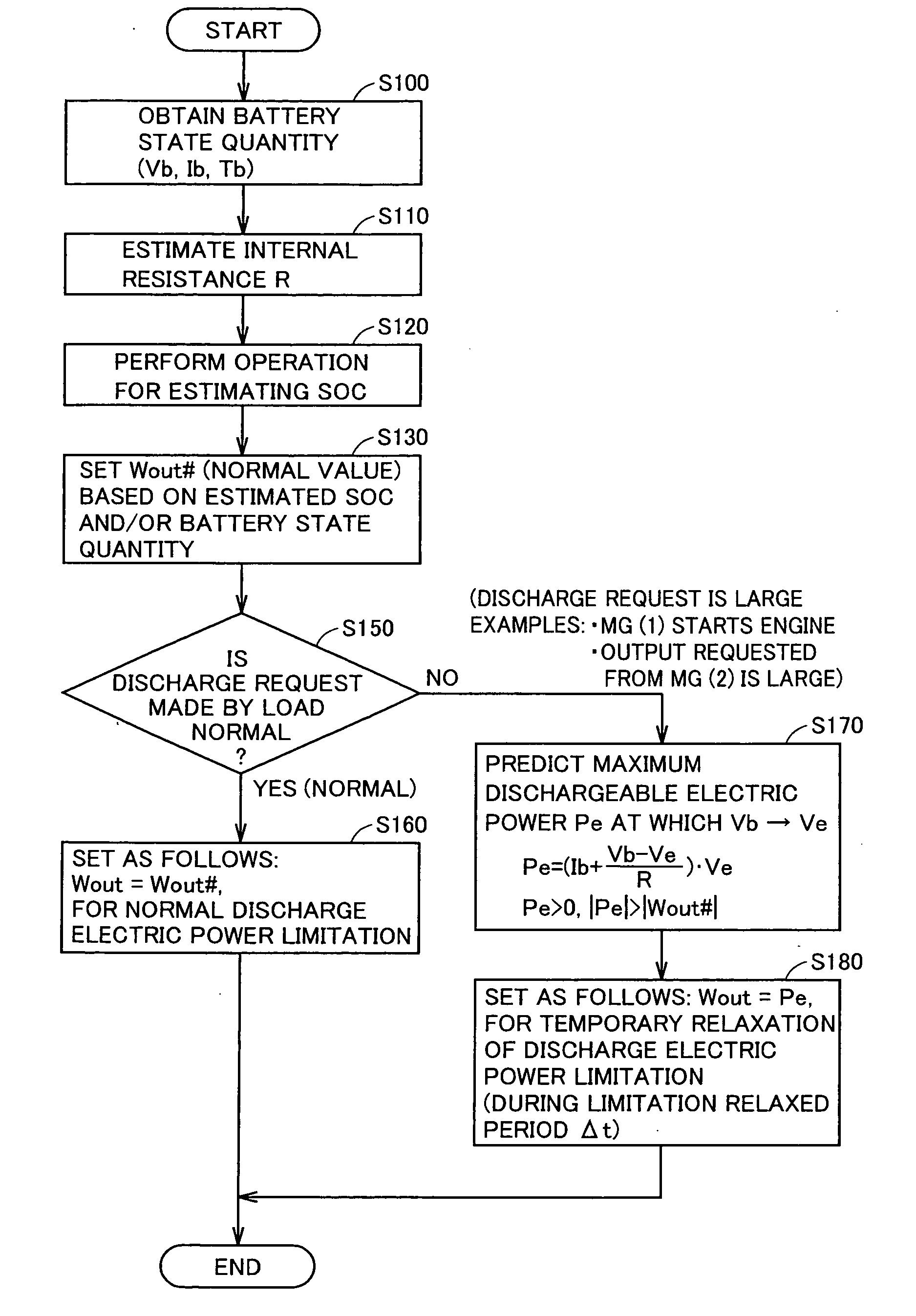

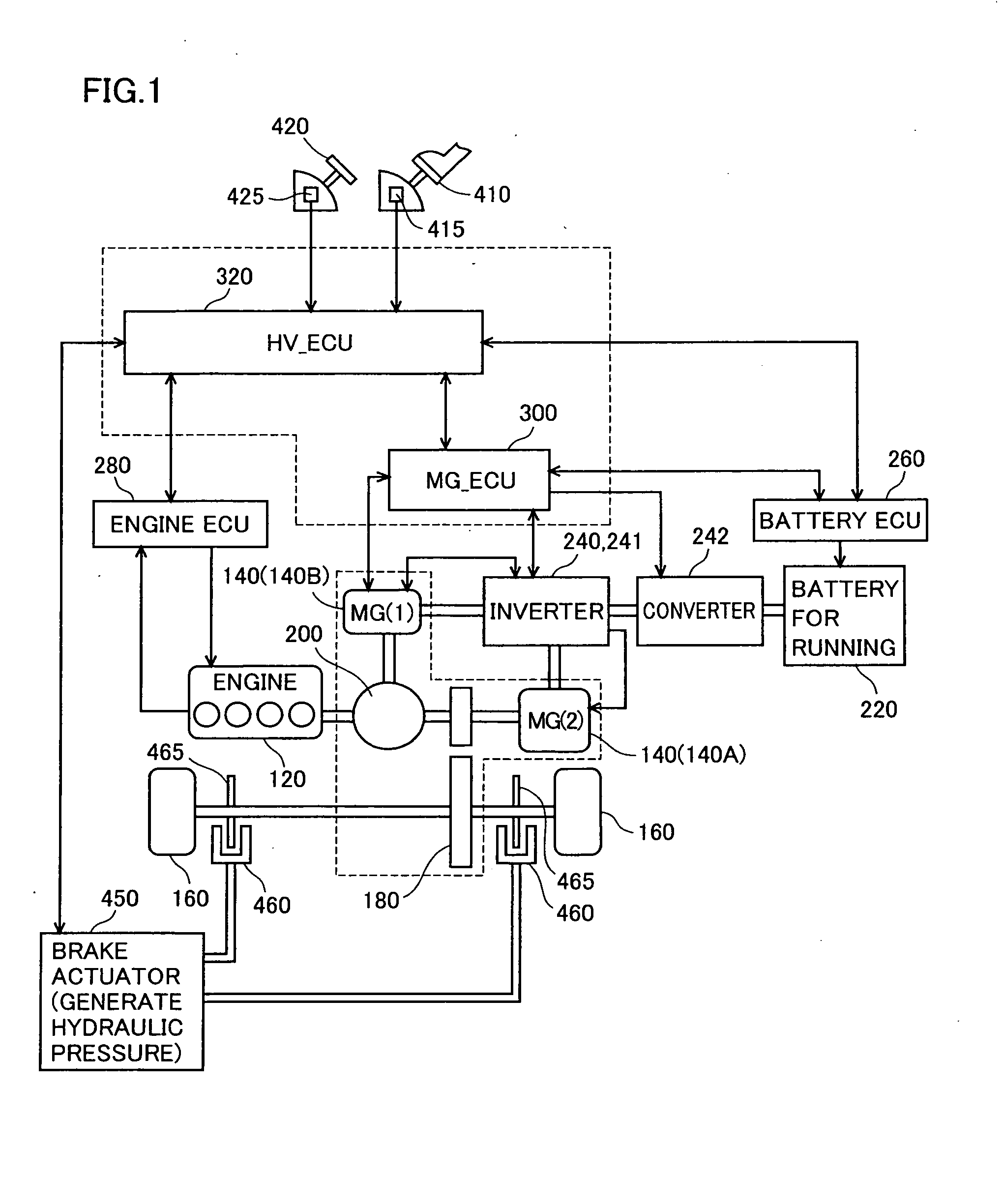

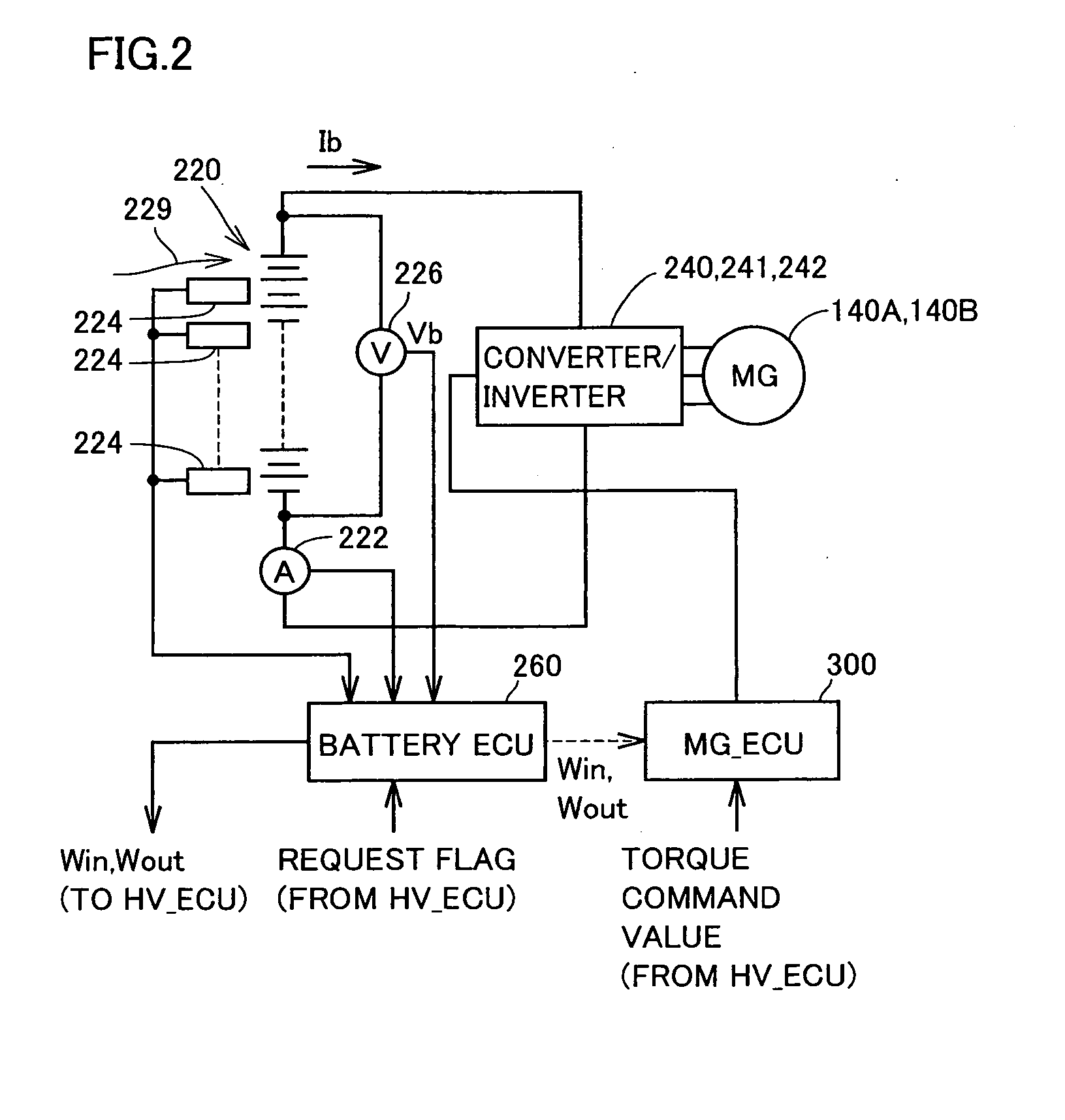

Charge/Discharge Control Device and Charge/Discharge Control Method for Power Storage Device, and Electric-Powered Vehicle

InactiveUS20090266631A1Suppress chargingAccurate settingSecondary cells charging/dischargingPlural diverse prime-mover propulsion mountingLower limitElectrical resistance and conductance

A maximum dischargeable current Idmax obtained when electric power output from a battery is increased from a battery current Ib and a battery voltage Vb at present under internal resistance R at present (an operating point 510) until the battery voltage reaches a lower limit voltage Ve (an operating point 520), is shown as follows: Idmax=Ib+(Vb−Ve) / R. Therefore, in accordance with multiplication of the lower limit voltage Ve and the maximum dischargeable current Idmax, it is possible to predict maximum dischargeable electric power at which the battery voltage does not become lower than the lower limit voltage even if discharge limitation is temporarily relaxed, as a relative value with respect to the battery voltage and the battery current at present. When the discharge electric power limitation for the battery (the power storage device) is temporarily relaxed in accordance with a discharge request made by a load, a discharge electric power permissible value is set to correspond to the maximum dischargeable electric power, such that the output voltage of the power storage device does not fall outside a controlled voltage range from the lower limit voltage to an upper limit voltage.

Owner:TOYOTA JIDOSHA KK

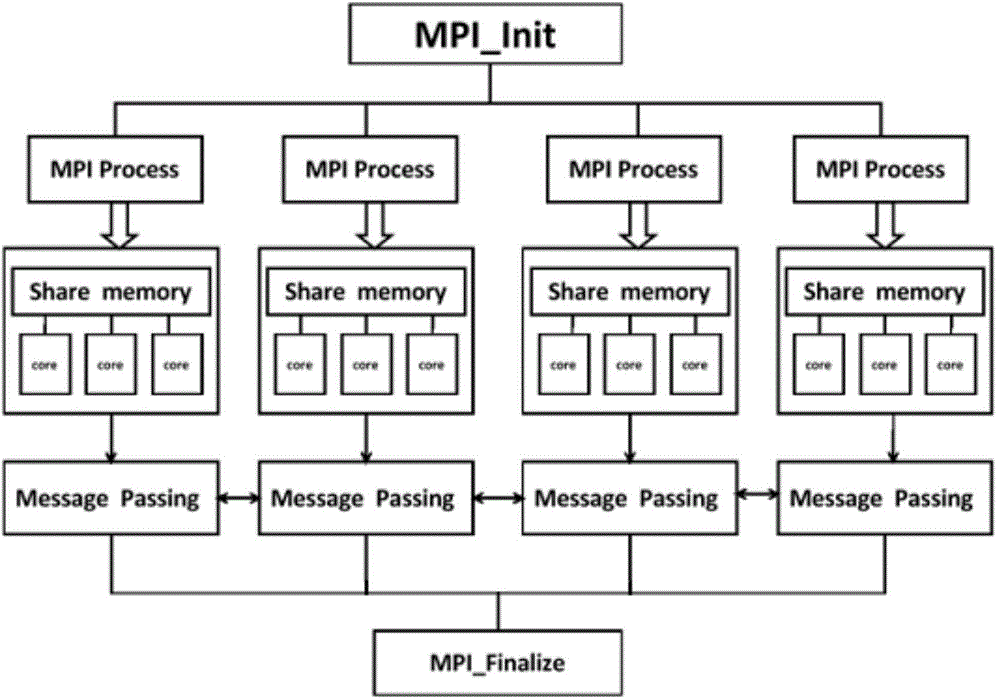

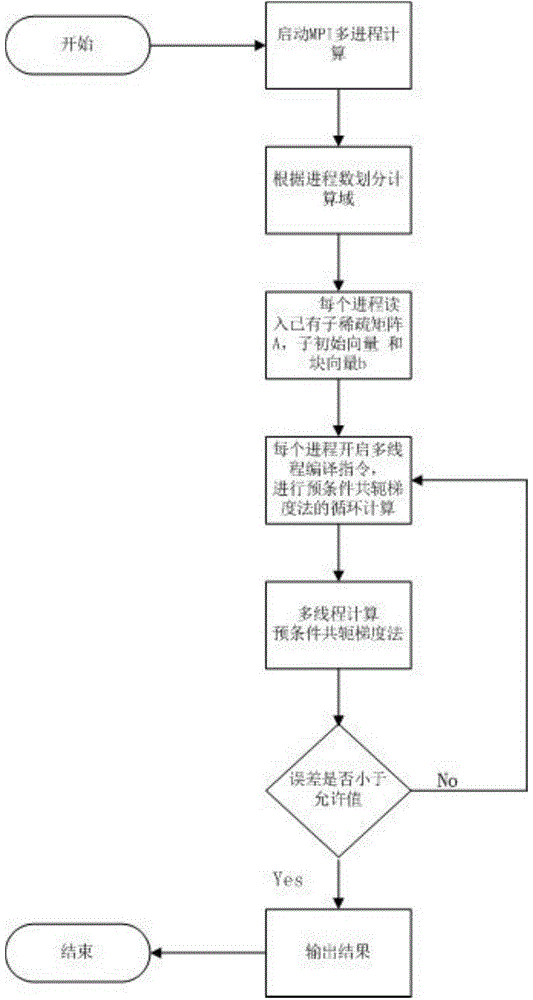

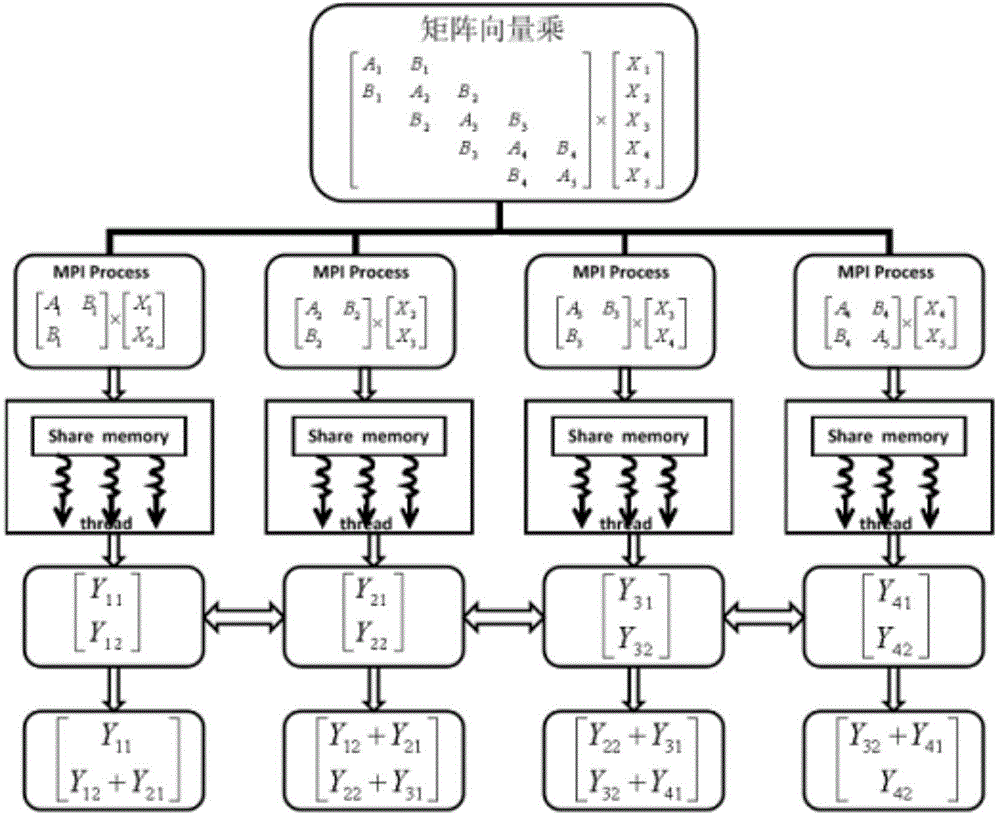

Method for increasing computing speed through parallel computing based on MPI and OpenMP hybrid programming model

ActiveCN104461466AAvoid interactionCalculation speedConcurrent instruction executionNODALHybrid programming

The invention discloses a method for increasing the computing speed through parallel computing based on an MPI and OpenMP hybrid programming model. The method includes the steps that the callable MPI process number and OpenMP thread number are determined according to the computing node number and the available CPU core number in nodes; an existing sub sparse matrix A, the sub initial vector x0, the block vector b and the maximum computing tolerance Tolerance are read into each process; a multi-thread compiling command is enabled for each process; cycle computing of a precondition conjugate gradient method is conducted on all the processes; if the computed error is smaller than the permissible value, cycle computing is ended, and otherwise, cycle computing is continuously conducted; computing results of all the processes are reduced, and a solution of a problem is output; when parallel computing is conducted, MPI processes are started, multi-thread resolving is conducted on the problem, parallel computing among the nodes is started, all the MPI processes are distributed to one computing node, and information is exchanged through message transmission among the processes; then in all the MPT processes, an OpenMP guidance command is used to create a set of threads, and the threads are distributed to different processors of the computing node to be executed.

Owner:INST OF SOFTWARE APPL TECH GUANGZHOU & CHINESE ACAD OF SCI

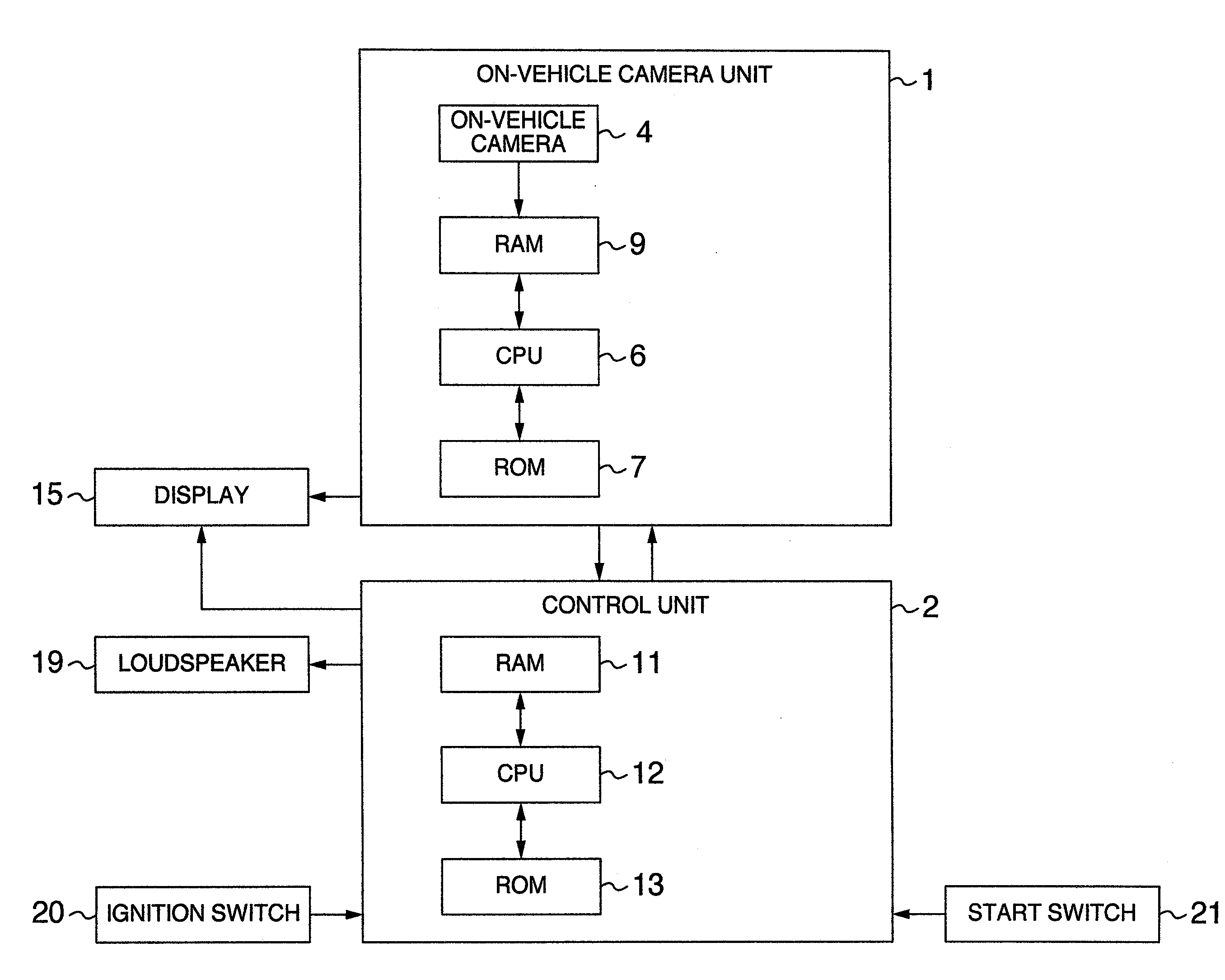

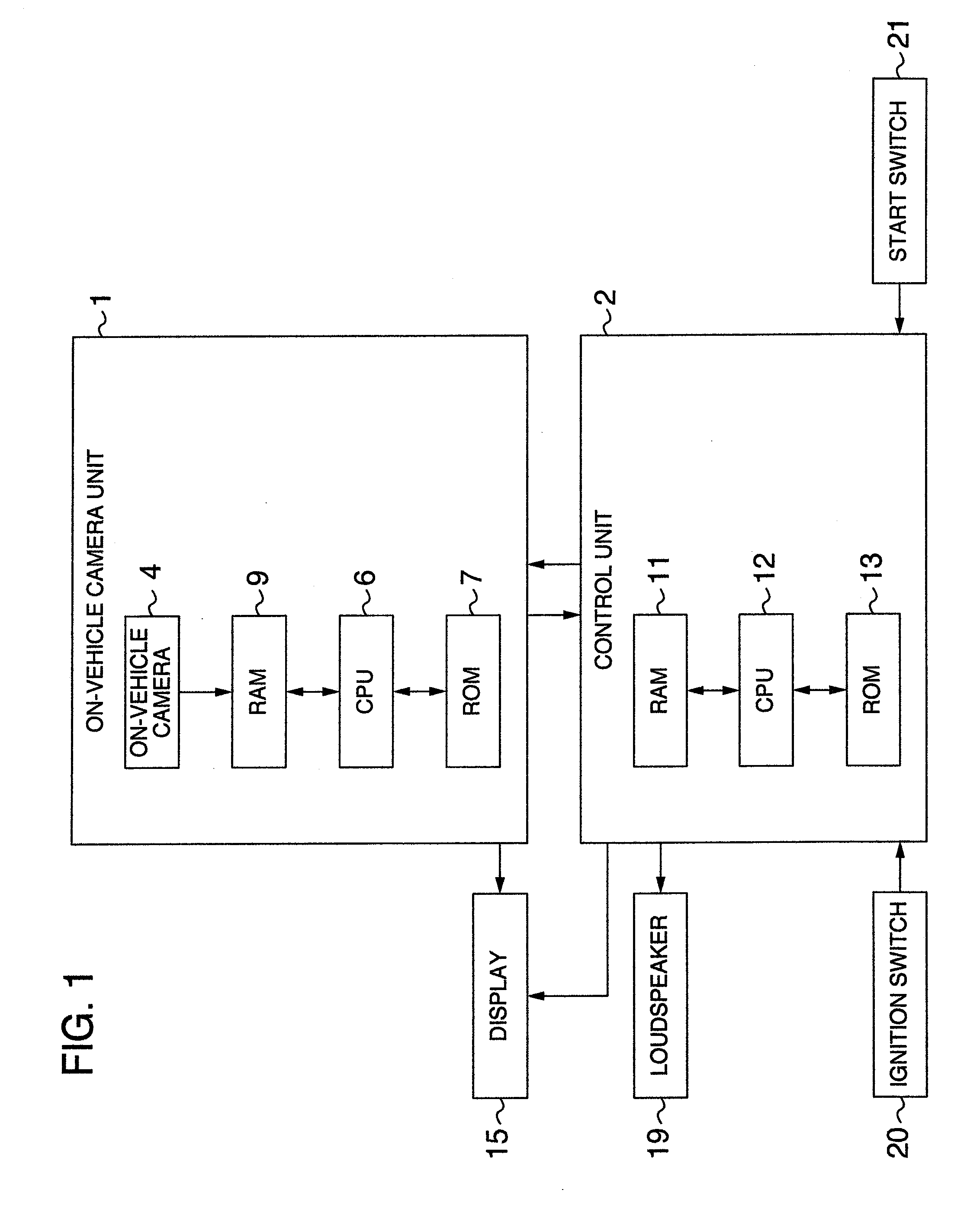

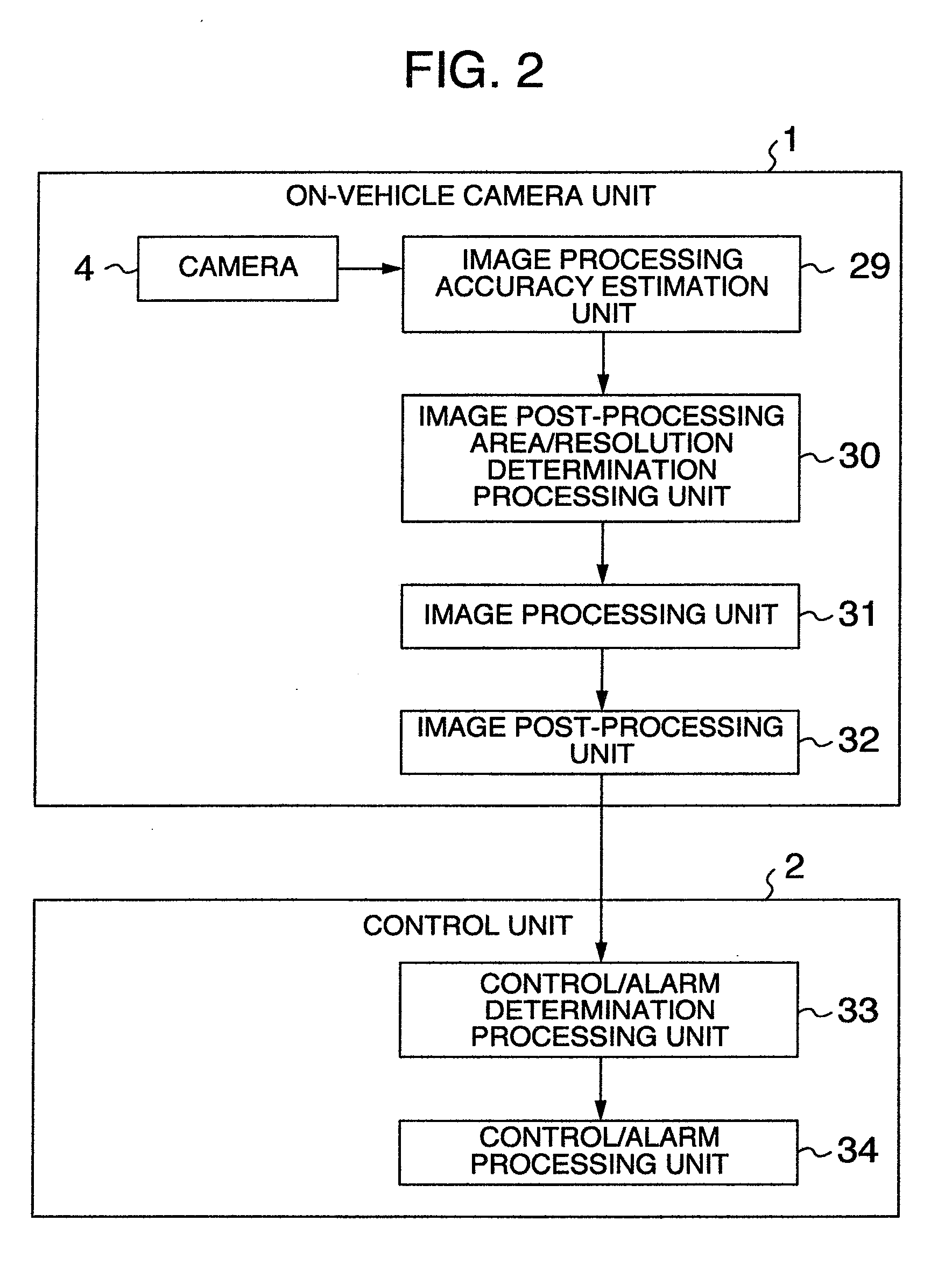

Image Processing Apparatus

ActiveUS20090316956A1Shorten the timeEasy to detectScene recognitionOptical signallingImaging processingImage post processing

An image processing accuracy estimation unit estimates an image processing accuracy by calculating a size of an object by which the accuracy of measurement of the distance of the object photographed by an on-vehicle camera becomes a permissible value or less. An image post-processing area determination unit determines, in accordance with the estimated image processing accuracy, a partial area inside a detection area of the object as an image post-processing area for which an image post-processing is carried out and lattices the determined image post-processing area to cells. An image processing unit processes the image photographed by the on-vehicle camera to detect a candidate for object and calculates a three-dimensional position of the detected object candidate. An image post-processing unit calculates, in each the individual cell inside the determined area the probability as to whether the detected object is present and determines the presence / absence of the object.

Owner:HITACHI LTD

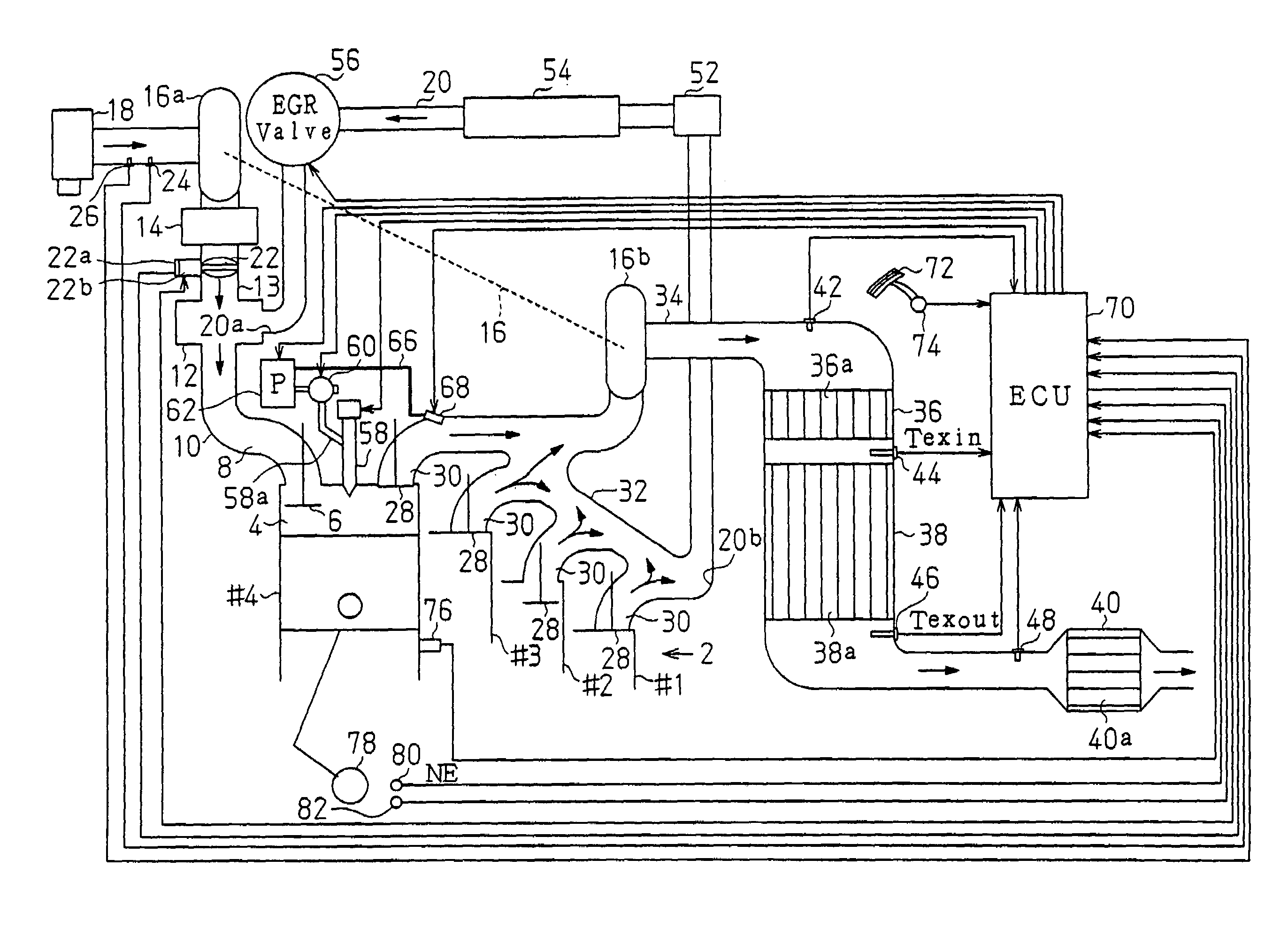

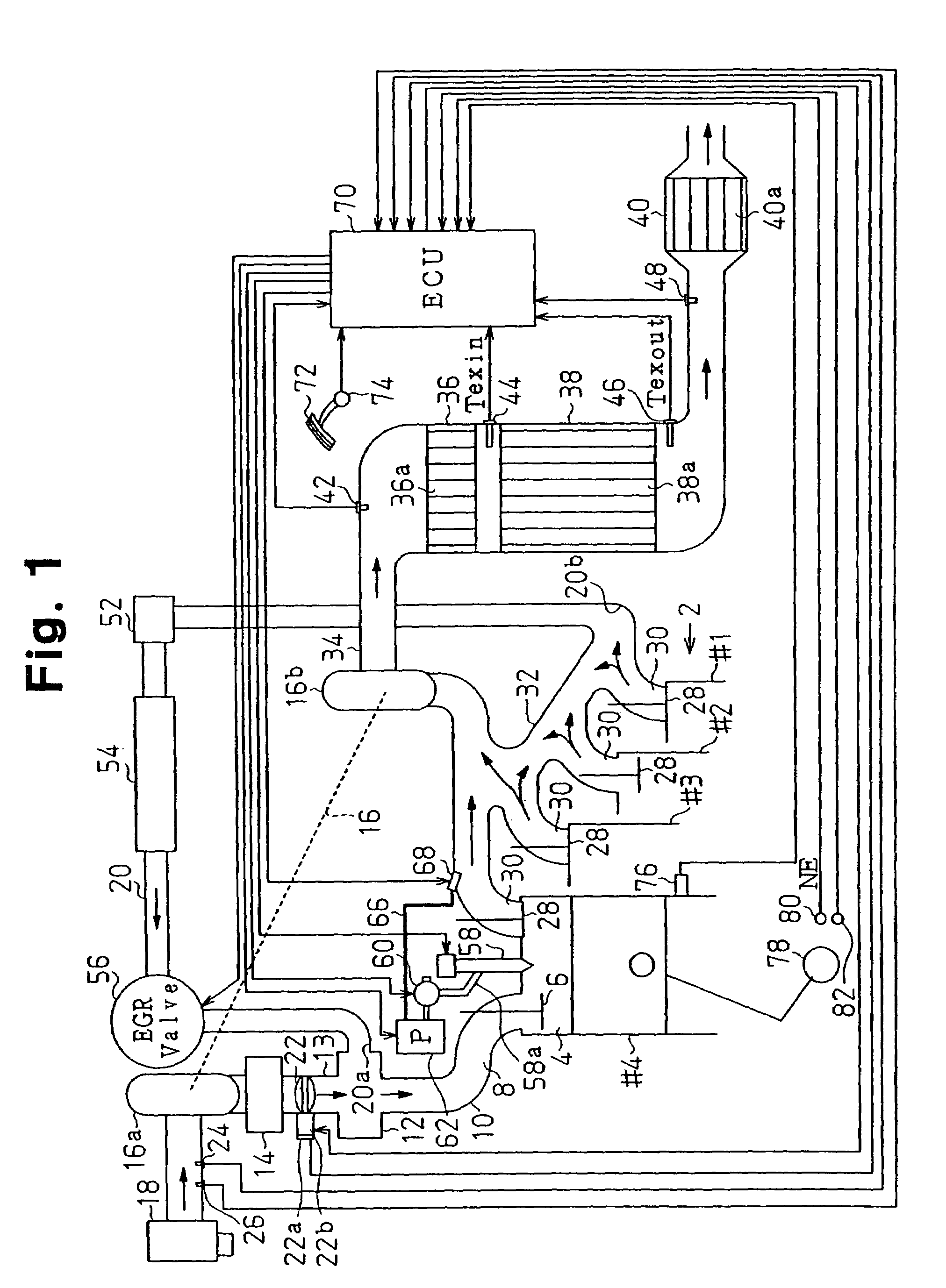

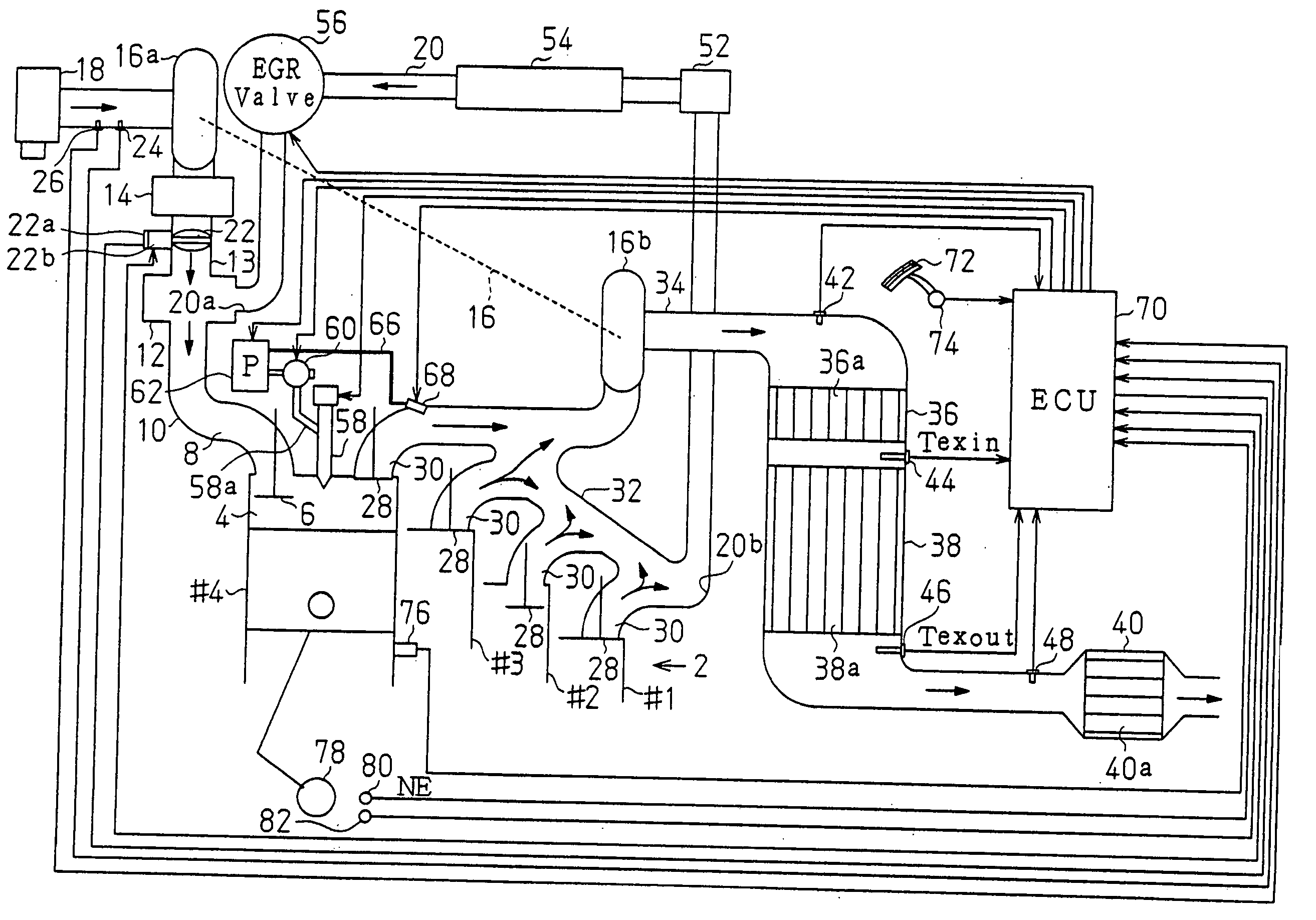

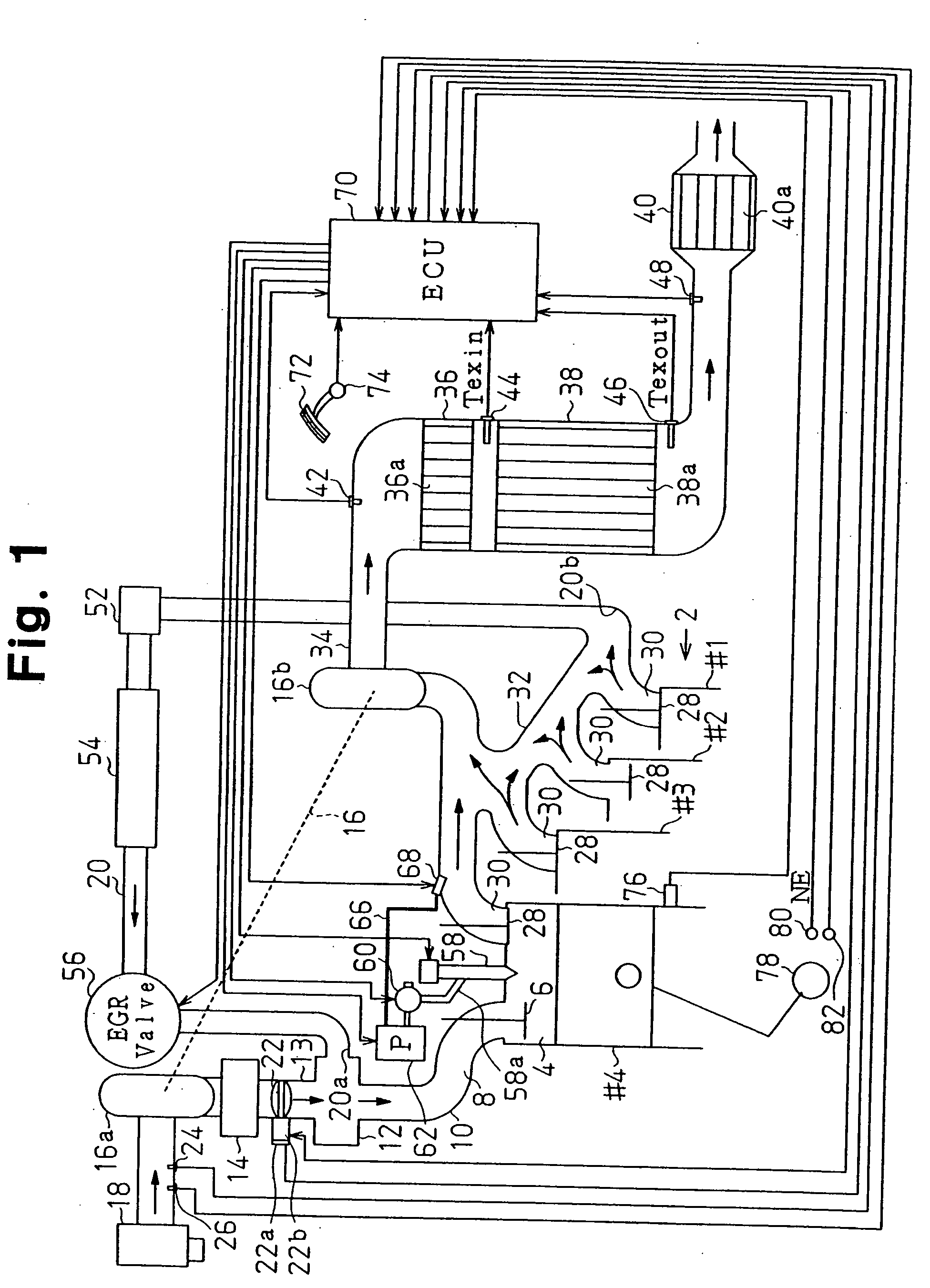

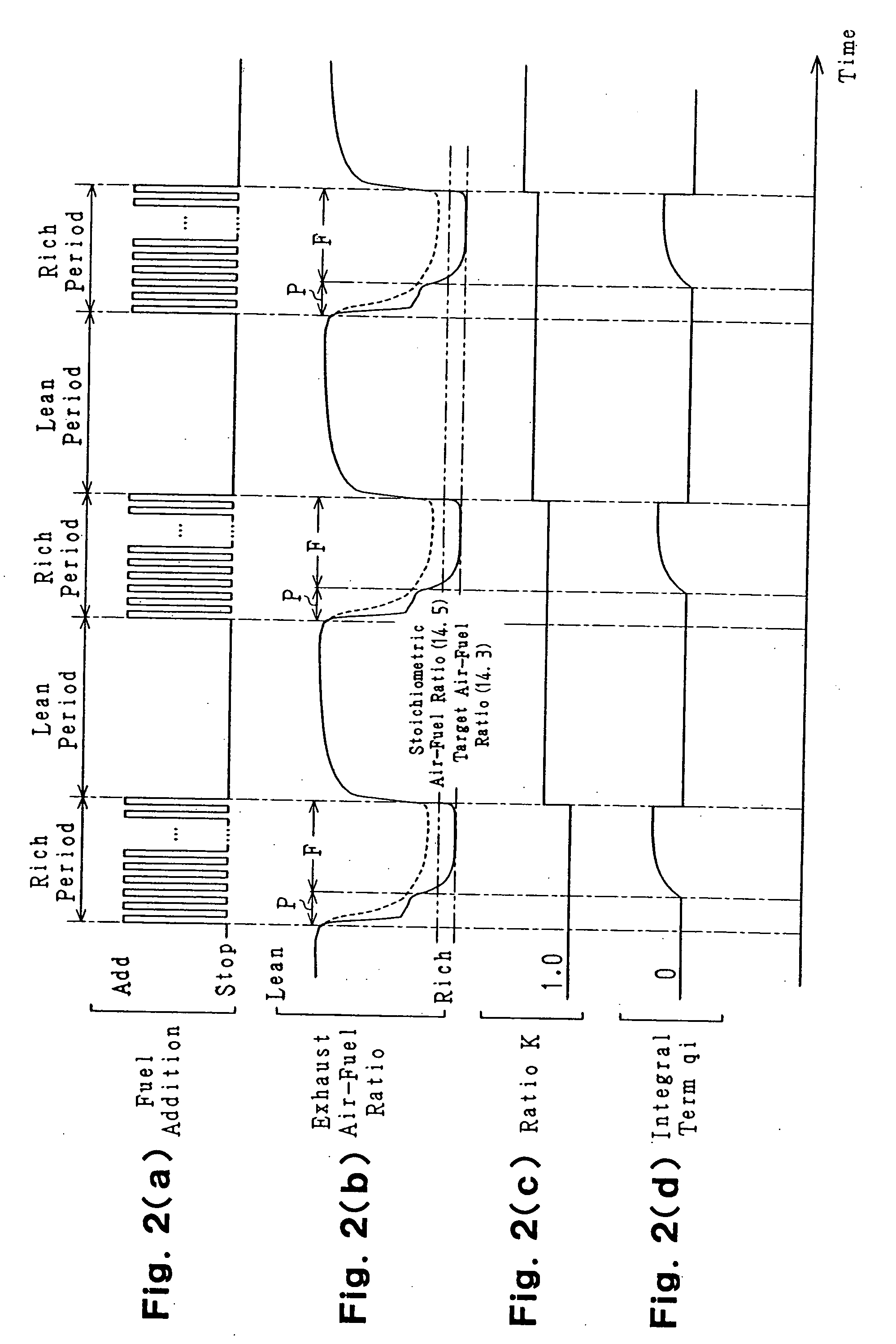

Exhaust purifying apparatus and exhaust purifying method for internal combustion engine

ActiveUS7299625B2Electrical controlNon-fuel substance addition to fuelSulfurExternal combustion engine

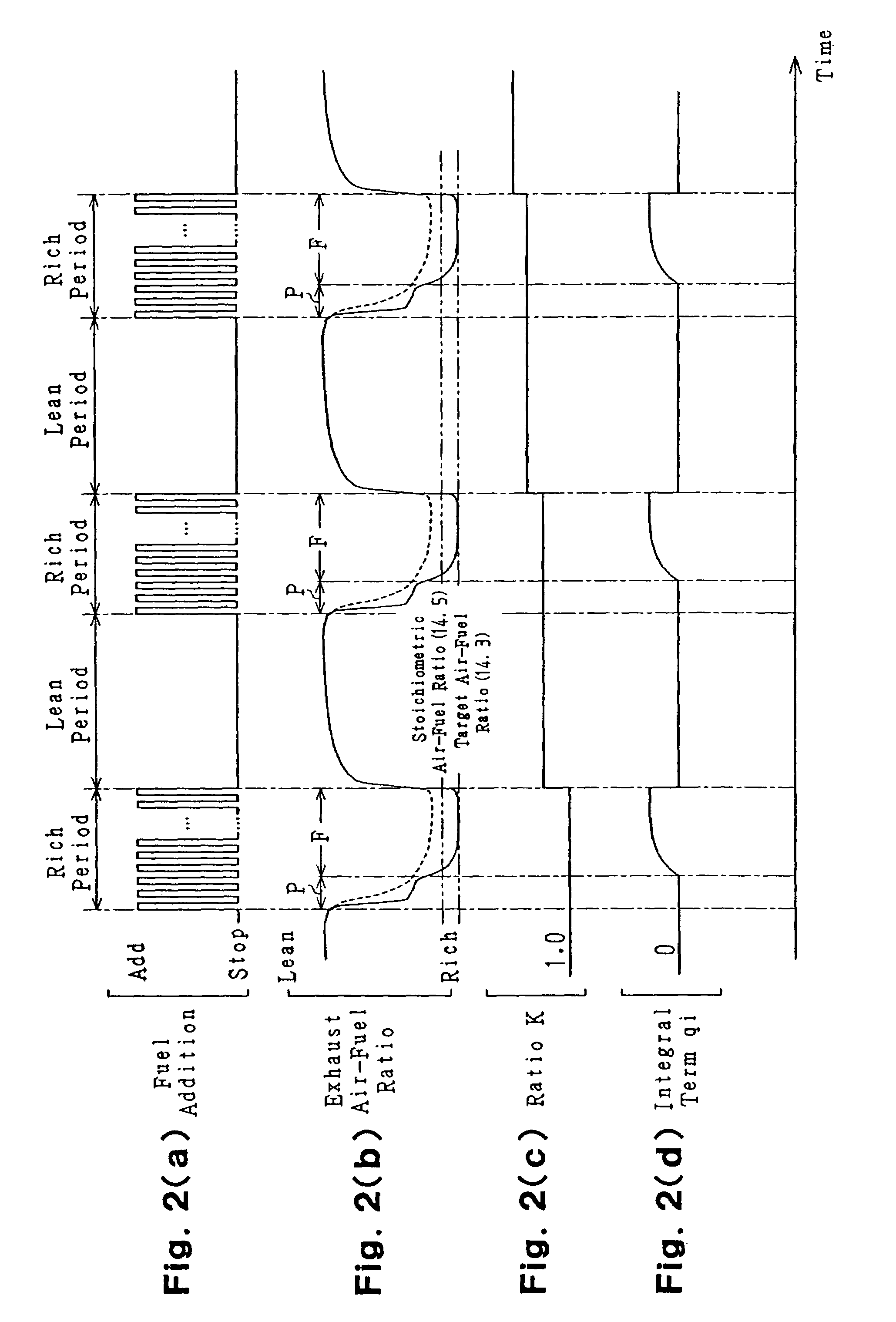

During sulfur release control in an internal combustion engine, a rich period and a lean period are alternately repeated. The air-fuel ratio of exhaust gas is controlled toward a target air-fuel ratio (14.3) by adding fuel from a fuel adding valve in the rich period. An ECU determines whether the actual air-fuel ratio of exhaust gas detected by an air-fuel ratio sensor has reached a stoichiometric air-fuel ratio each time the rich period ends at which addition of fuel from the fuel adding valve is stopped. A counter counts the number of times the ECU has determined that the actual air-fuel ratio of exhaust gas has not reached the stoichiometric air-fuel ratio. When the value of the counter becomes greater than or equal to a permissible value, the ECU determines that there is an abnormality in the sulfur release control.

Owner:TOYOTA JIDOSHA KK

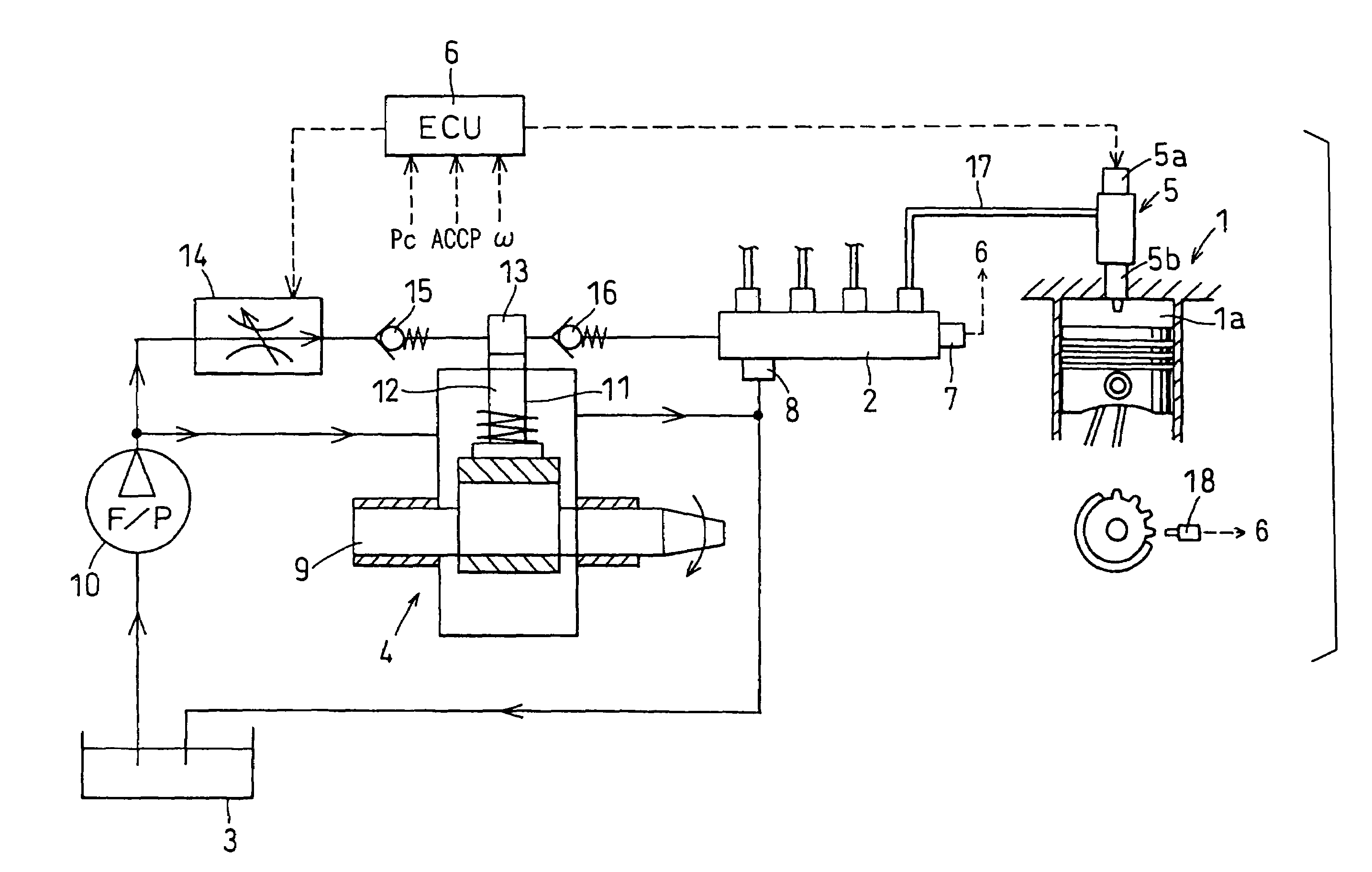

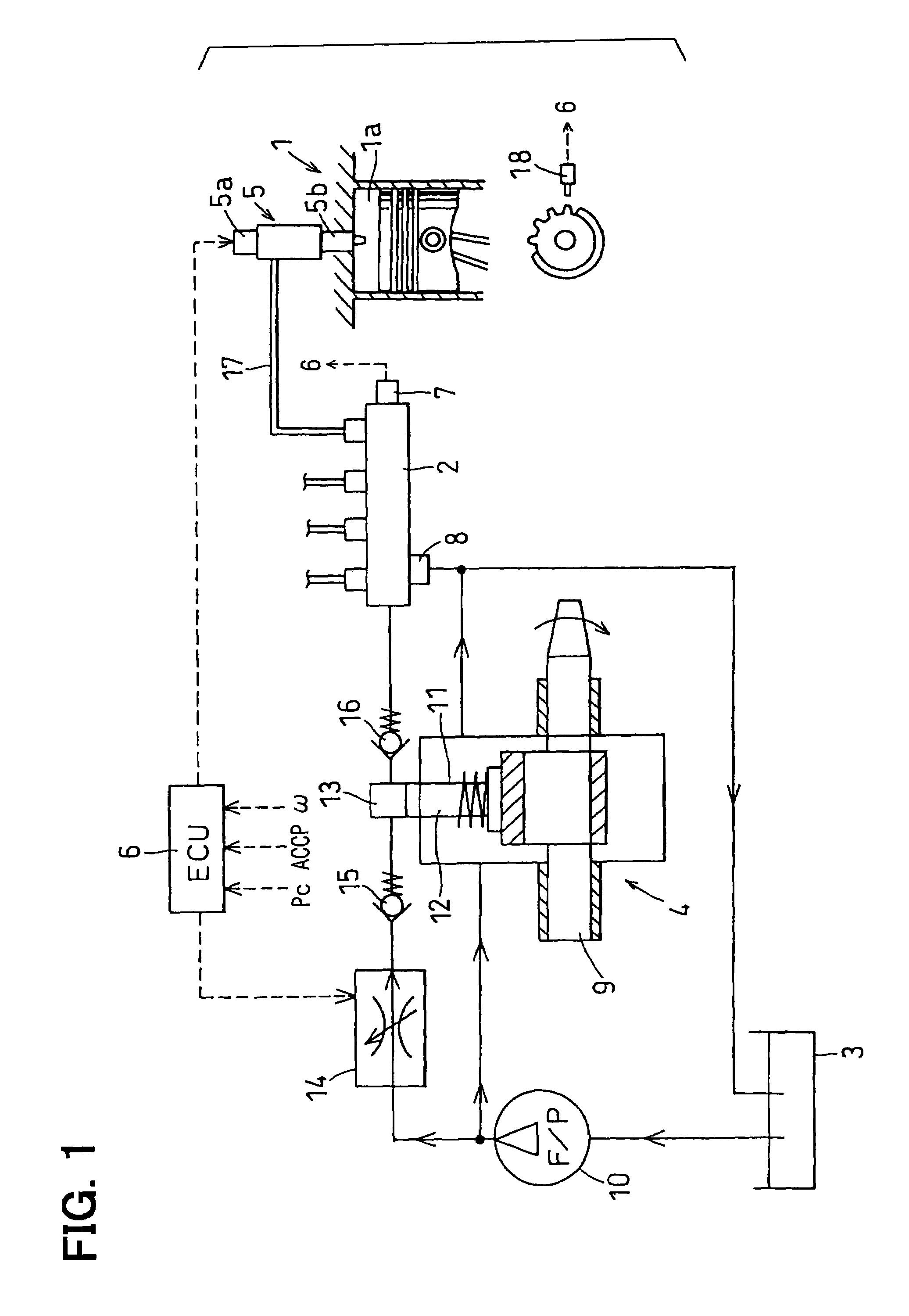

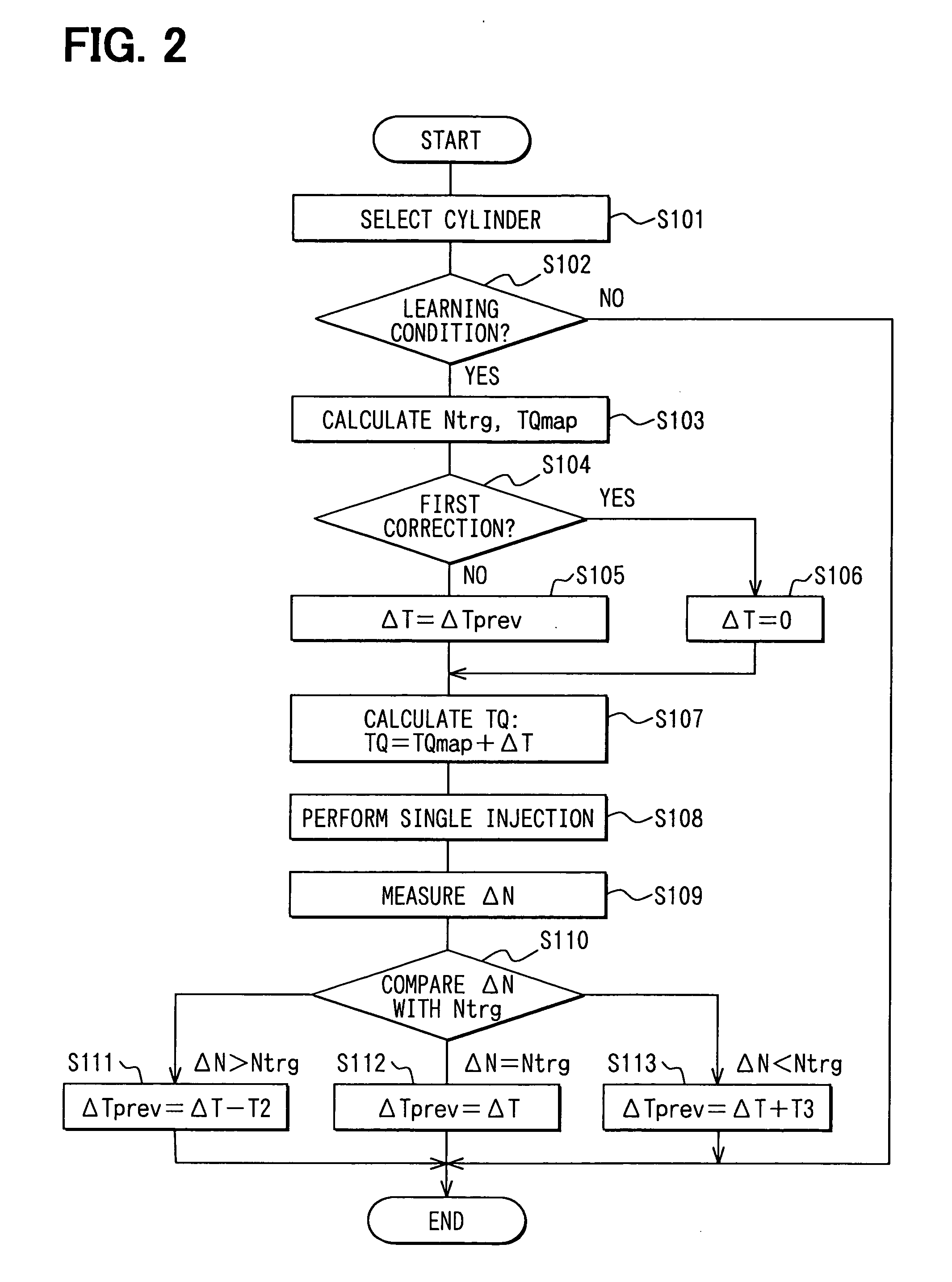

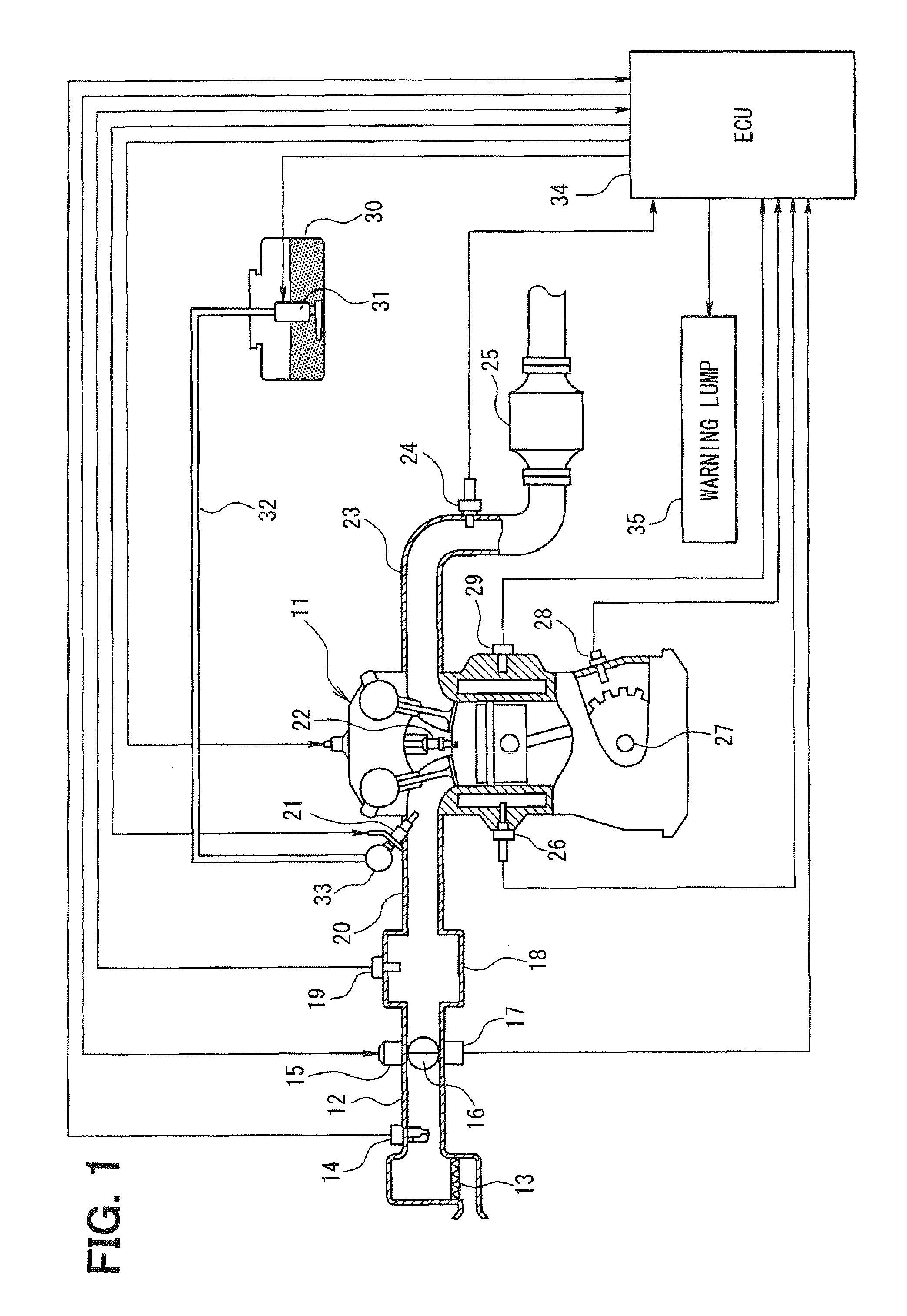

Injection control system of internal combustion engine

ActiveUS6988030B2Shorten the overall cycleAvoid emissionsAnalogue computers for vehiclesElectrical controlState variationControl system

Owner:DENSO CORP

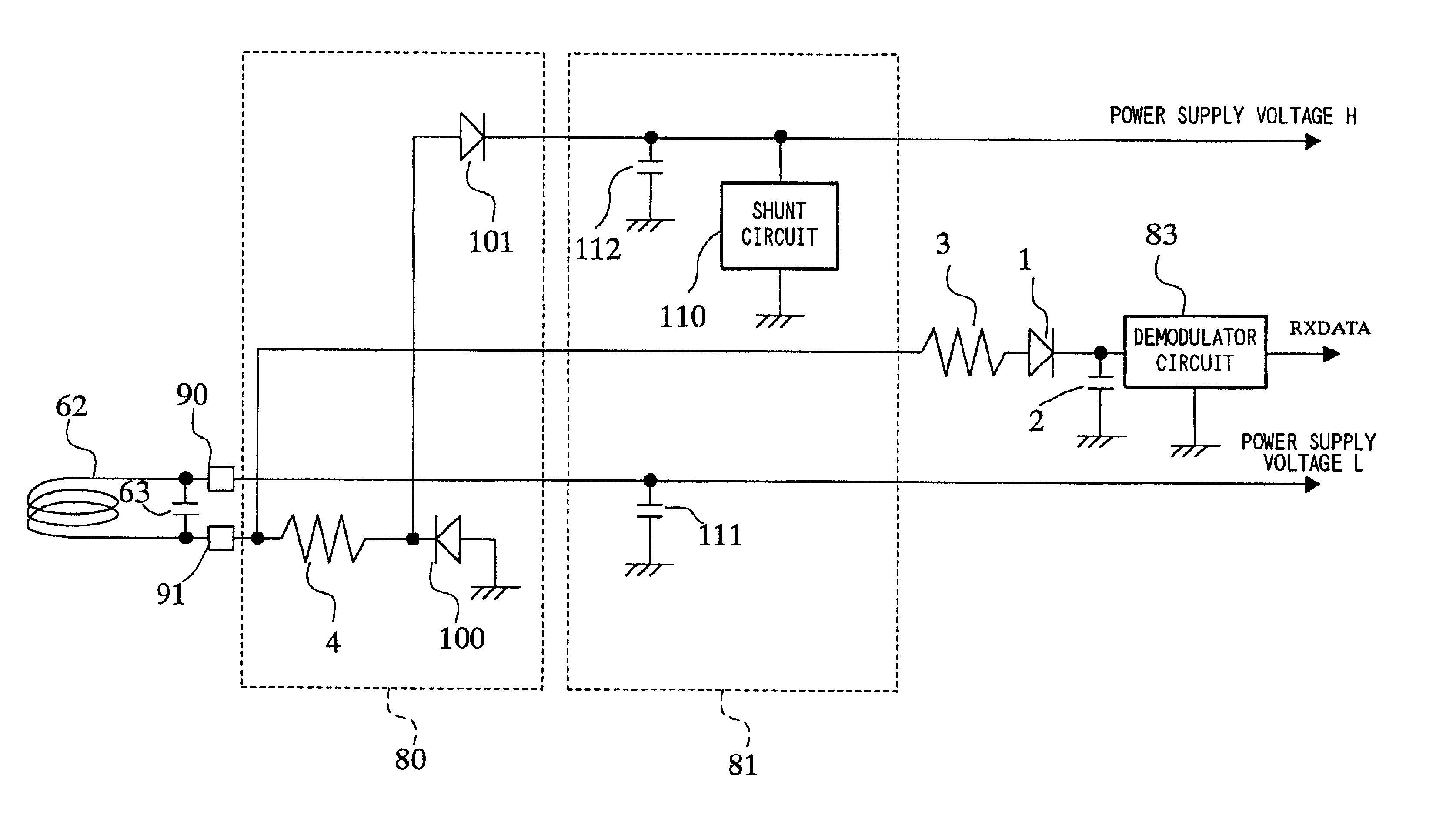

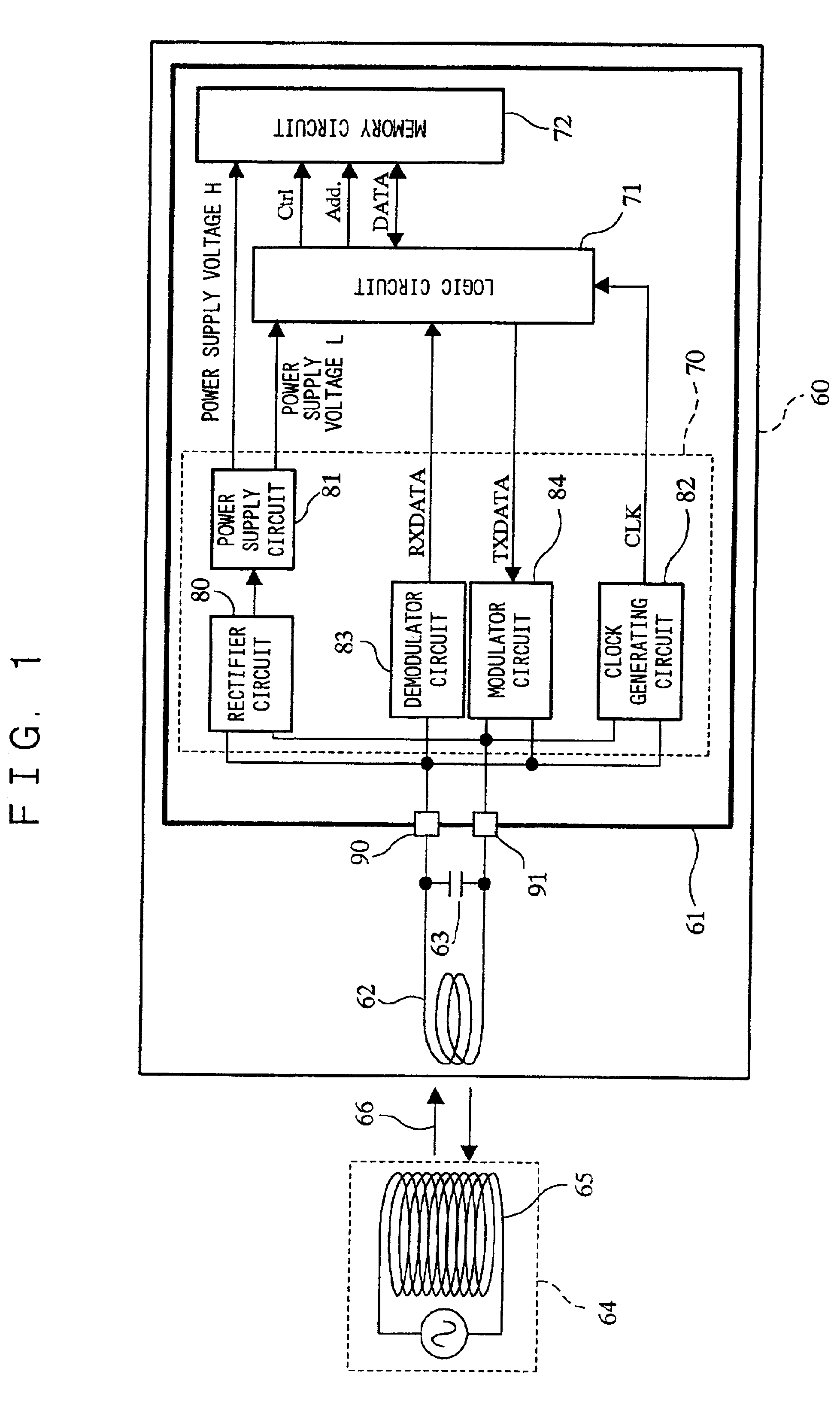

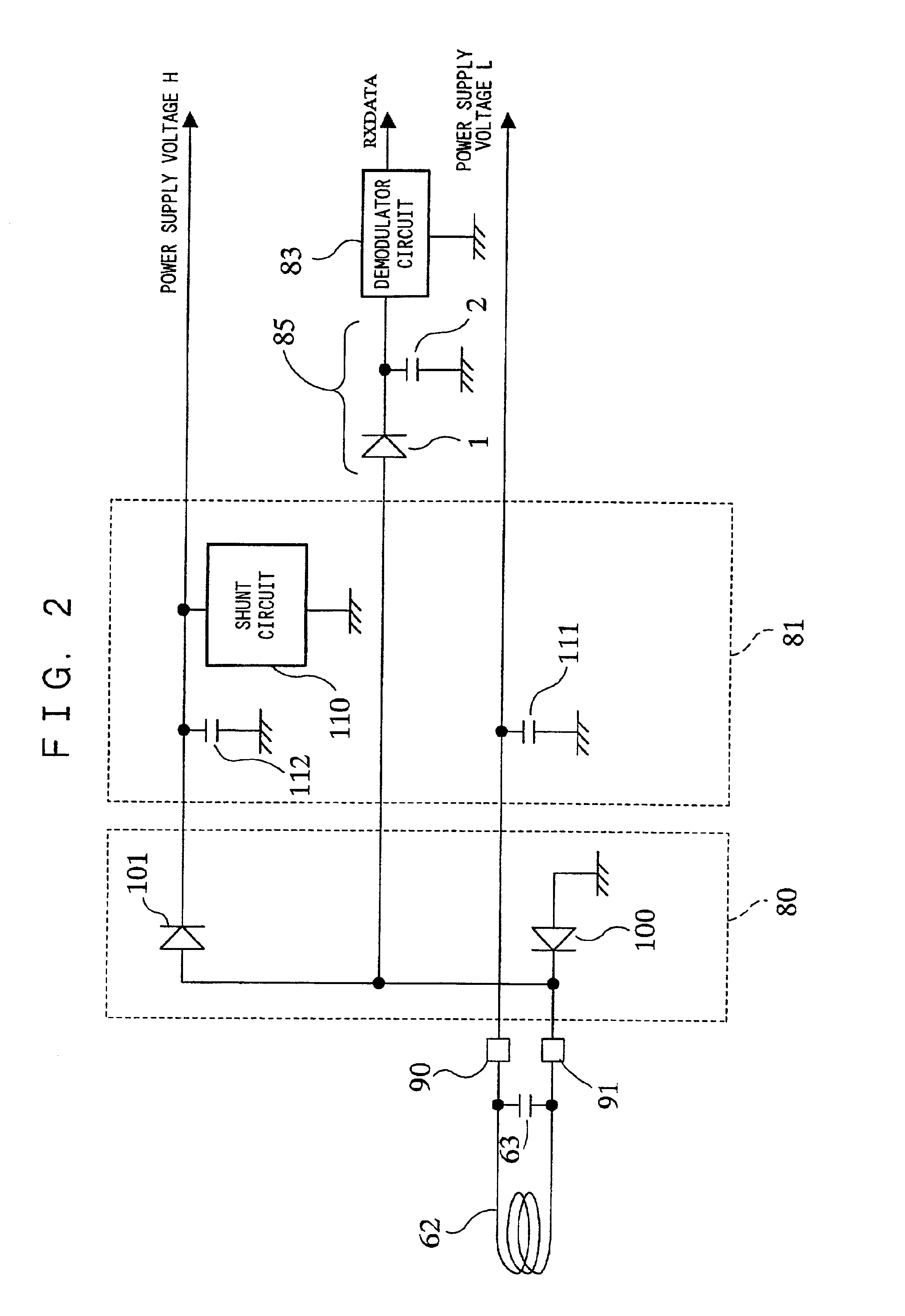

Semiconductor integrated circuit

InactiveUS6848620B2Obtain an IC card with stabilityOther printing matterCo-operative working arrangementsOvervoltageShortest distance

A semiconductor integrated circuit is provided to allow a stable operation even in a short distance where an IC card is in contact with a reader / writer. In a semiconductor integrated circuit for a noncontact IC card that obtains driving power supply by carrying superimposed data, obtained voltage does not become overvoltage and data can be demodulated with stability regardless of a change in communication distance. Inputs of a system (including a rectifier circuit and a power supply circuit) producing power supply from an antenna coil of the IC card which receives radio waves transmitted from a reader / writer, and of a demodulator circuit are connected via a path separated from the output of the rectifier circuit. Thus, a power supply voltage range can be set within a permissible value and a rate of change in input of the demodulator circuit can be obtained regardless whether the communication distance is short or long.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

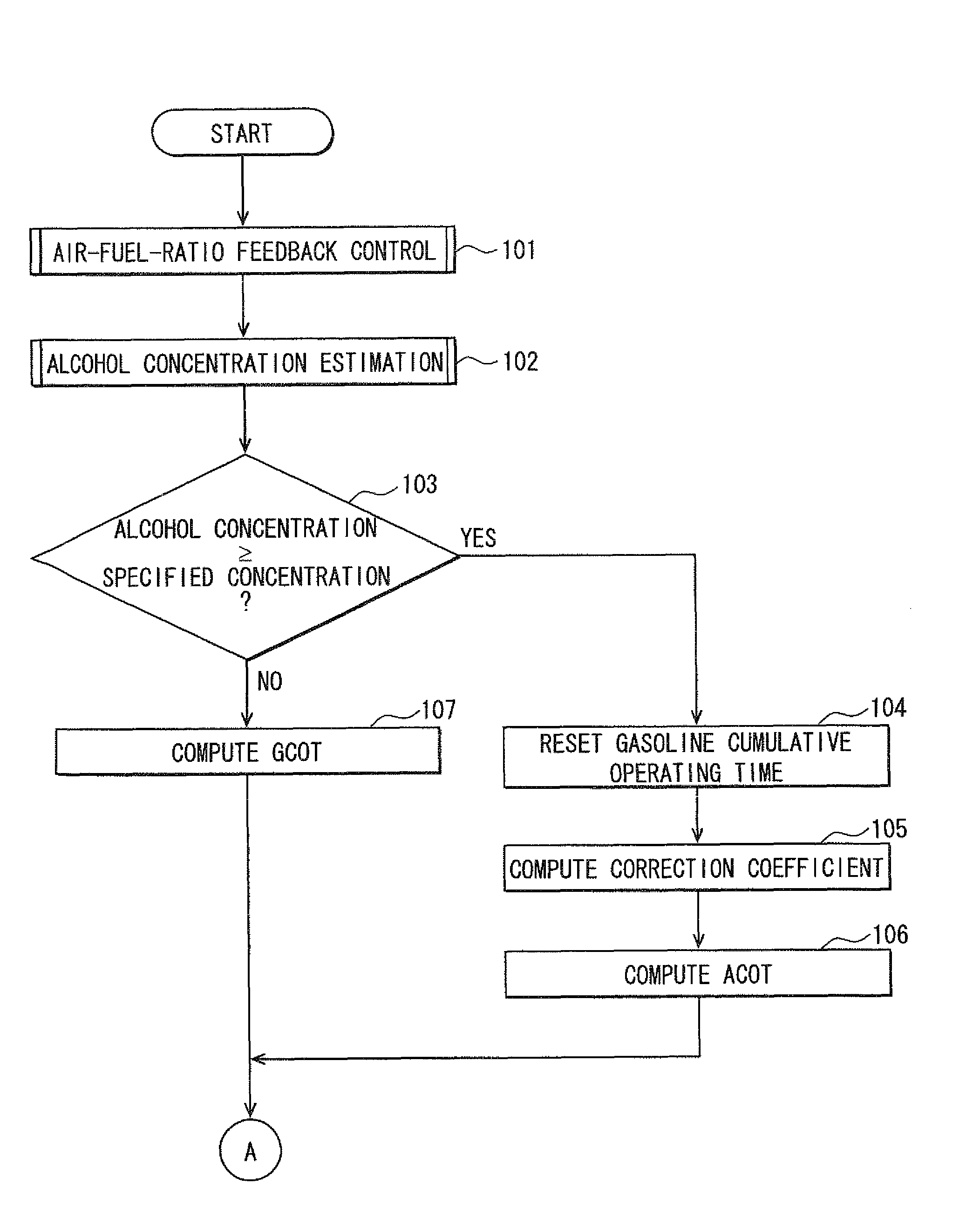

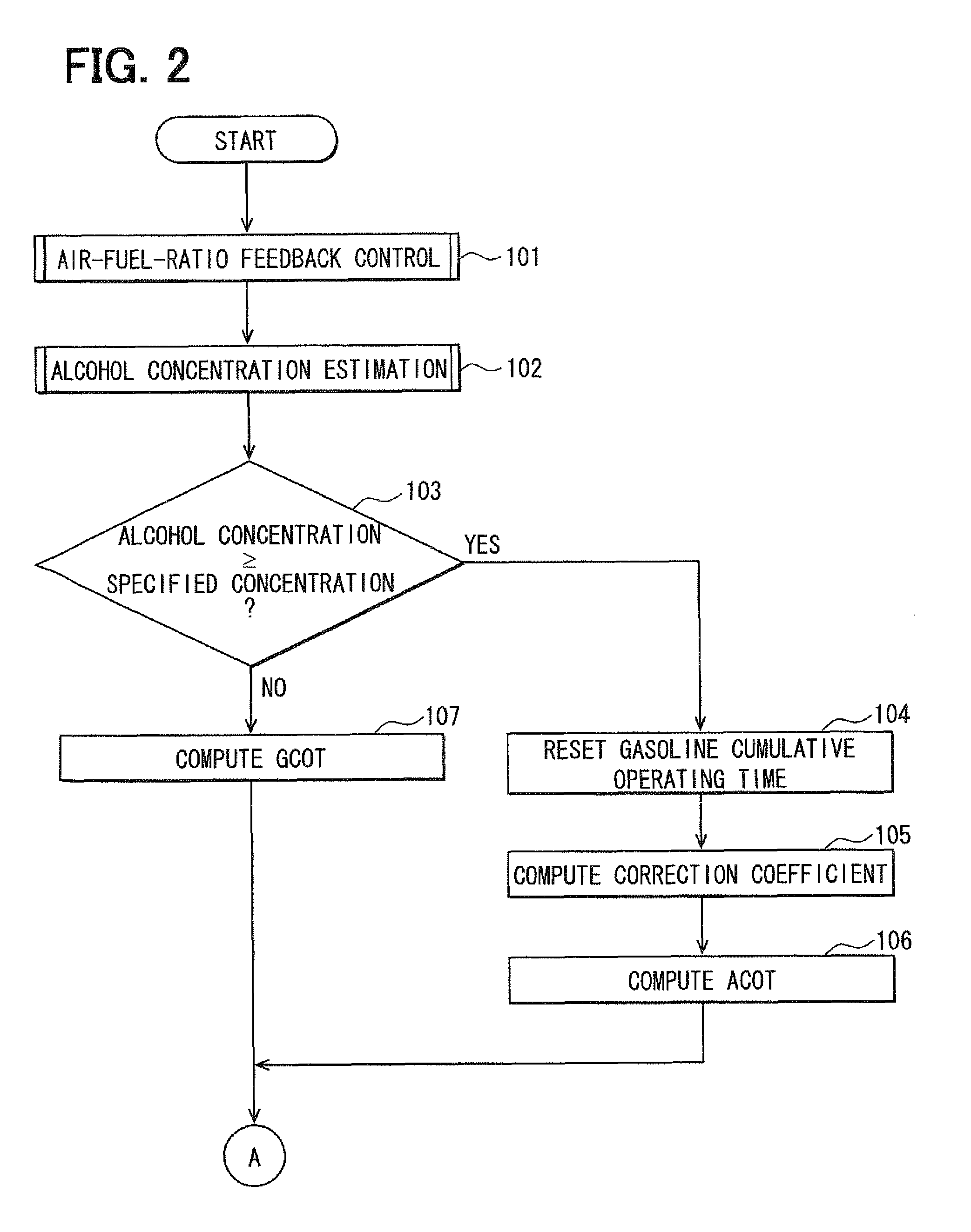

Controller for internal combustion engine

InactiveUS7856966B2Promote accumulationImprove performanceElectrical controlInternal combustion piston enginesFuel tankExhaust gas emissions

When an estimated alcohol concentration is higher than a specified concentration, an operation time of an engine is cumulated to obtain an alcohol cumulative operating time (ACOT). When the ACOT exceeds a specified time and a feedback correction quantity of a fuel injection quantity exceeds a specified quantity, a computer estimates that a deposit quantity exceeds a permissible value to notify the driver to refuel a fuel tank with gasoline. After fueling with gasoline, a cleaning agent contained in the gasoline removes the deposit accumulated on a fuel injector. As a result, a variation in fuel injection quantity due to deposit on the fuel injector can be avoided, and a deterioration in exhaust gas emission and drivability can be avoided.

Owner:DENSO CORP

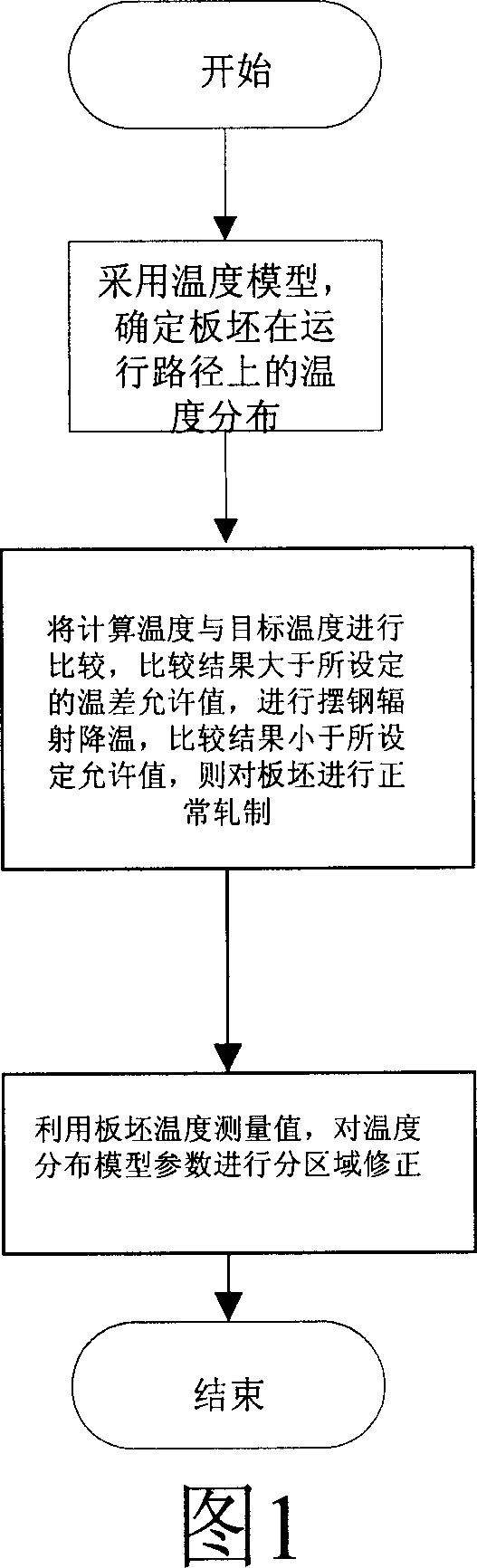

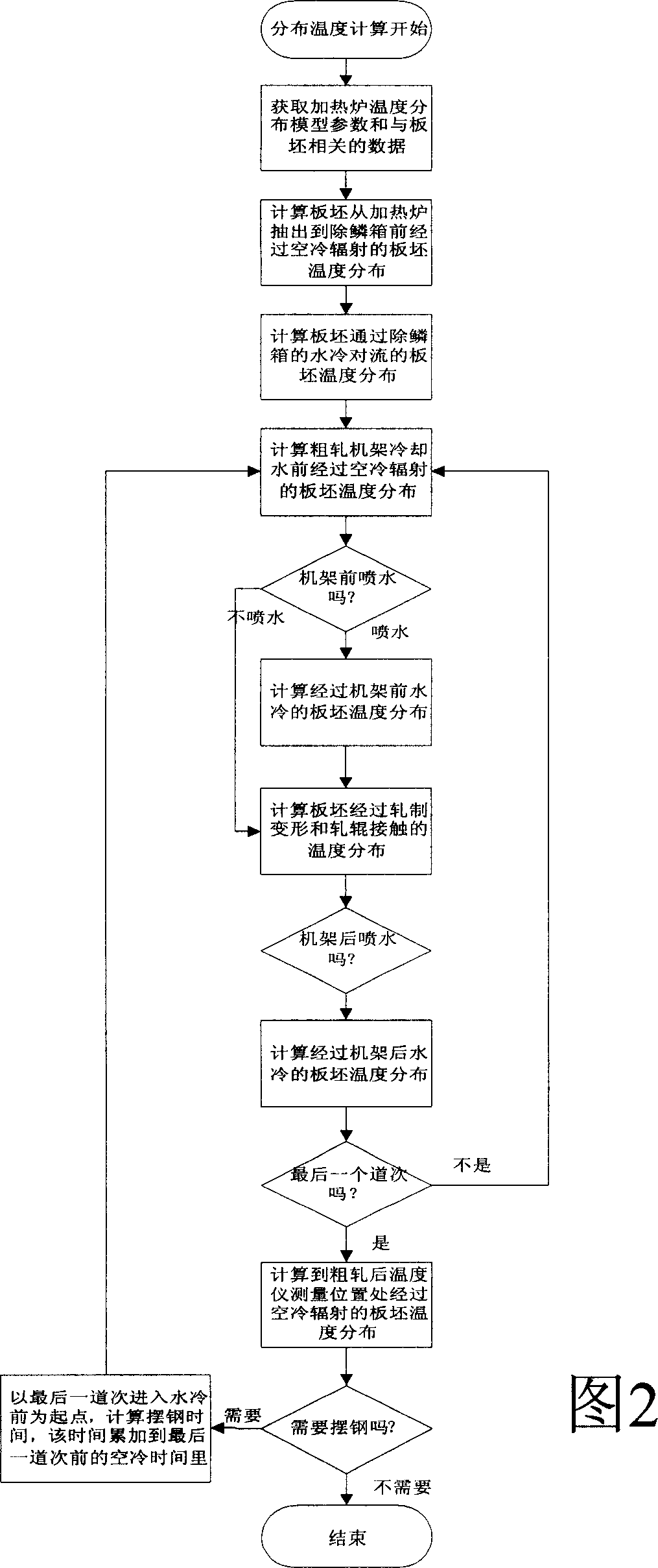

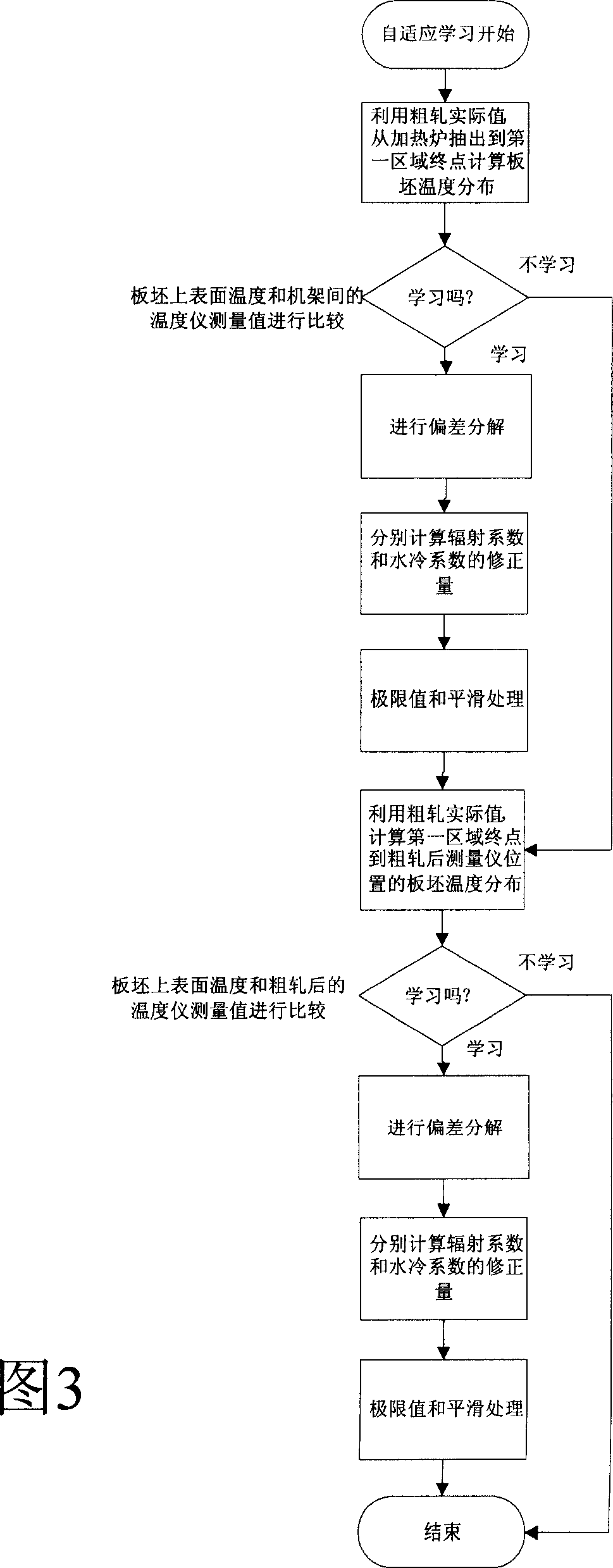

Roughed plate bloom temperature control method in hot-rolled process

ActiveCN1990131APrecise temperature controlCalculation speedTemperature control deviceSpecial data processing applicationsTemperature controlEngineering

The invention discloses a rough roll bar plate temperature control method in operation of heat rolling, the invention mainly uses the temperature when bar plate is pulled out of heating-furnace as start, according to the movement order and o running time of bar plate uses the recursive analytic temperature distribution model to calculating the temperature distribution of each points on the bar plate rolling operation path; and compares the average temperature of the measuring point on the bar plate after rough roll and the rough roll goal temperature, if the compared result is bigger then the permissible value of set temperature contrast of said both parties, then makes the last entrance temperature of rough roll as reference, and controls the temperature of bar plate through swing steel, in addition, makes self-adaptive amendment of the model radiation coefficient and water cooling coefficient in different areas, while according the rough roll goal temperature determines the swing time of bar plate on the middle roll table to controlling the temperature of bar plate accurately and improving the whole control level of rough roll procedure.

Owner:BAOSHAN IRON & STEEL CO LTD

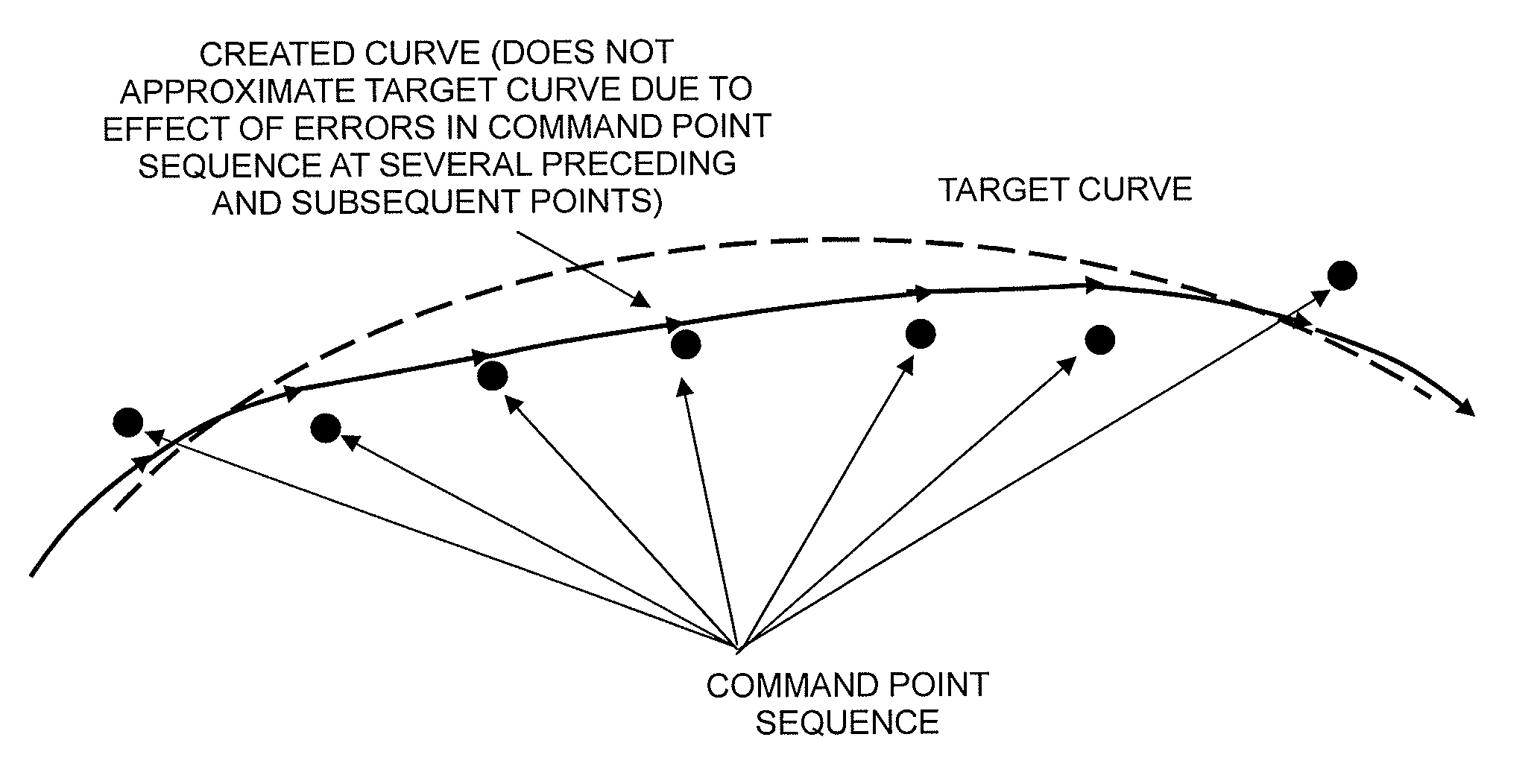

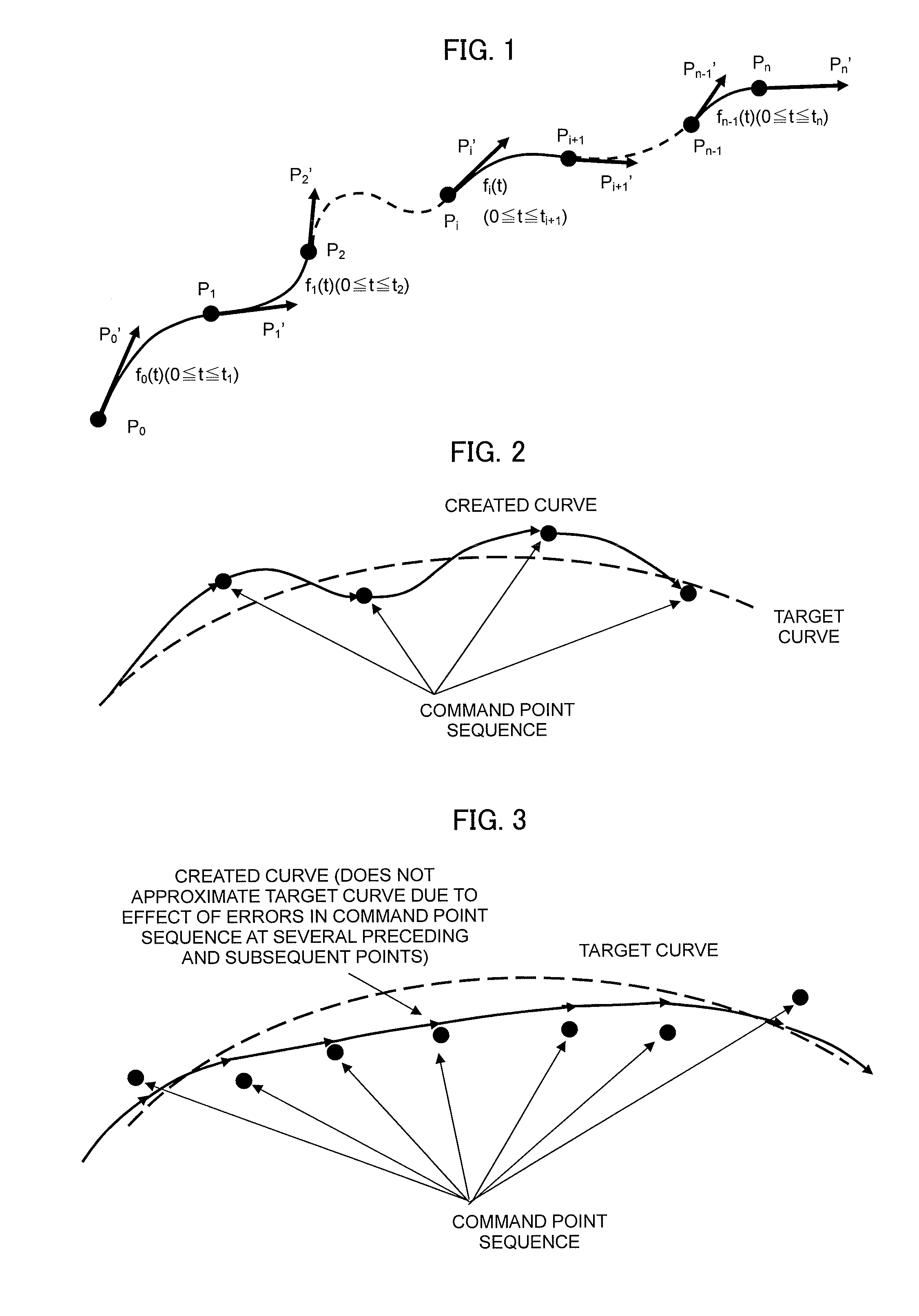

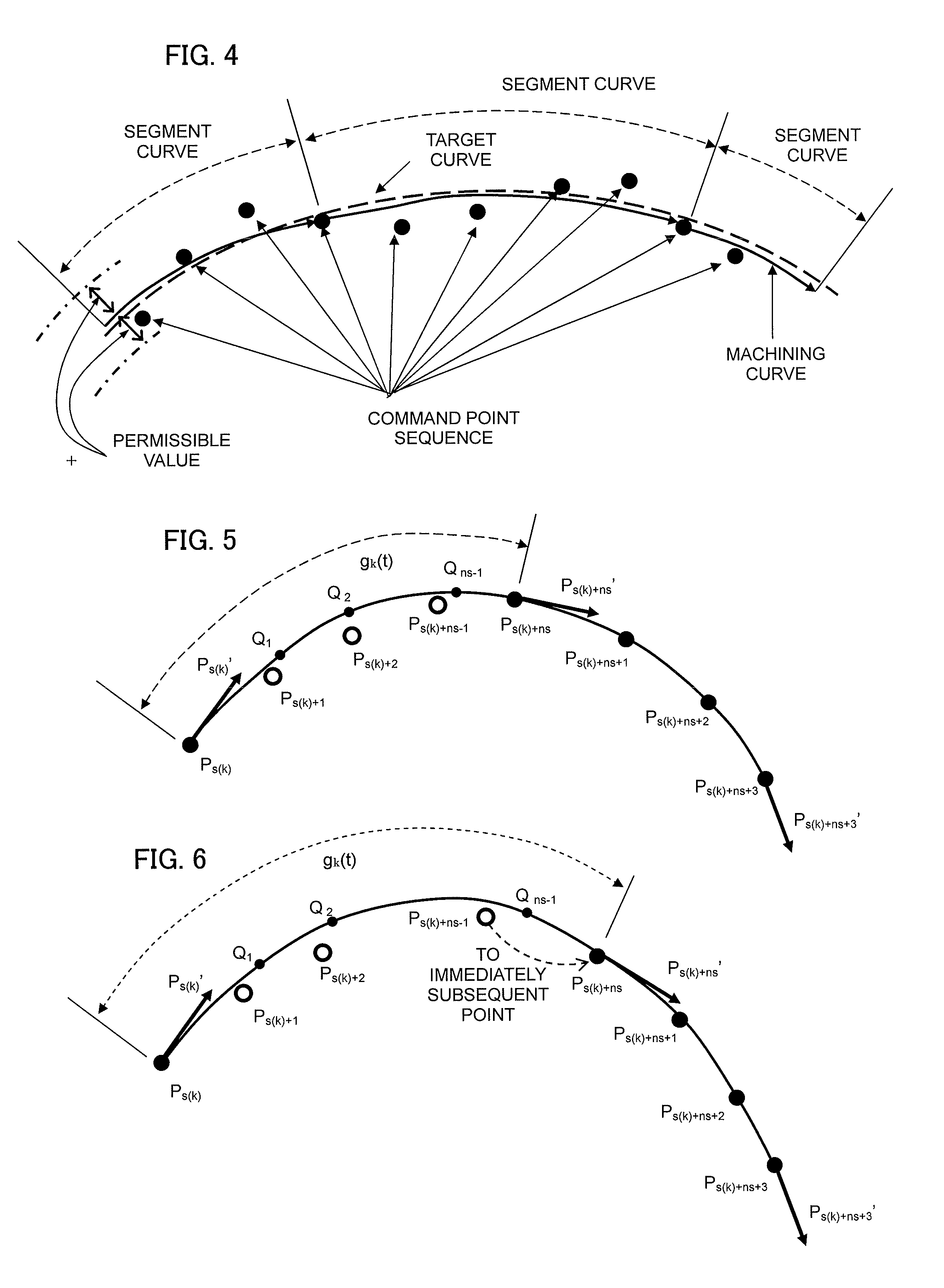

Numerical controller with machining curve creating function

ActiveUS20130218323A1Special data processing applicationsNumerical controlPoint sequenceComputer science

Owner:FANUC LTD

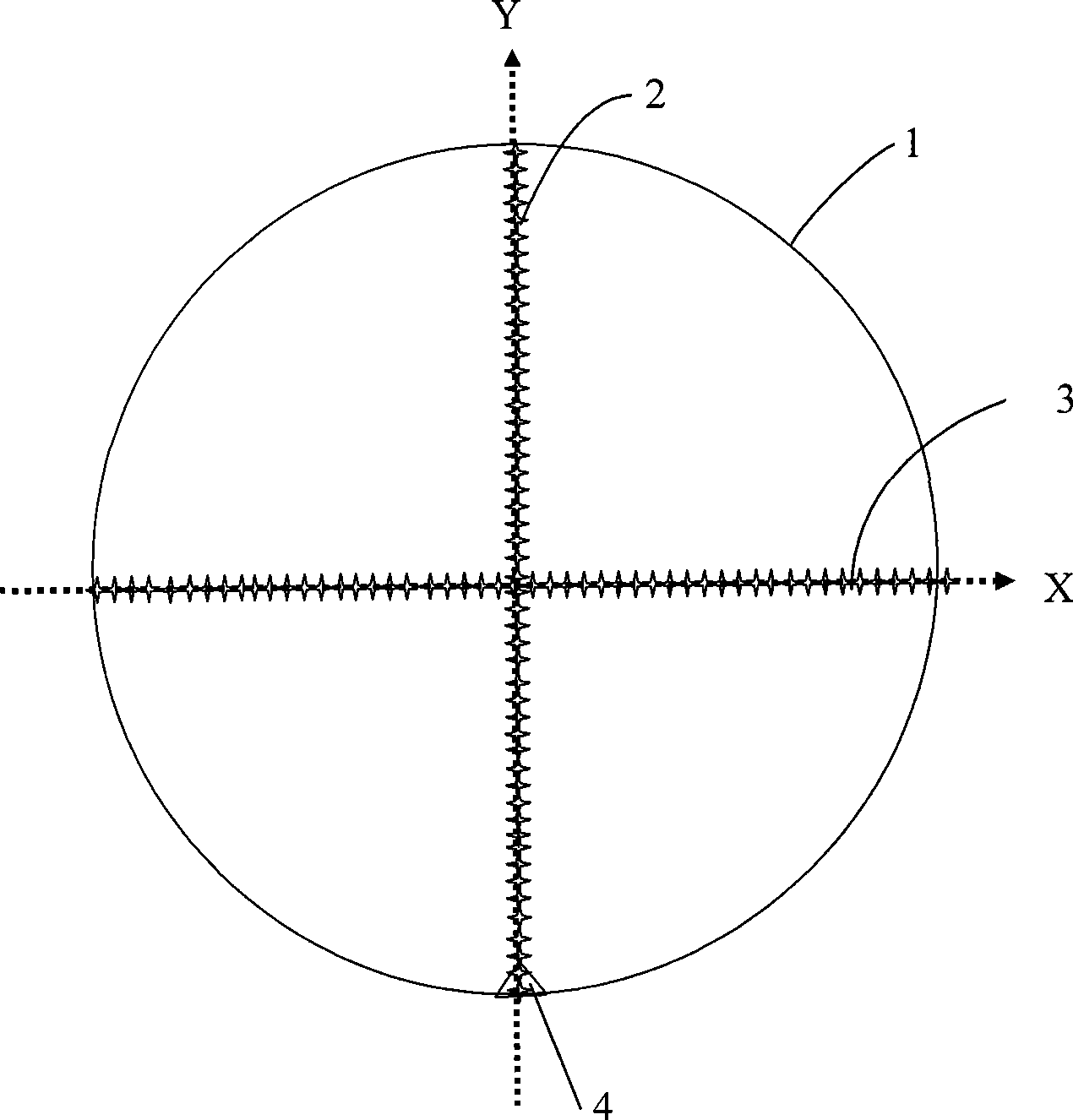

Detection method for silicon wafer warpage degree

InactiveCN101442018ATimely compensation and correctionEliminate the hidden danger of abnormal positionSemiconductor/solid-state device testing/measurementUsing optical meansSemiconductorSilicon

The invention discloses a method for detecting wafer warp degree, which relates to a detection process in the field of semiconductor. The detecting method comprises the following steps: two detecting lines which are vertical and intersected with a wafer center are selected from the surface of a wafer; and a plurality of detecting points are selected from each detecting line; before the wafer carries out certain processing procedure, the detecting device is used to measure a reference distance; after the wafer carries out certain processing procedure, the detecting device is used to measure the measuring distance; the measuring distance subtracts the corresponding reference distance to obtain a difference value of each measuring point; if the difference value is within the permissible value range, the difference values obtained respectively by two detecting points on the two detecting lines on the same circumference of the wafer are compared; if two difference values are same, the warp of the wafer is proved not to influence the subsequent processing procedure; and if the two difference values are different, the warp of the wafer is proved to influence the subsequent processing procedure. The detecting method provided by the method can effectively and timely detect whether the wafer warp is even or not, and avoid abnormal aligned mark position in the subsequent processing procedure.

Owner:SEMICON MFG INT (SHANGHAI) CORP

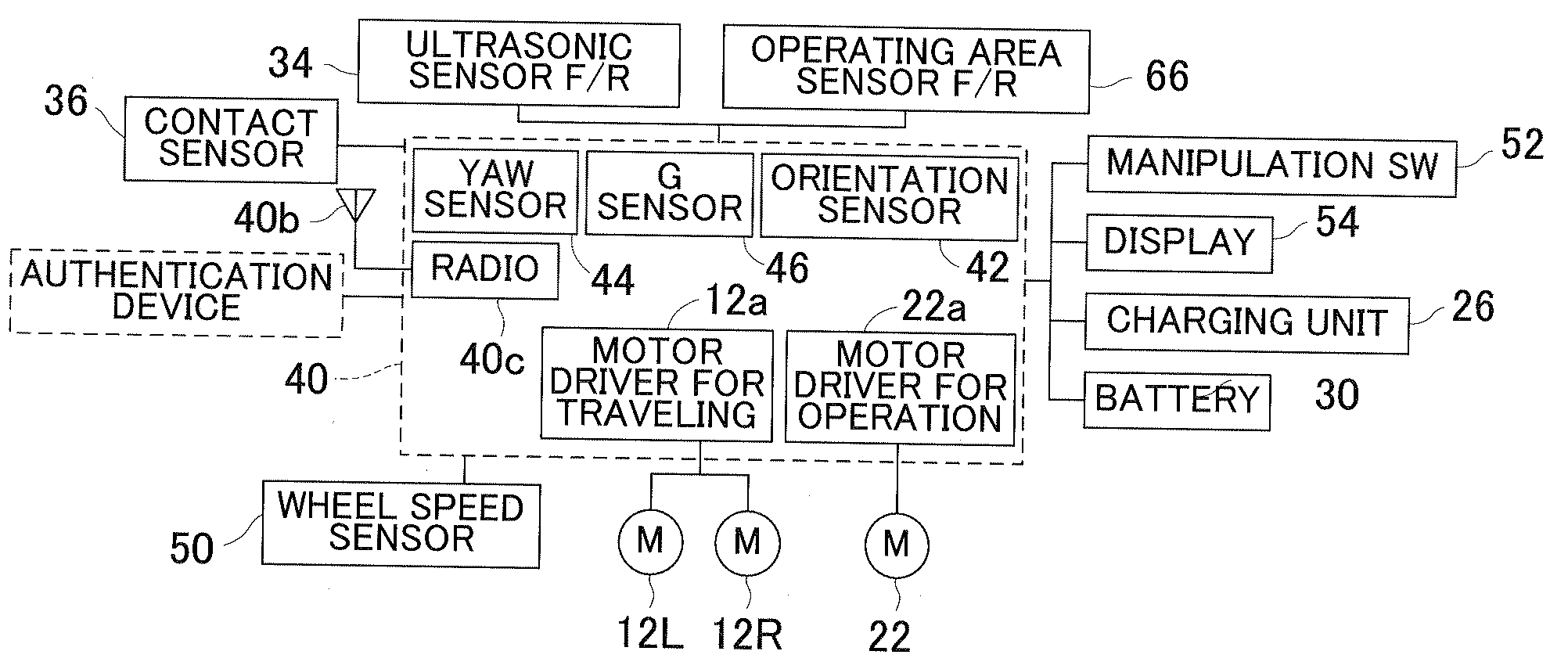

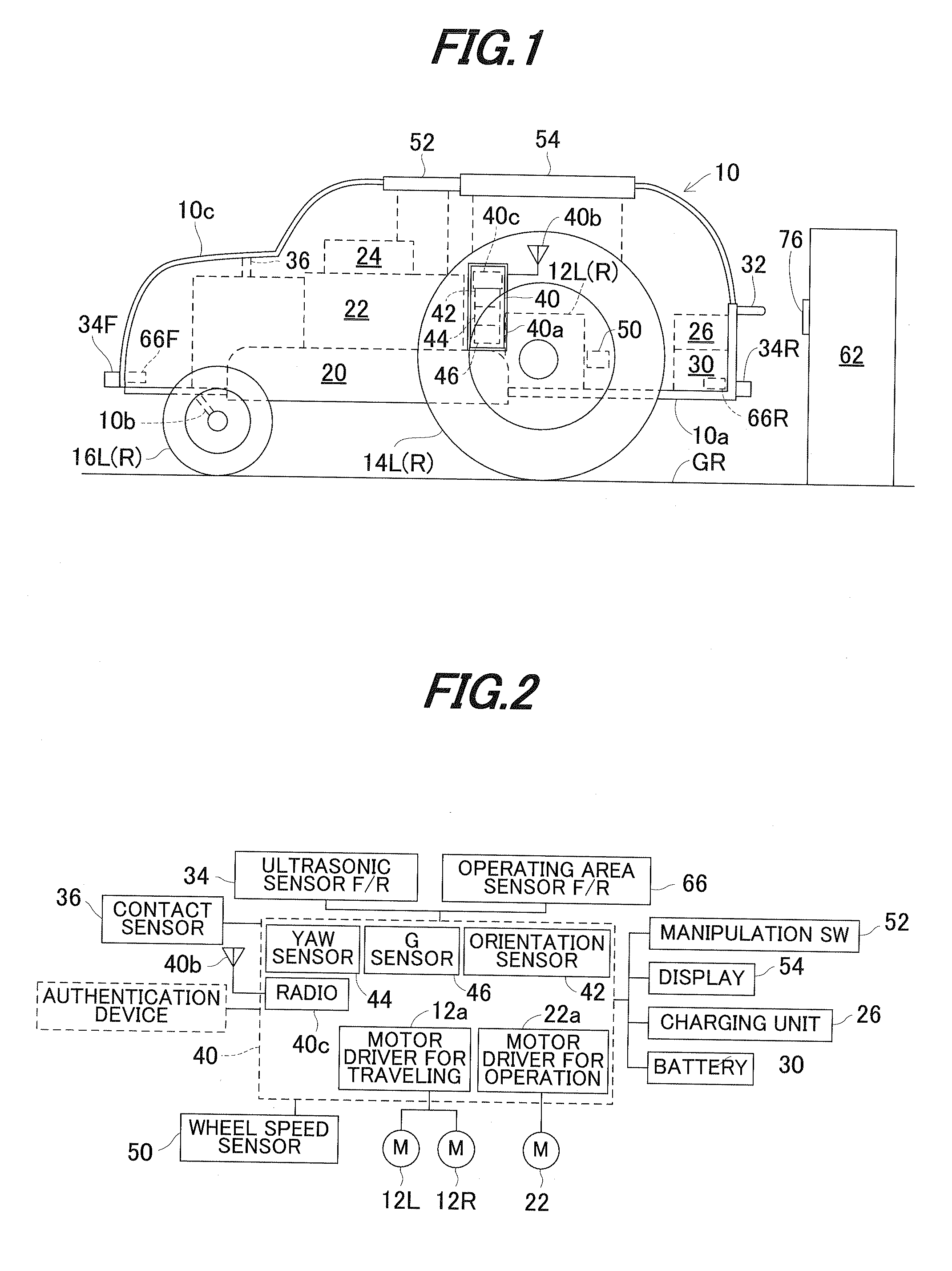

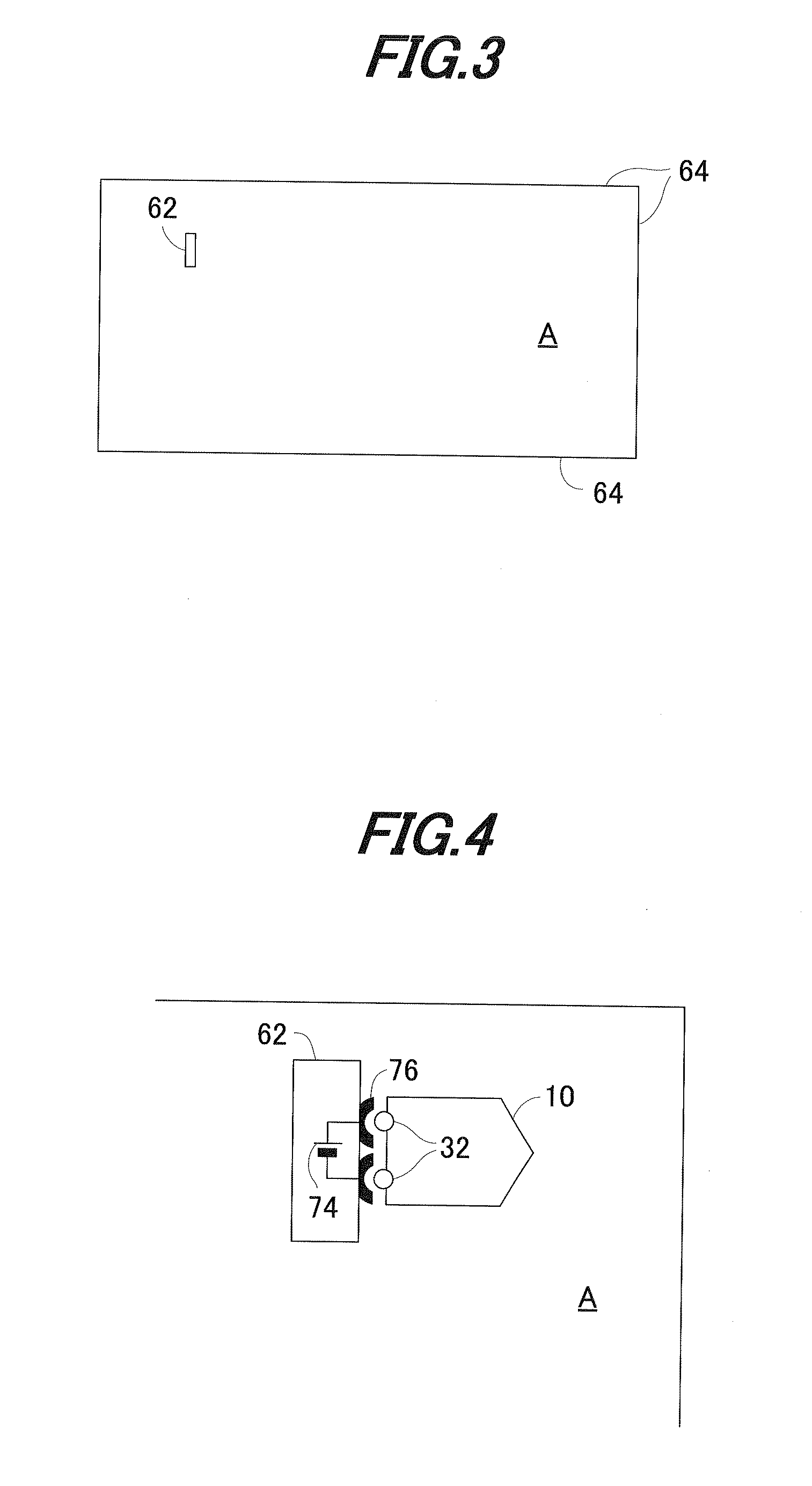

Control apparatus for autonomous operating vehicle

ActiveUS20120083963A1Instruments for road network navigationVehicle position/course/altitude controlWheel speed sensorAngular velocity

In an apparatus for controlling an autonomous operating vehicle, a traveling direction and traveled distance are calculated based on outputs of wheel speed sensor and angular velocity sensor, and the vehicle is controlled to, as traveling straight, perform the operation using an operating machine in accordance with a predetermined travel pattern in a travel-scheduled area based on the calculated traveling direction and traveled distance. It is determined whether a difference between a scheduled-travel distance scheduled in the predetermined travel pattern and an actual traveled distance exceeds a permissible value when the vehicle is traveled straight and a center value of the outputs of the angular velocity sensor is corrected when the difference is determined to exceed the permissible value.

Owner:HONDA MOTOR CO LTD

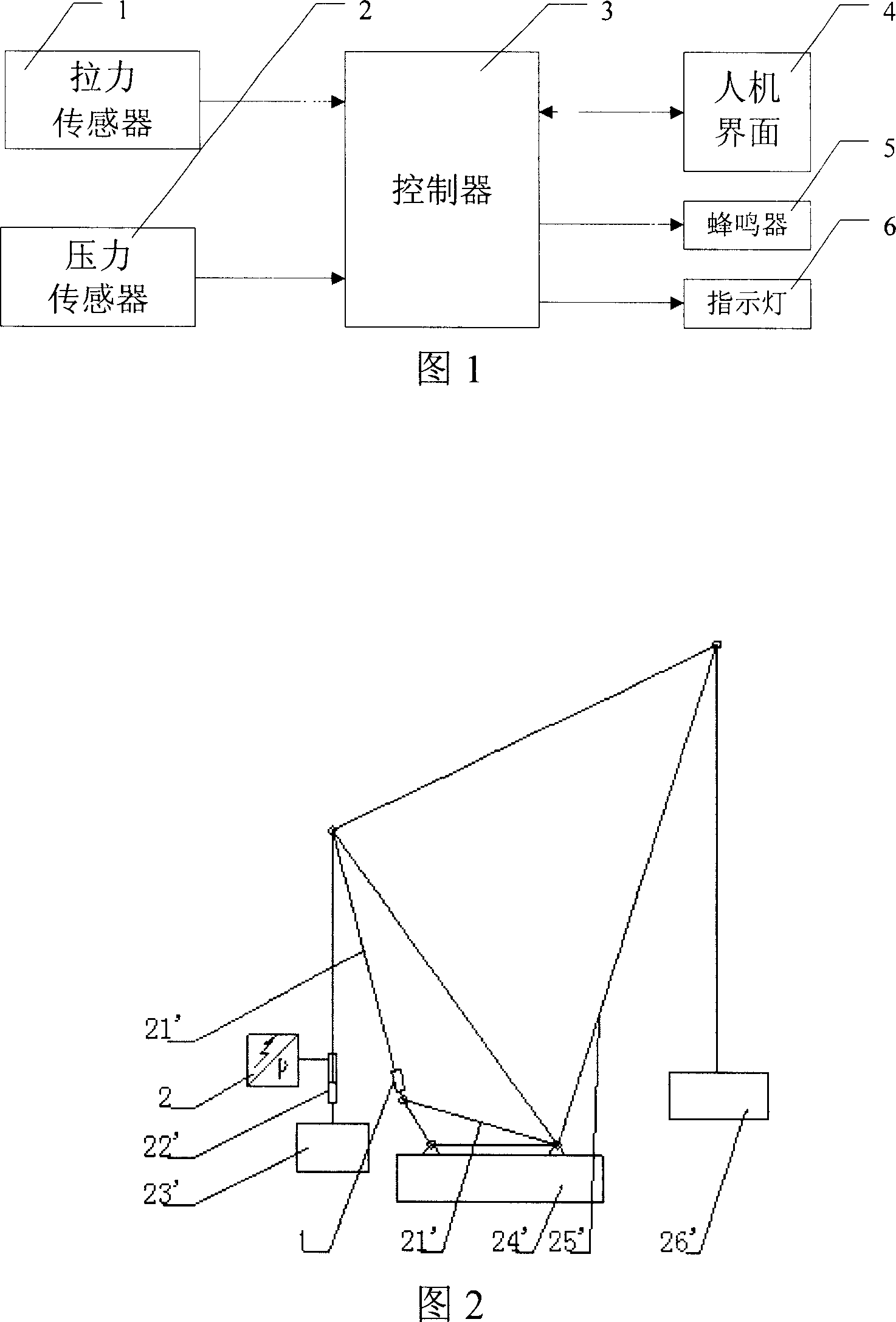

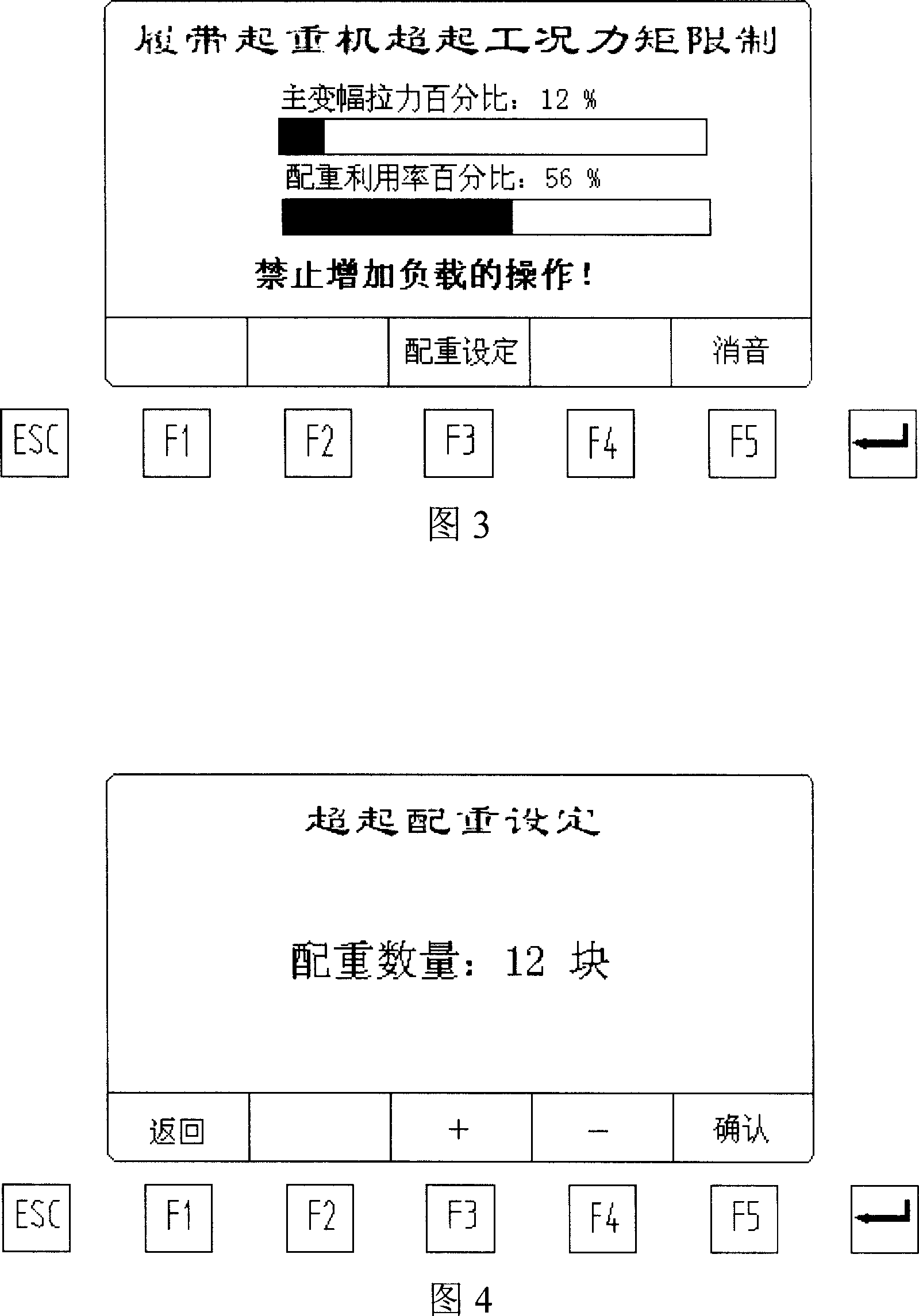

Crawler crane torque controlling method and apparatus under super lifting working condition

InactiveCN101021731ANovel methodEasy to implementMechanical power/torque controlHuman–machine interfacePull force

A torque control method and device on the condition of superlift of a crawler crane takes the ratio of actual loading pressure and maximum permissible value of the crane main luffing rod as the main luffing percentage A, and the ratio of pull sum for crane superlift counterweight upgrading fuel tank and counterweight as the using percentage B to realize the torque control according to the relation of A and B. It also provides a method of achieving the above device, which includes: buzzers, lights, pull sensors set on the main luffing rod, pressure sensors on the superlift counterweight fuel tank, the controller coupled with the above components and the interface coupled with controller.

Owner:SHANGHAI SANY TECH

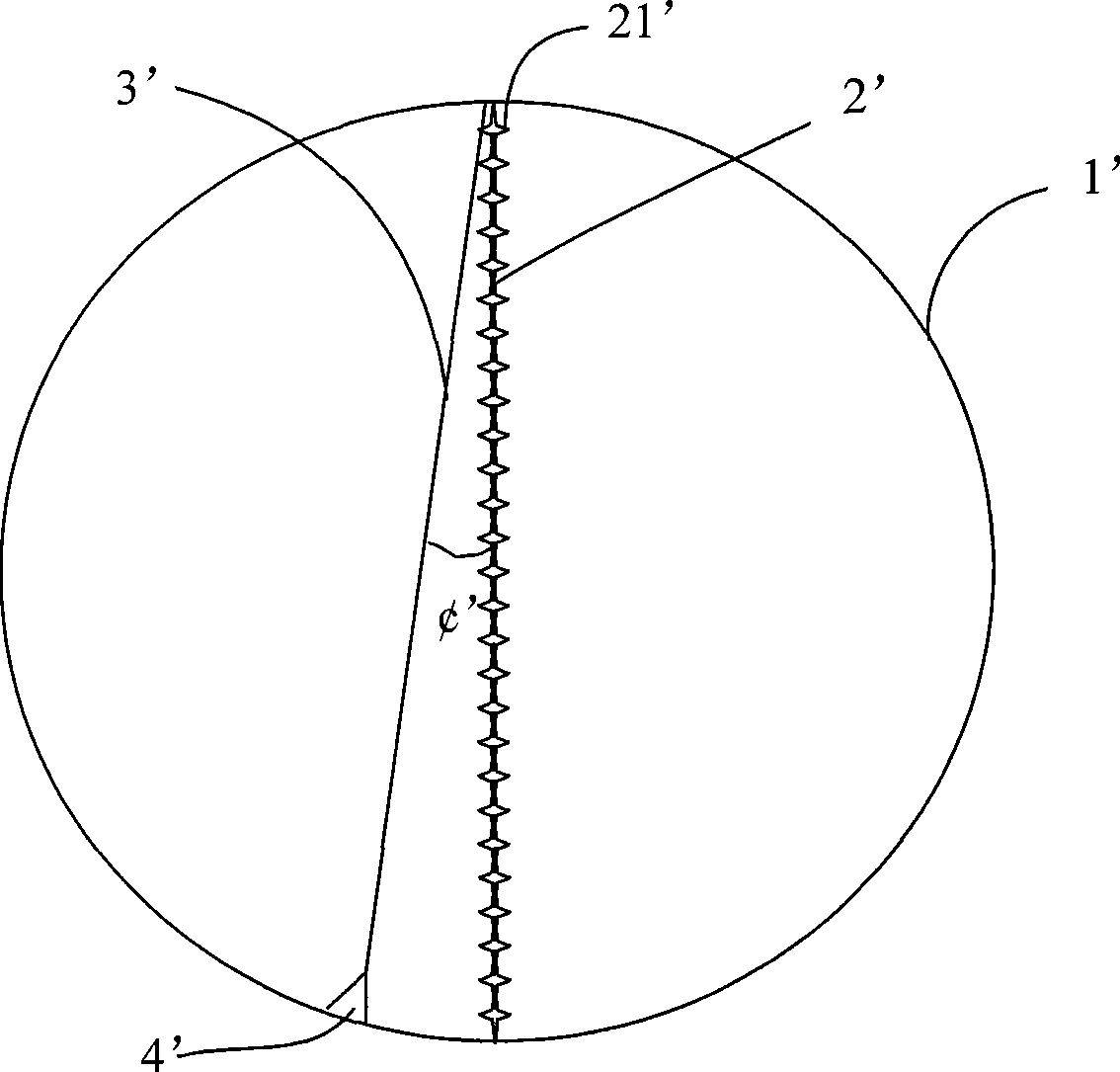

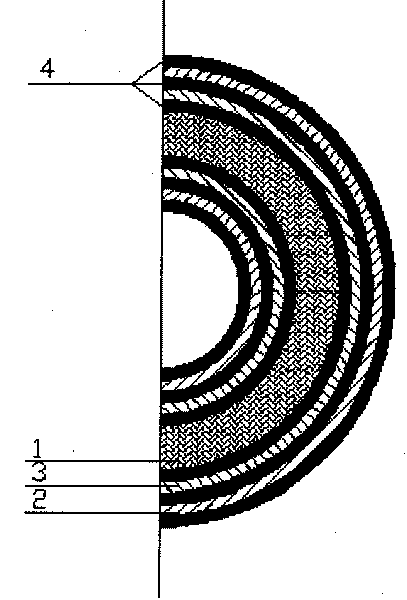

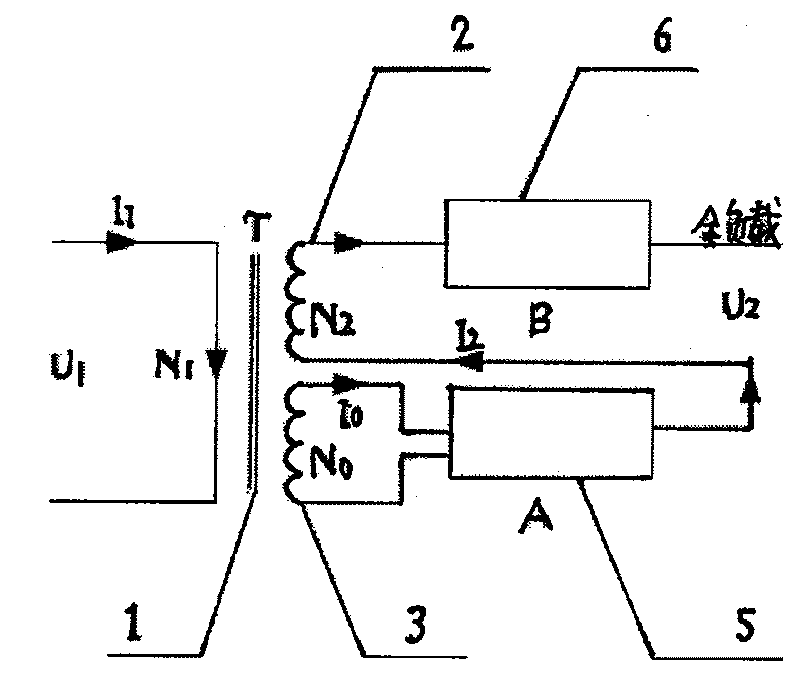

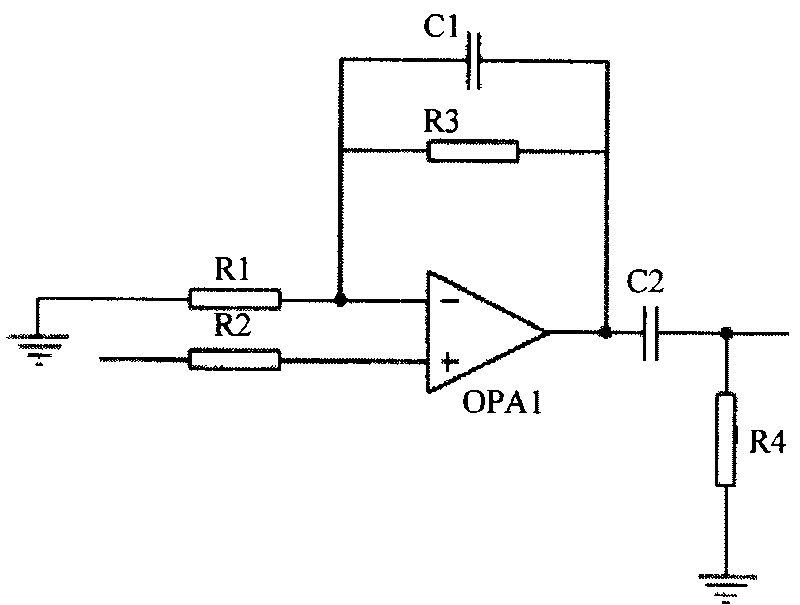

Power frequency zero-flux mini-current sensor for capacitive equipment dielectric loss on-line monitoring

InactiveCN101692102ASimple internal structureEasy to manufactureResistance/reactance/impedenceCurrent/voltage measurementDielectric lossPotential difference

A power frequency zero-flux mini-current sensor for capacitive equipment dielectric loss on-line monitoring comprises a working magnetic core 1, wherein a test coil 3 is winded round the working magnetic core 1, a secondary side coil 2 is winded round the test coil 3 in the inverse direction, shielding layers 4 are arranged between the secondary side coil 2 and the test coil 3, and the test coil 3 and the working magnetic core 1, the test coil 3 is connected with a compensation circuit module 5, the output end of the compensation circuit module 5 is connected with one end of the secondary side coil 2, the other end of the secondary side coil 2 is connected with an output circuit module 6, the two ends of the test coil 3 generate induced potential, the induced current is added to the output end of the compensation circuit module 5 to generate secondary current for the secondary side coil 2, the compensation circuit module 5 is used to test the potential difference of the test coil 3, the magnetic flux in the working magnetic core is almost equal to zero; and if the test value deviates the permissible value, the working magnetic core can be adjusted automatically to keep in almost zero-flux state, and the mini-current sensor has high reliability and is characterized by simple structure, little production difficulty and low cost.

Owner:西安博源电气有限公司

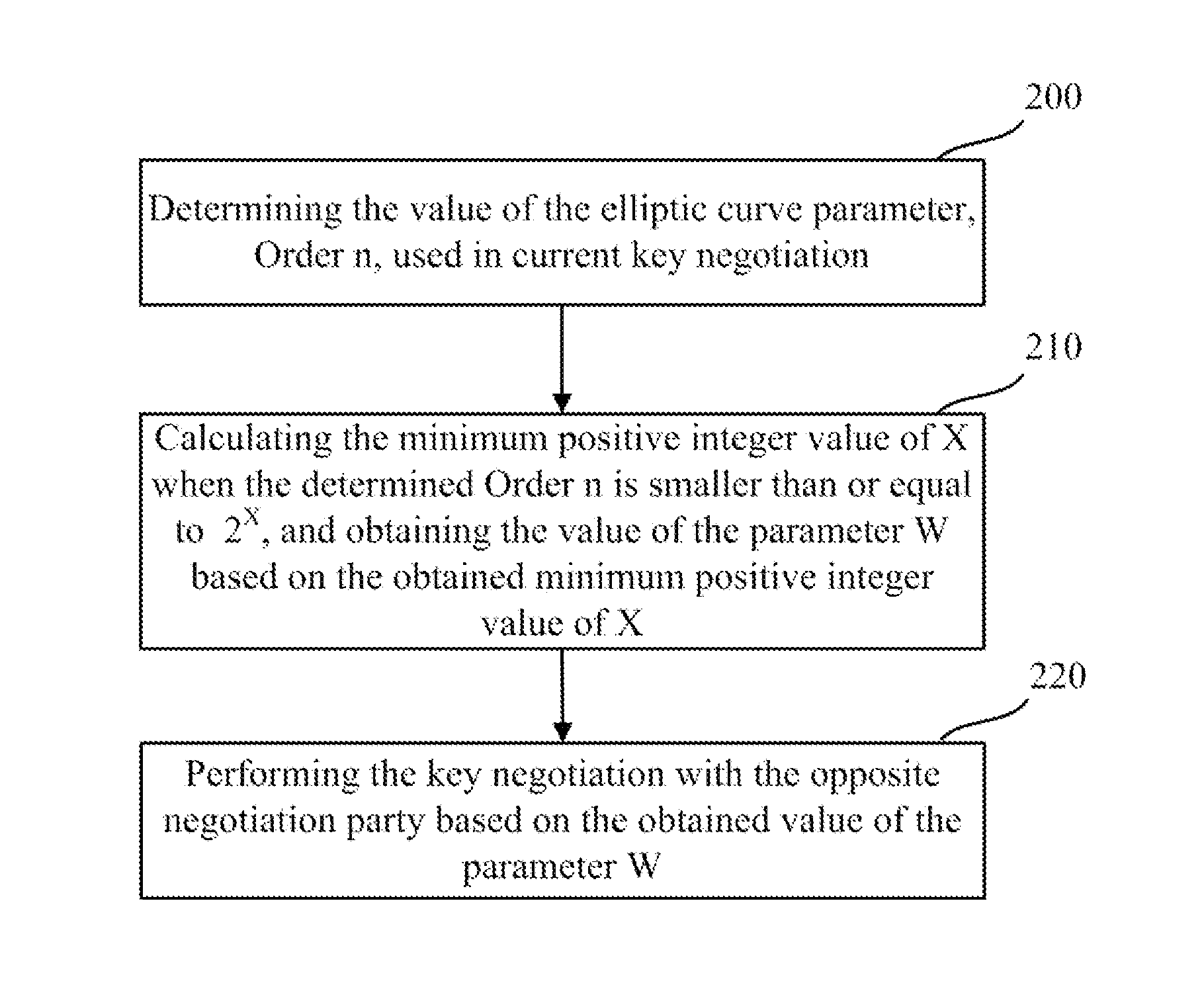

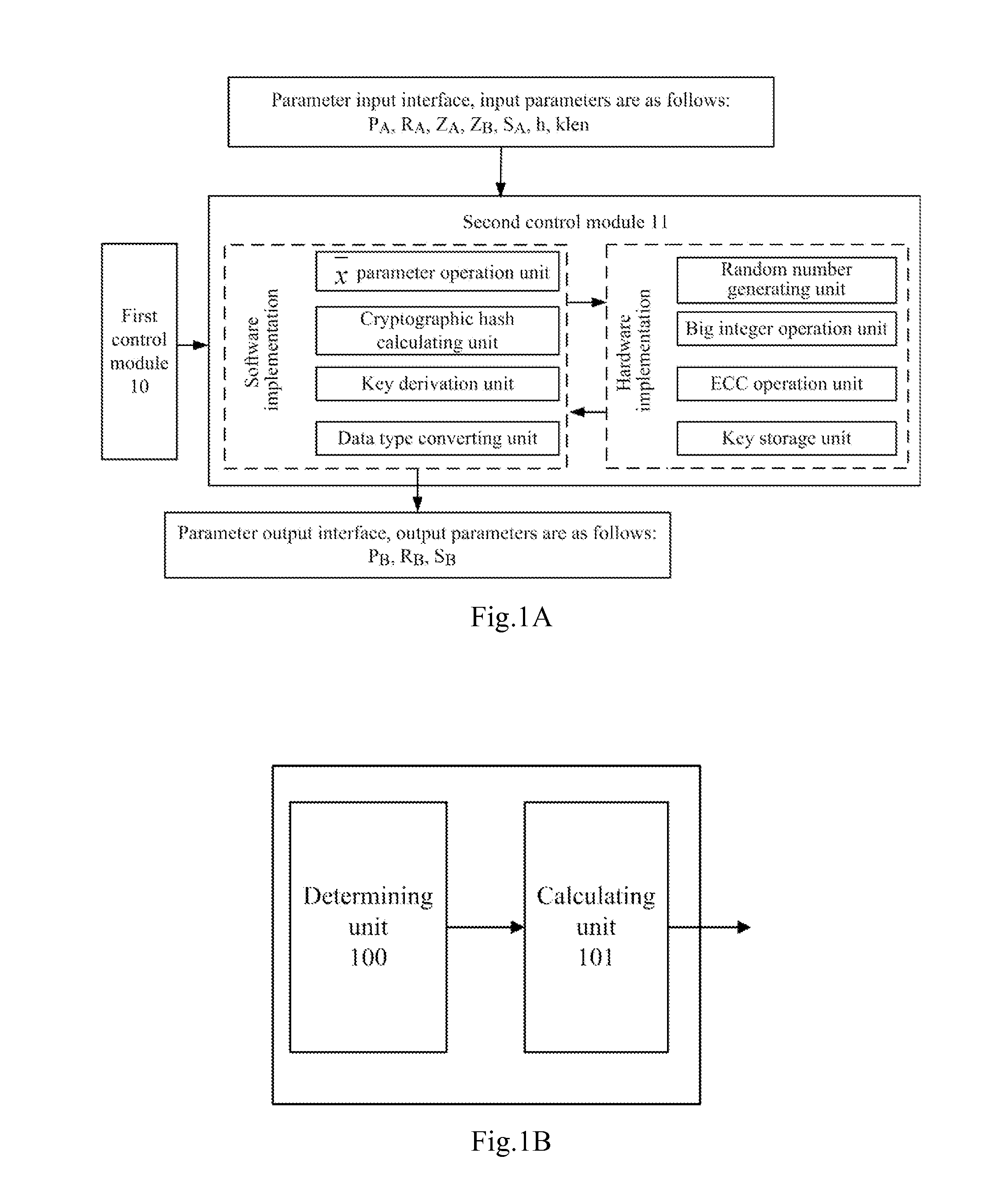

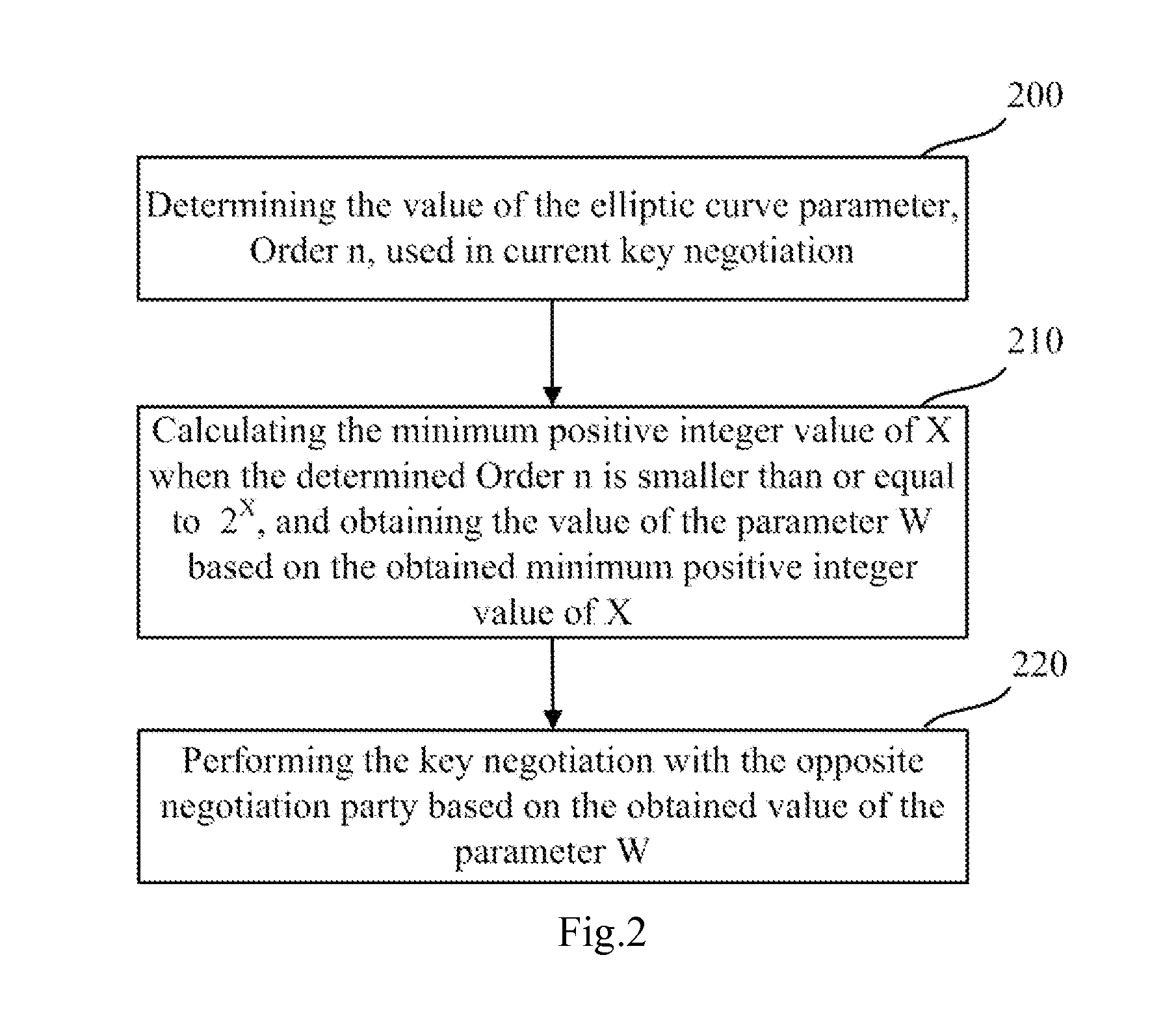

Key negotiation method and apparatus according to sm2 key exchange protocol

ActiveUS20150124970A1Implementation complexity can be reducedImprove execution efficiencyKey distribution for secure communicationMultiple keys/algorithms usageKey exchangeComputer hardware

The invention relates to the technical field of information, and disclosed in the present invention are a key negotiation method and apparatus according to the SM2 key exchange protocol. The method is implemented as follows: two negotiation parties both calculate a parameter W according to the minimum positive integer value in the permissible values of X which enable an inequality n≦2X to hold, and perform key negotiation with the opposite negotiation party according to the parameter W. Compared with a method for calculating the parameter W through calculating log2 (n) logarithmic value firstly and then rounding up the logarithmic value, the method disclosed by the invention has the advantages that the calculated amount is effectively reduced, and the implementation complexity of an algorithm is reduced, thereby greatly improving the implementation efficiency of the key negotiation process based on the SM2 key exchange protocol, and then optimizing the engineering implementation of the SM2 key exchange protocol.

Owner:CHINA IWNCOMM

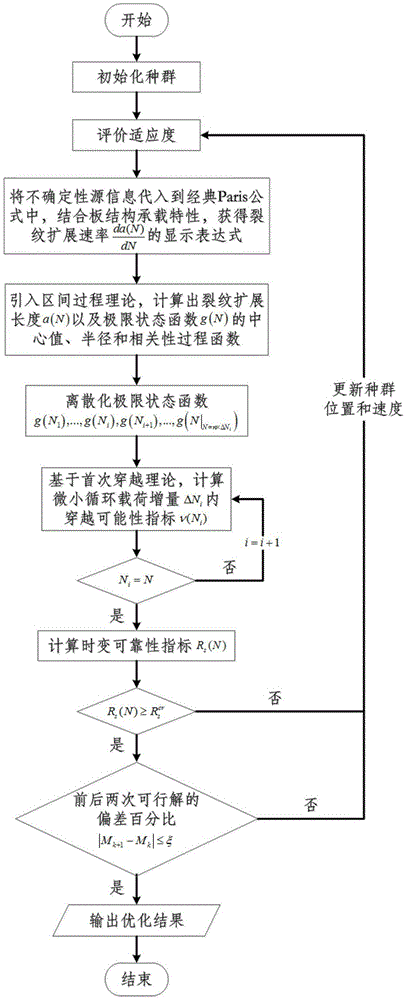

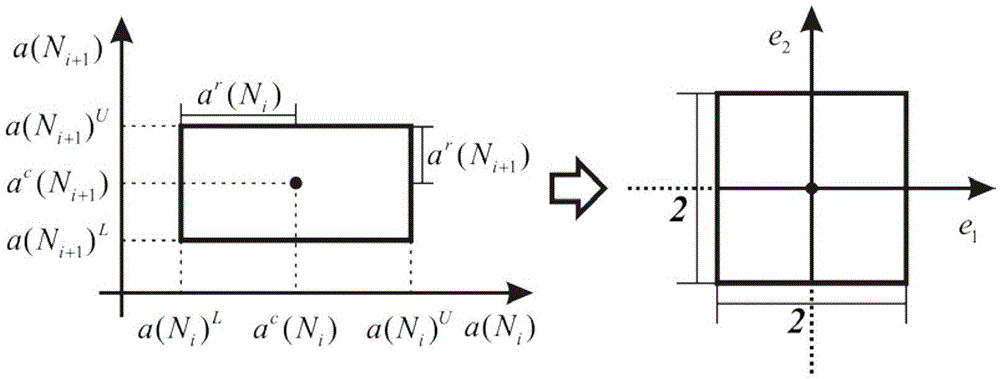

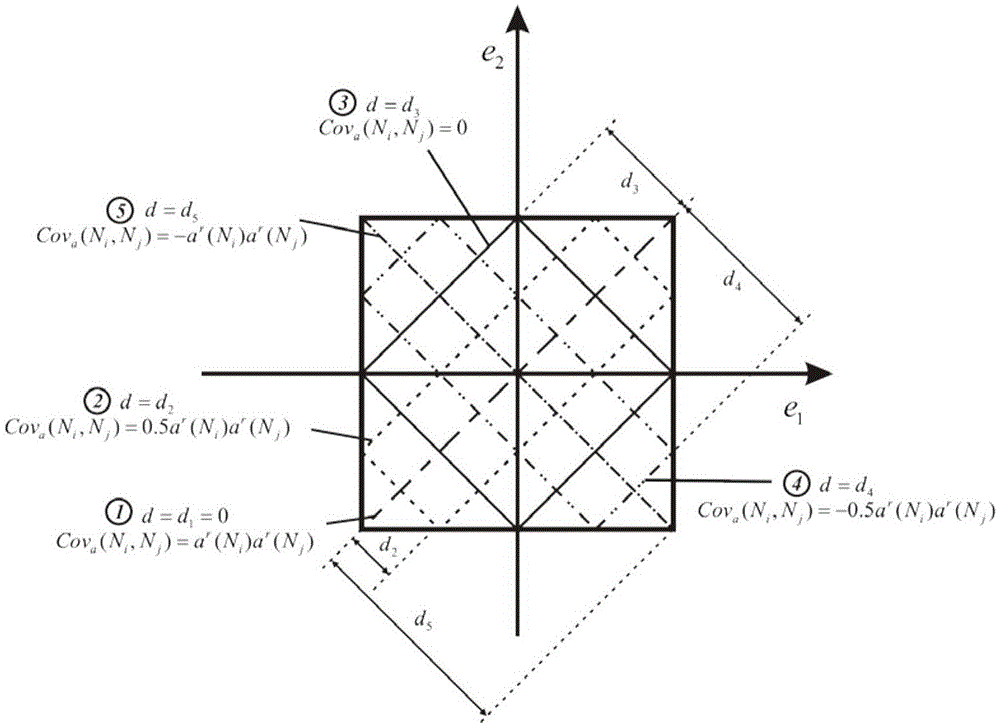

Time-variant reliability design method for rectangular plate structure with initial defects

ActiveCN105653794AMake up for and perfect limitationsReduce dependenceSpecial data processing applicationsReliability designOptimal design

The invention discloses a time-variant reliability design method for a rectangular plate structure with initial defects. The method comprises the steps of firstly, according to stress characteristics of the defected plate structure, considering indeterministic effects of parameters such as a load, material characteristics, a design permissible value and the like under a finite sample condition, and establishing a non probability interval process model of crack expansion length of the rectangular plate structure; secondly, based on a classic Paris damage evolution formula and a first passage theory, constructing a time-variant reliability measurement model of the structure with the initial defects; and finally, by taking the reliability as a constraint condition, the weight reduction as an optimization target and the plate thickness as a design variable, performing repeated iterations to obtain an optimal design scheme of the structure within a set service time. According to the method, the comprehensive influence of indeterminacy on power safety of the structure with the initial defects within a set life cycle is reasonably characterized in an optimization design process, and the weight can be effectively reduced, thereby ensuring the safety and economy of the design.

Owner:BEIHANG UNIV

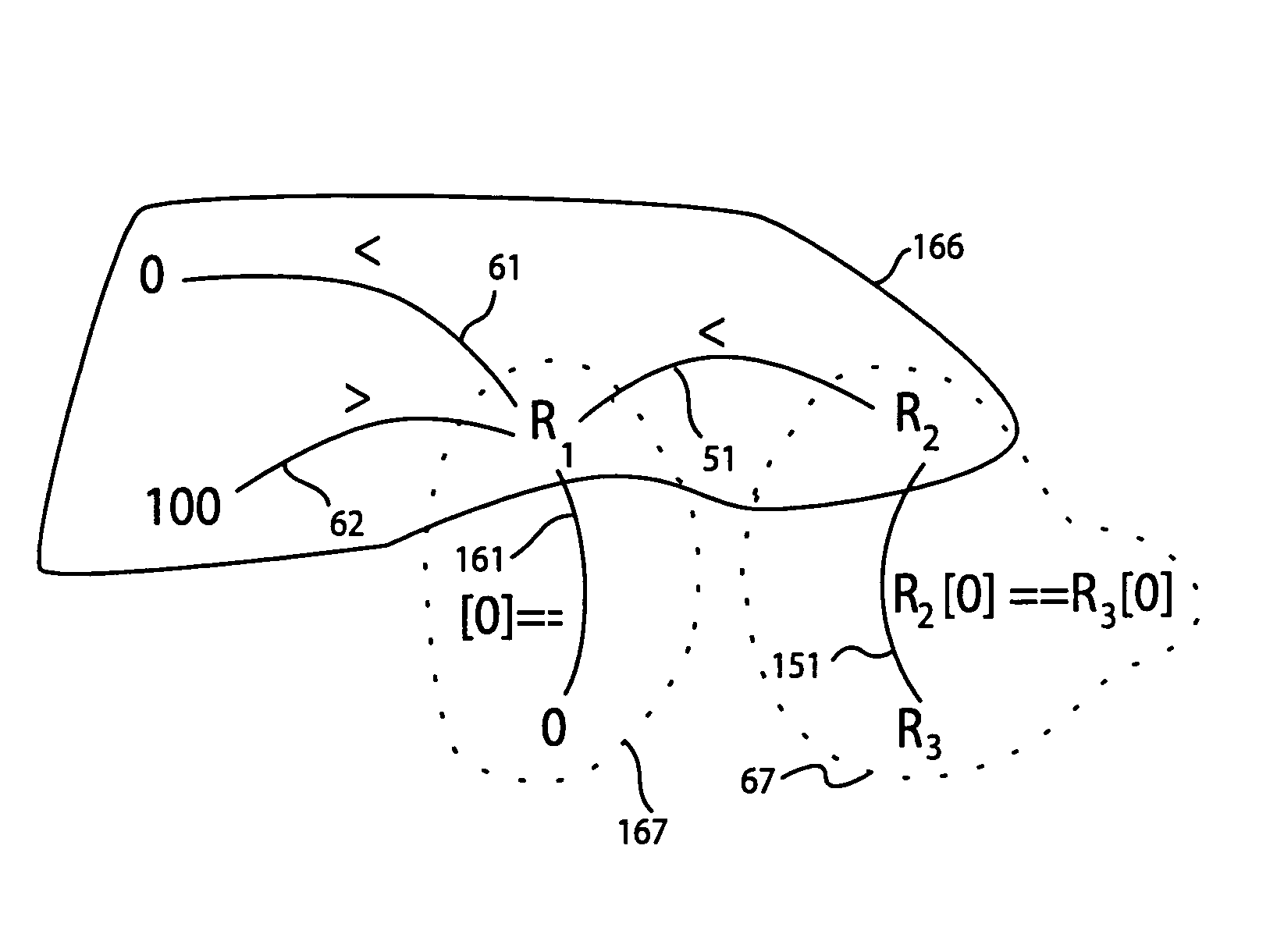

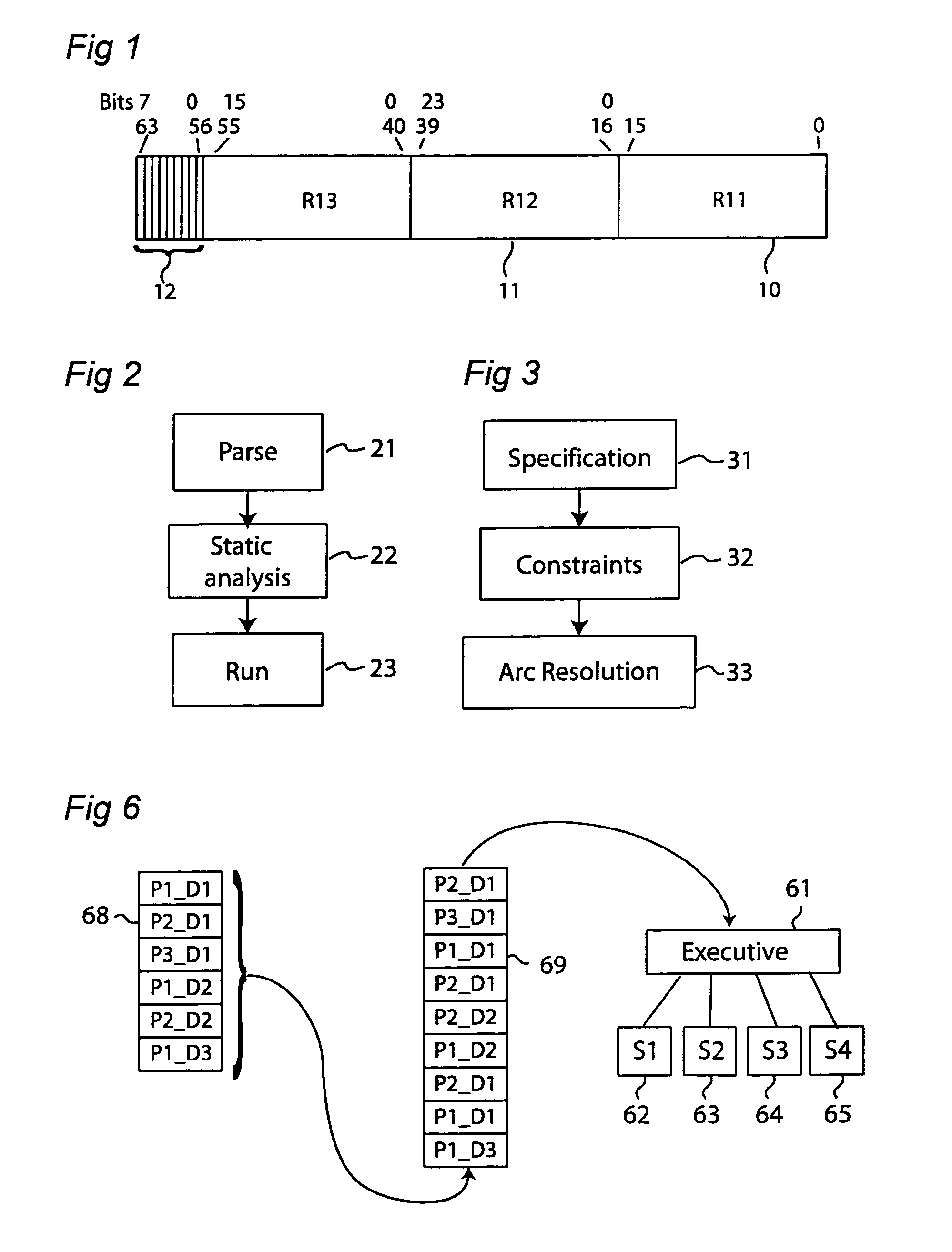

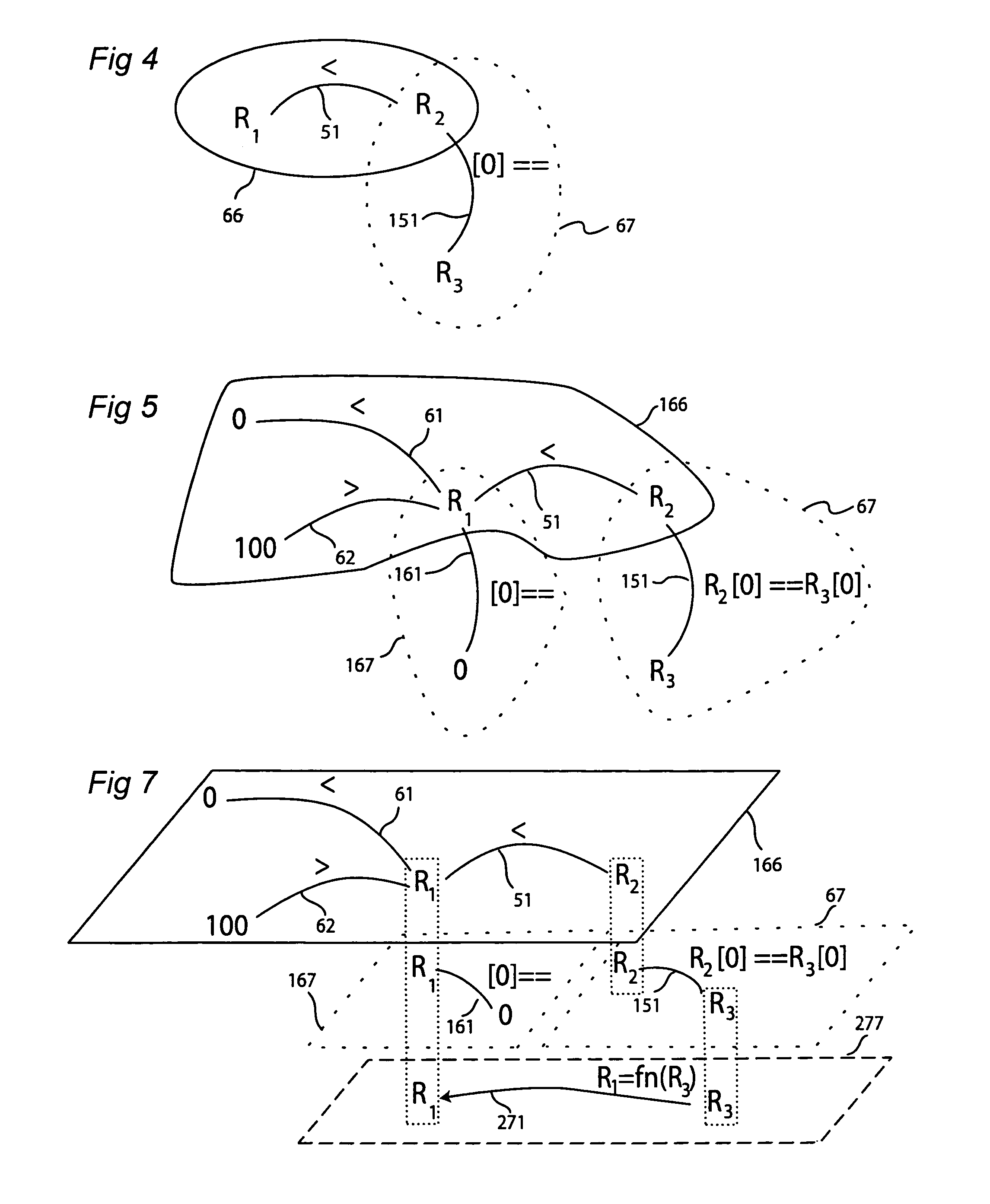

System and method for test generation with dynamic constraints using static analysis and multidomain constraint reduction

ActiveUS7870523B1Quantity minimizationError detection/correctionDigital computer detailsStatic timing analysisA domain

The present invention provides a system and method for resolving a test generation problem involving constraint resolution problems where a verification environment includes constraints that are suitable for resolution using one type of solver for a first domain and other constraints that are suitable for resolution using a different solver in a second domain. The invention further comprises variables and, in instances where at least one variable is in each of the first and second domains, using these solvers to restrict the set of permissible values of variables to be consistent in multiple domains, preferably in all relevant domains.A constraint resolution problem is divided into clusters of constraints connected within a domain, and connected clusters of clusters that are connected through shared variables that are subject to constraints in more than one cluster.A preferred solver is applied to constraints in each of various domains such that constraints in multiple clusters and domains in a connected cluster are consistent for connected constraints in a domain, and preferably all constraints in all clusters in all domains within the connected cluster are consistent.

Owner:CADENCE DESIGN SYST INC

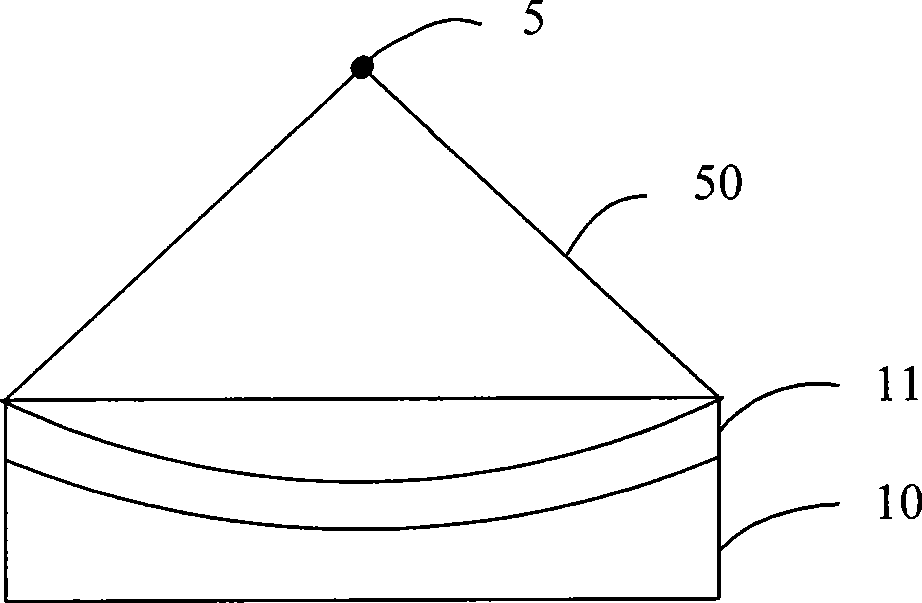

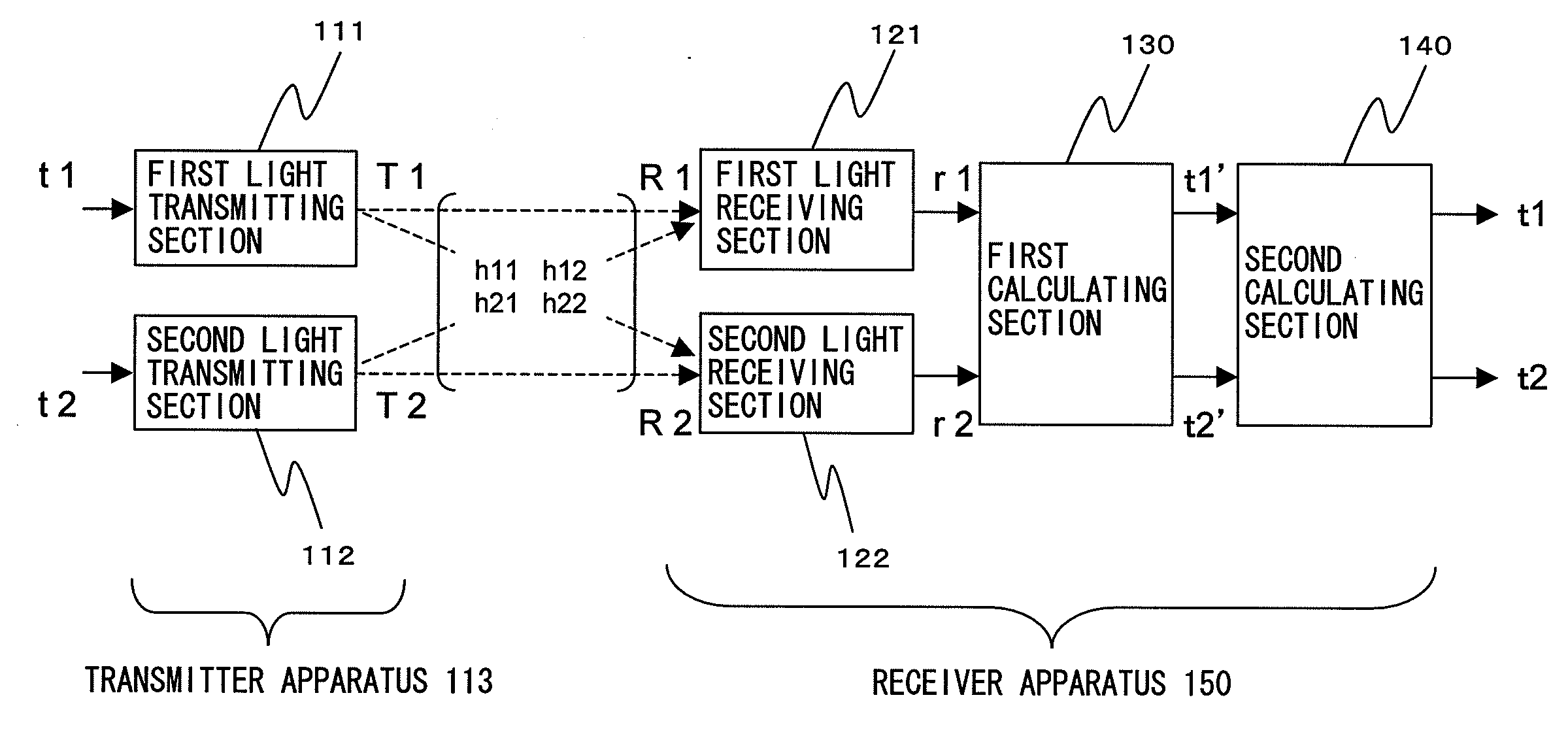

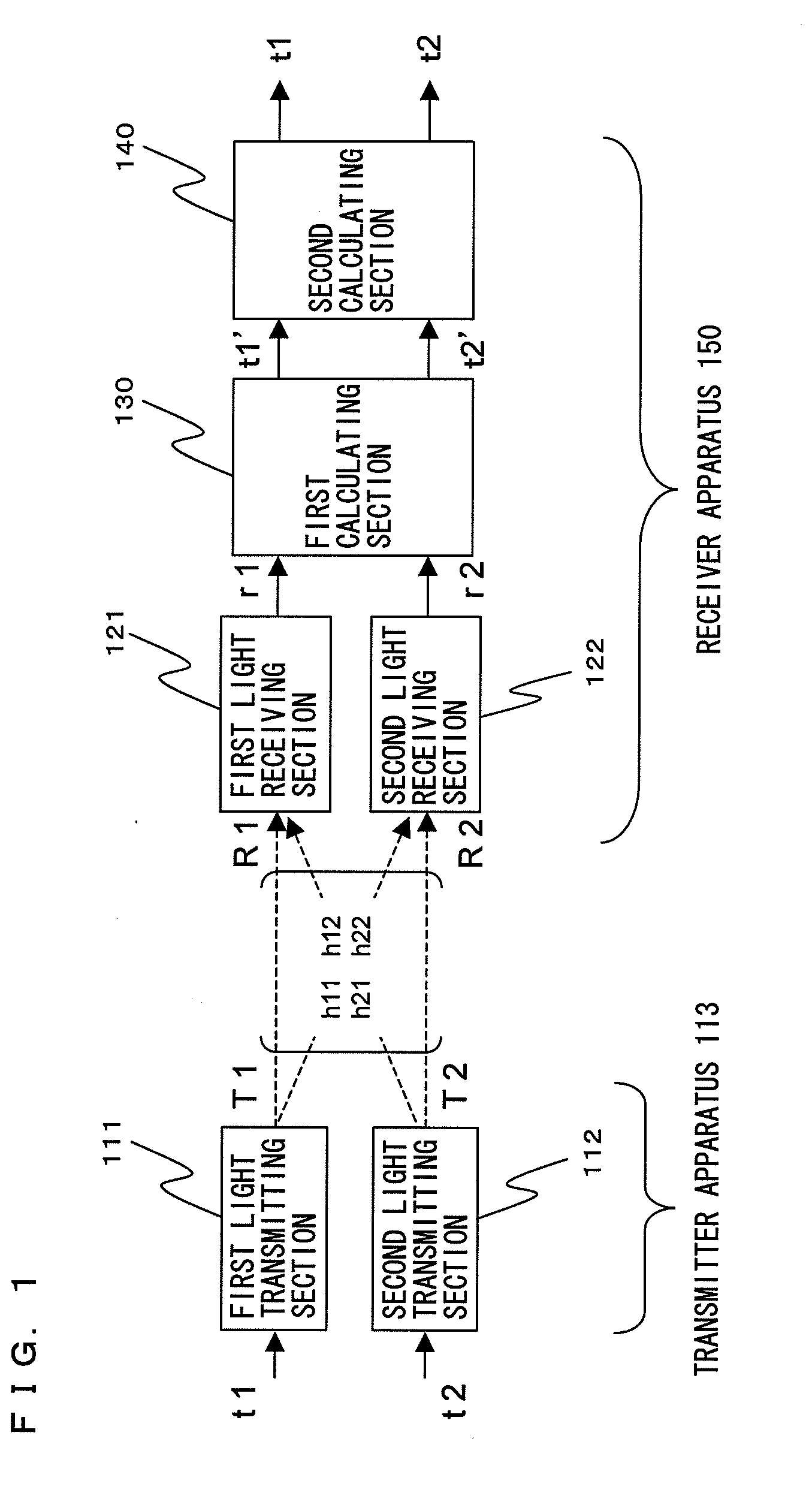

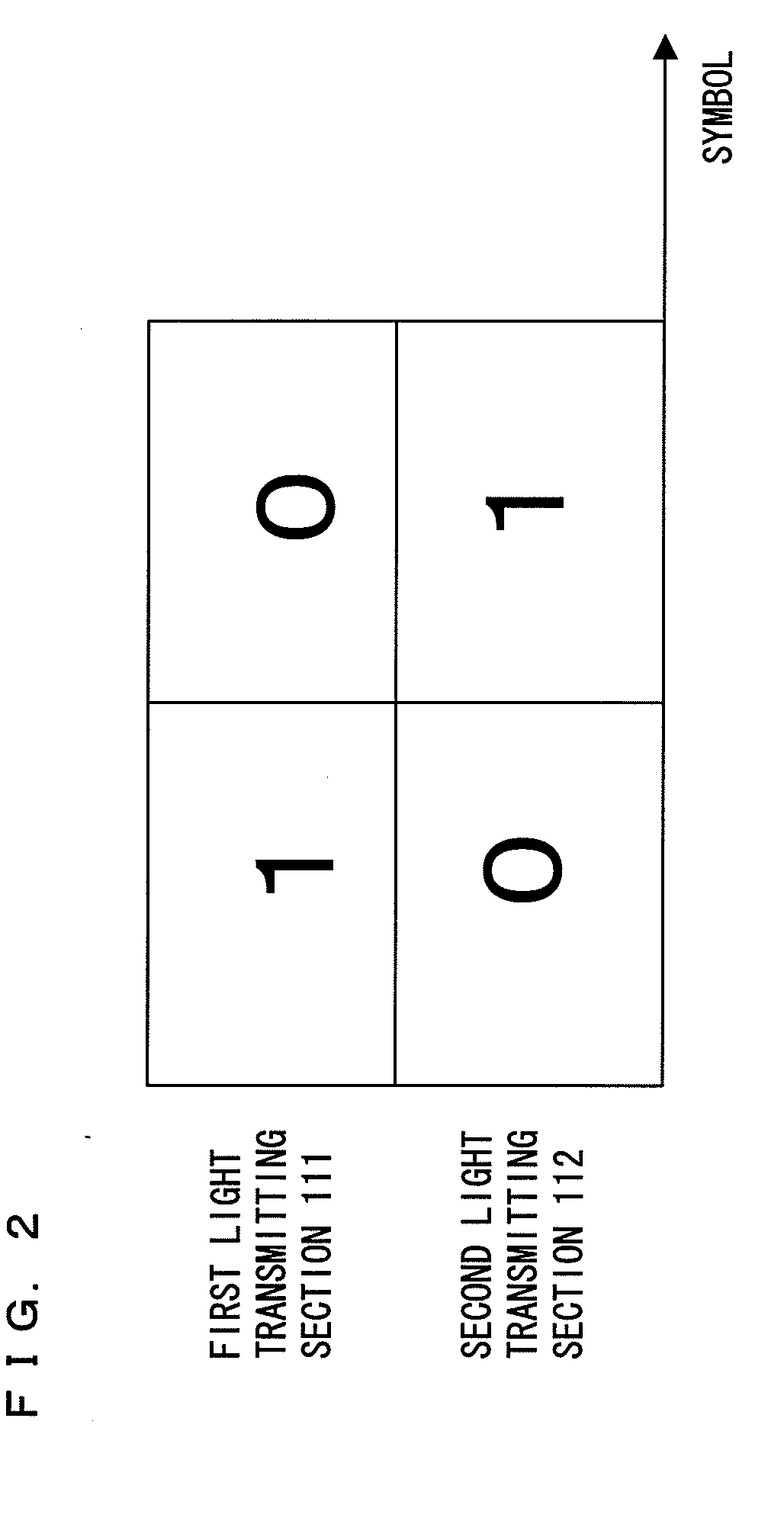

Receiver apparatus for use in optical space transmission system

InactiveUS20090097856A1Reduce decreaseReduce the impactClose-range type systemsElectromagnetic receiversOptical spaceDistortion

There included are a plurality of light receiving sections (121, 122) for receiving a plurality of optical signals (R1, R2) and respectively converting the received optical signals to a plurality of electrical signals (r1, r2); a first calculating section (130) for subjecting the plurality of electrical signals (r1, r2) to a process of canceling interference components occurring due to propagation of the plurality of optical signals through space; and a second calculating section (140) for calculating, with respect to each of the plurality of electrical signals whose interference components have been canceled by the first calculating section, whether or not a distortion occurring due to optical beat interference has a value less than or equal to a predetermined permissible value.

Owner:PANASONIC CORP

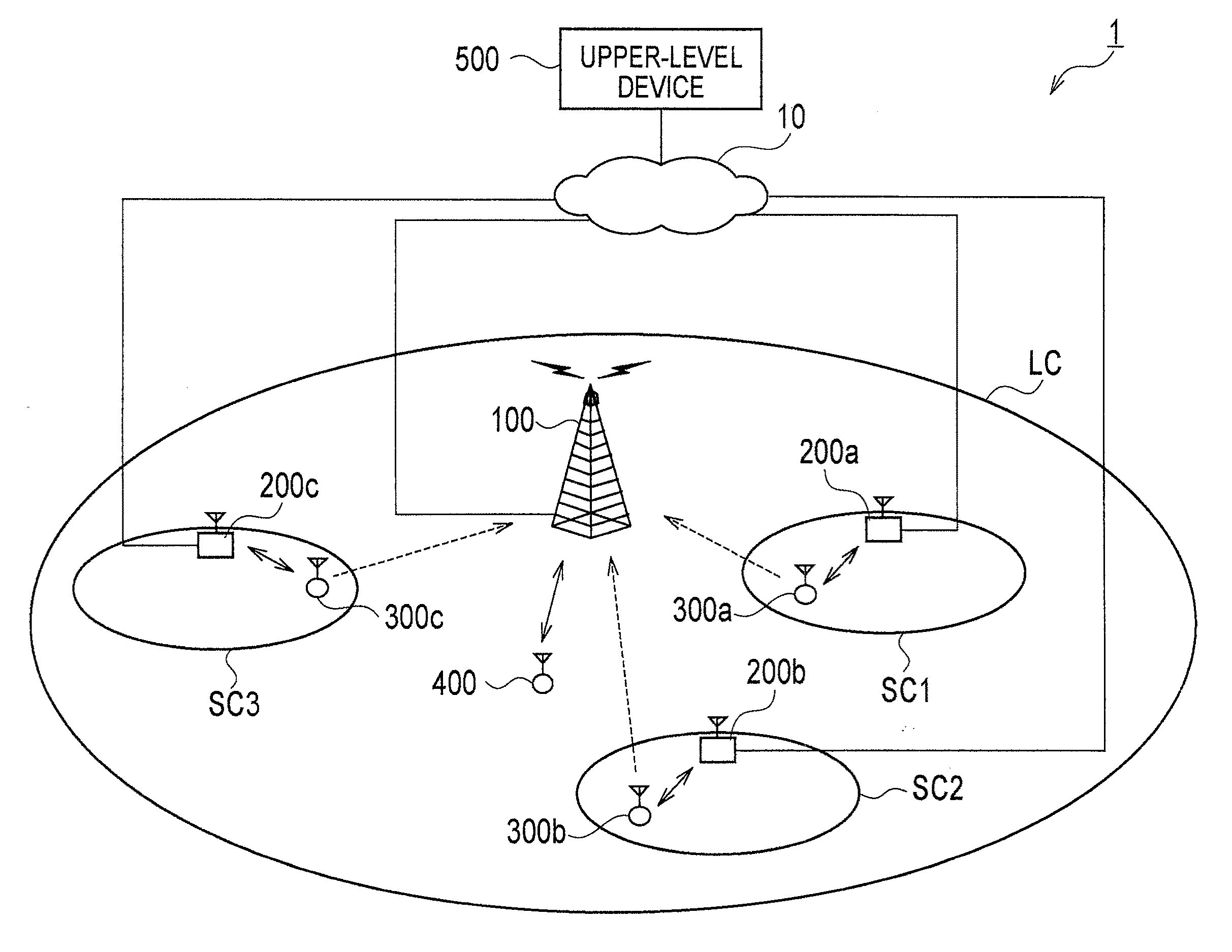

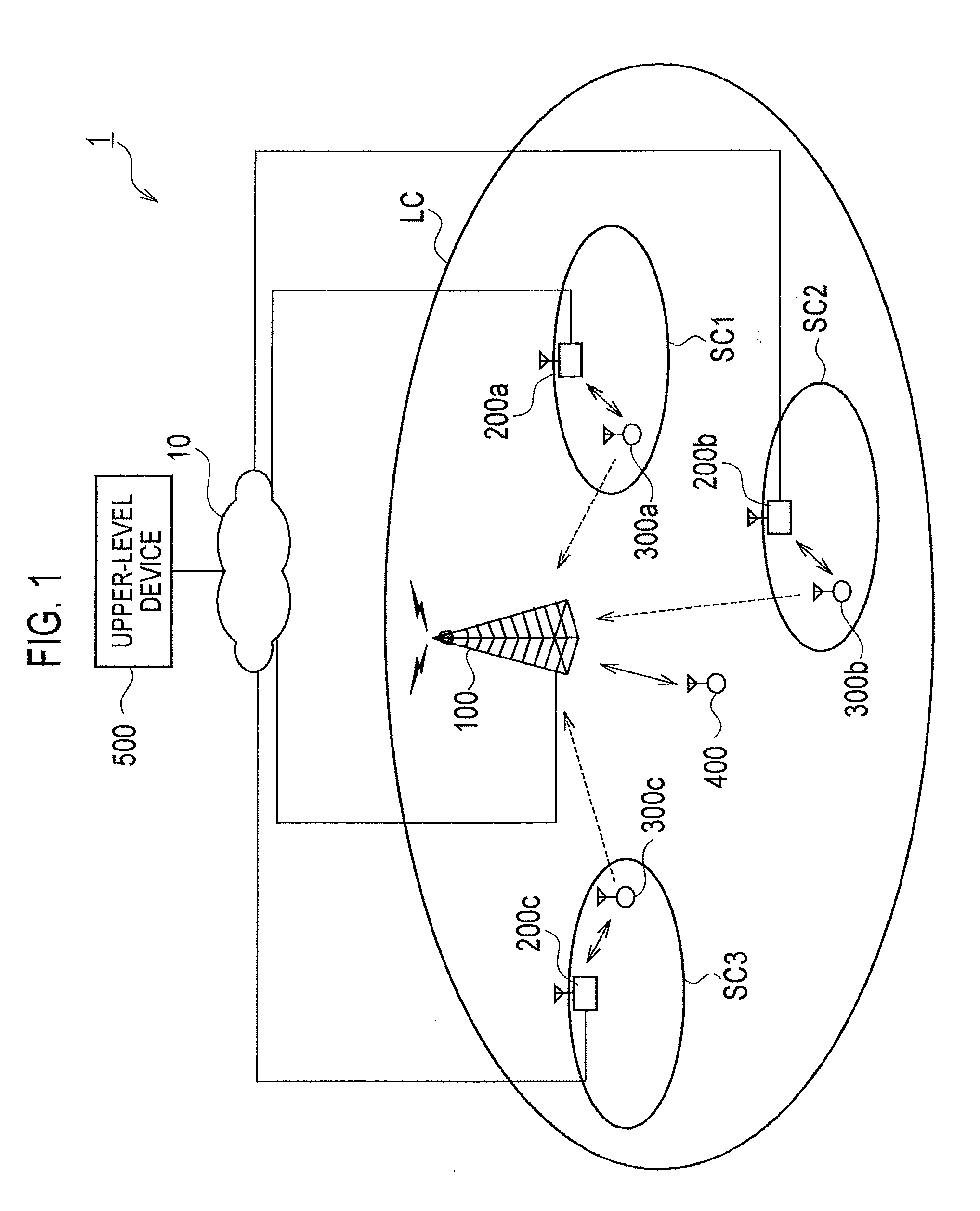

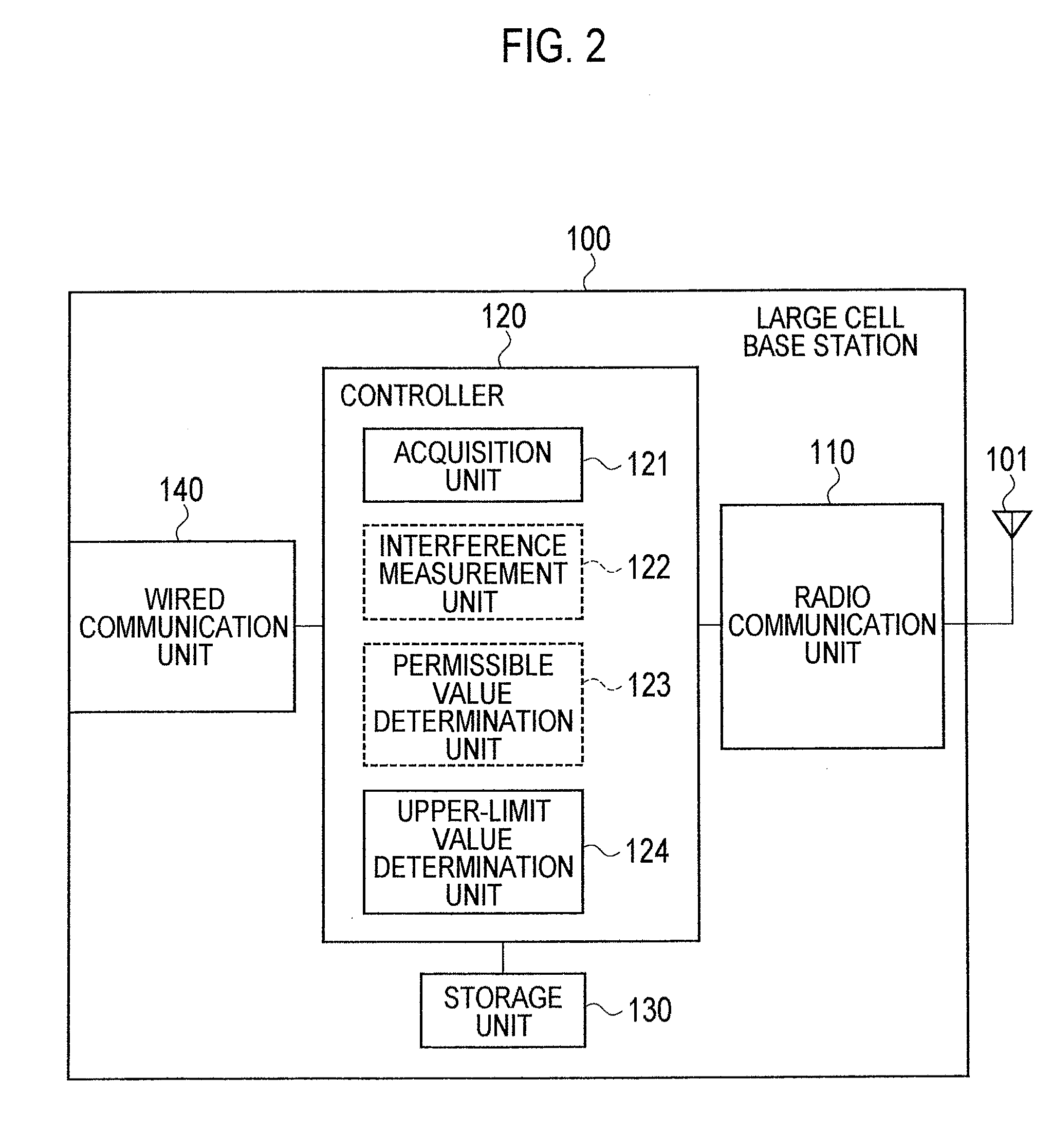

Radio communication system, network side device, small cell base station, and transmission power control method

ActiveUS20110086665A1Reduce rateReduce transmissionPower managementBroadcast transmission systemsWired communicationCommunications system

A large cell base station 100 according to an embodiment is configured to form a large cell and includes: an upper-limit value determination unit 124 configured to determine an upper-limit value Icap of an amount of interference which is received by the large cell base station from each of the radio terminals based on a permissible value Itotal of a total amount of interference which is received by the large cell base station from the radio terminals and the number of the small cell base stations within the large cell; and a wired communication unit 140 configured to transmit upper-limit value information indicating the upper-limit value Icap determined by the upper-limit value determination unit 124 to the small cell base stations.

Owner:KYOCERA CORP

Exhaust purifying apparatus and exhaust purifying method for internal combustion engine

During sulfur release control in an internal combustion engine, a rich period and a lean period are alternately repeated. The air-fuel ratio of exhaust gas is controlled toward a target air-fuel ratio (14.3) by adding fuel from a fuel adding valve in the rich period. An ECU determines whether the actual air-fuel ratio of exhaust gas detected by an air-fuel ratio sensor has reached a stoichiometric air-fuel ratio each time the rich period ends at which addition of fuel from the fuel adding valve is stopped. A counter counts the number of times the ECU has determined that the actual air-fuel ratio of exhaust gas has not reached the stoichiometric air-fuel ratio. When the value of the counter becomes greater than or equal to a permissible value, the ECU determines that there is an abnormality in the sulfur release control.

Owner:TOYOTA JIDOSHA KK

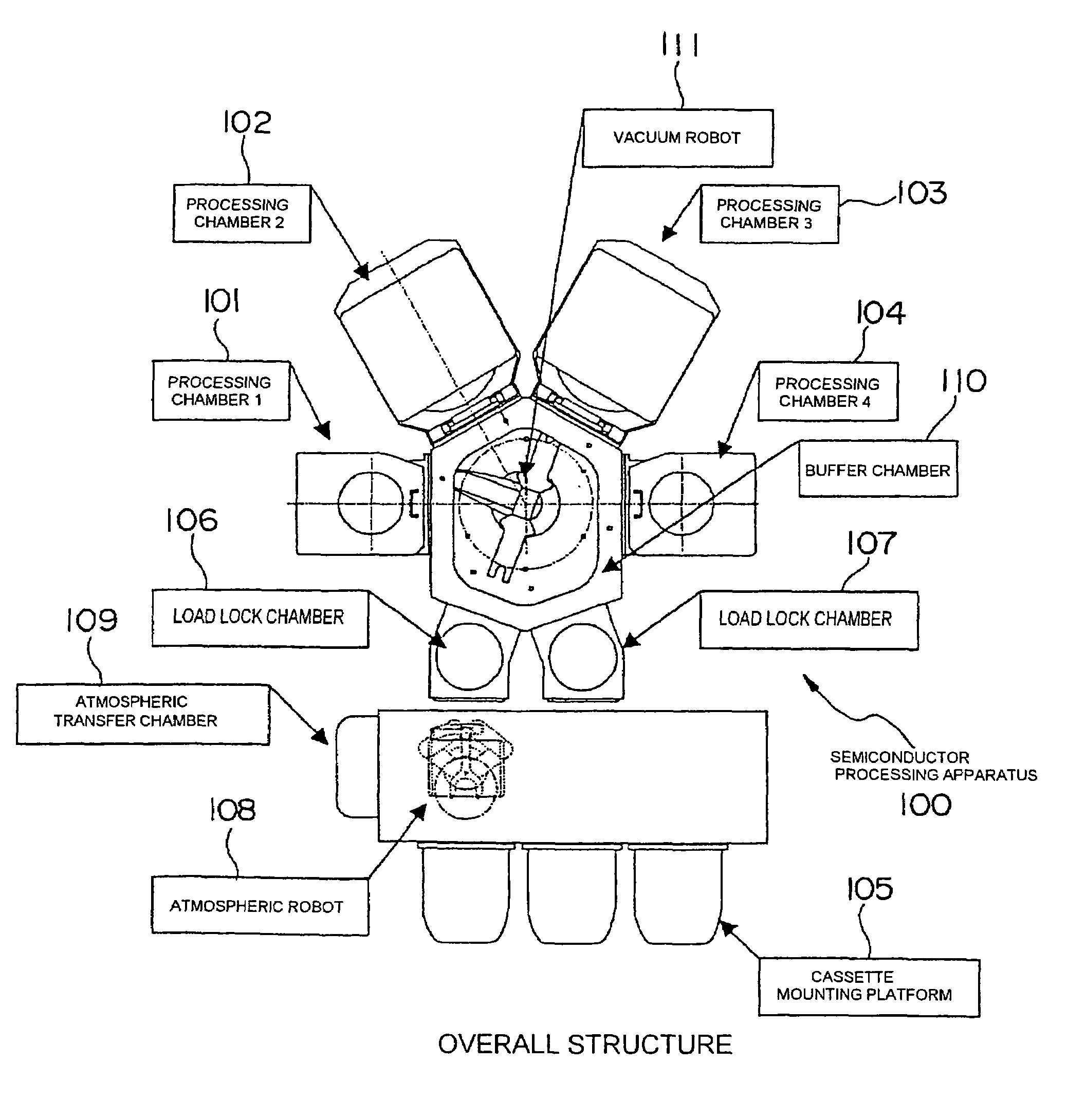

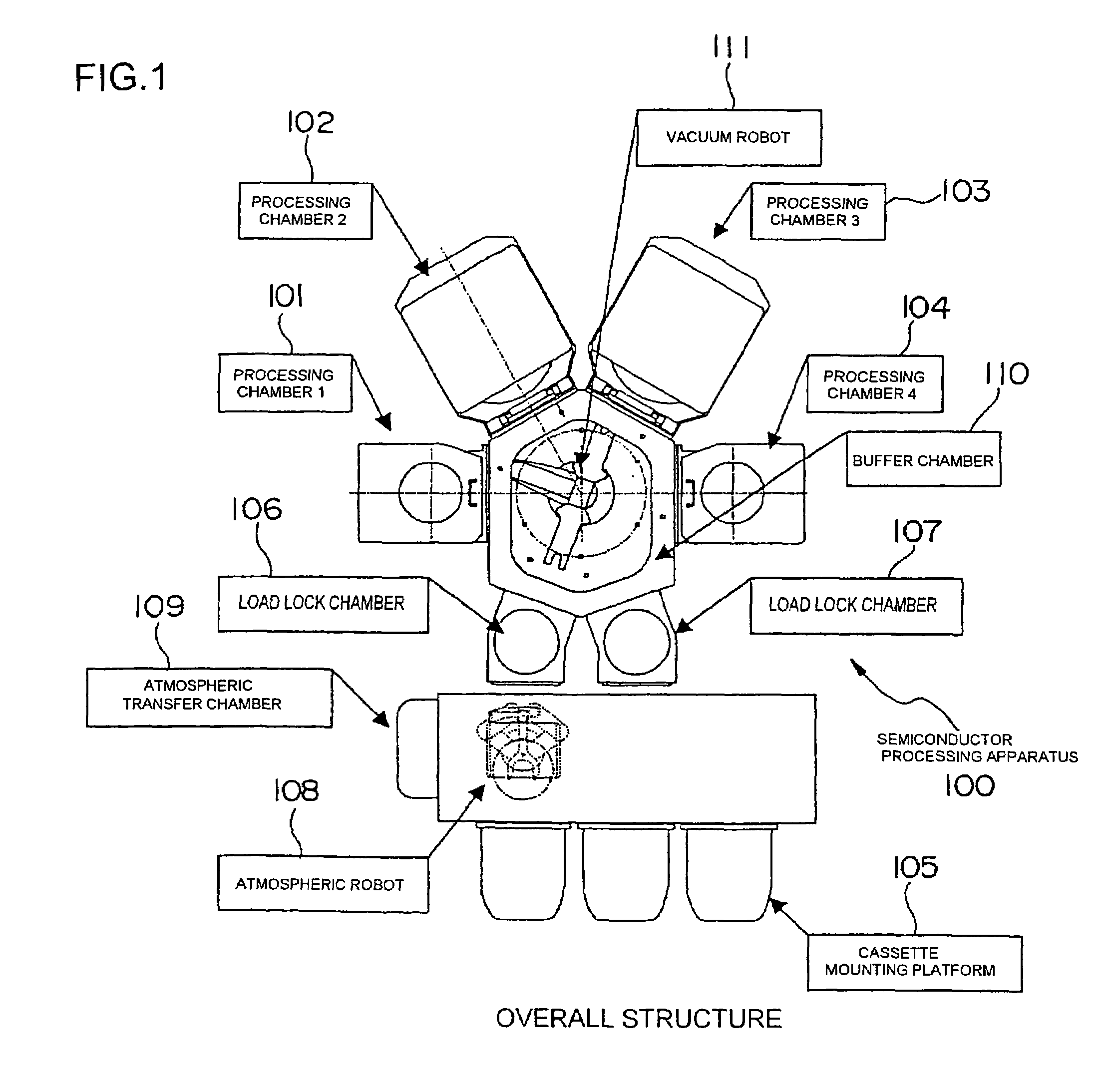

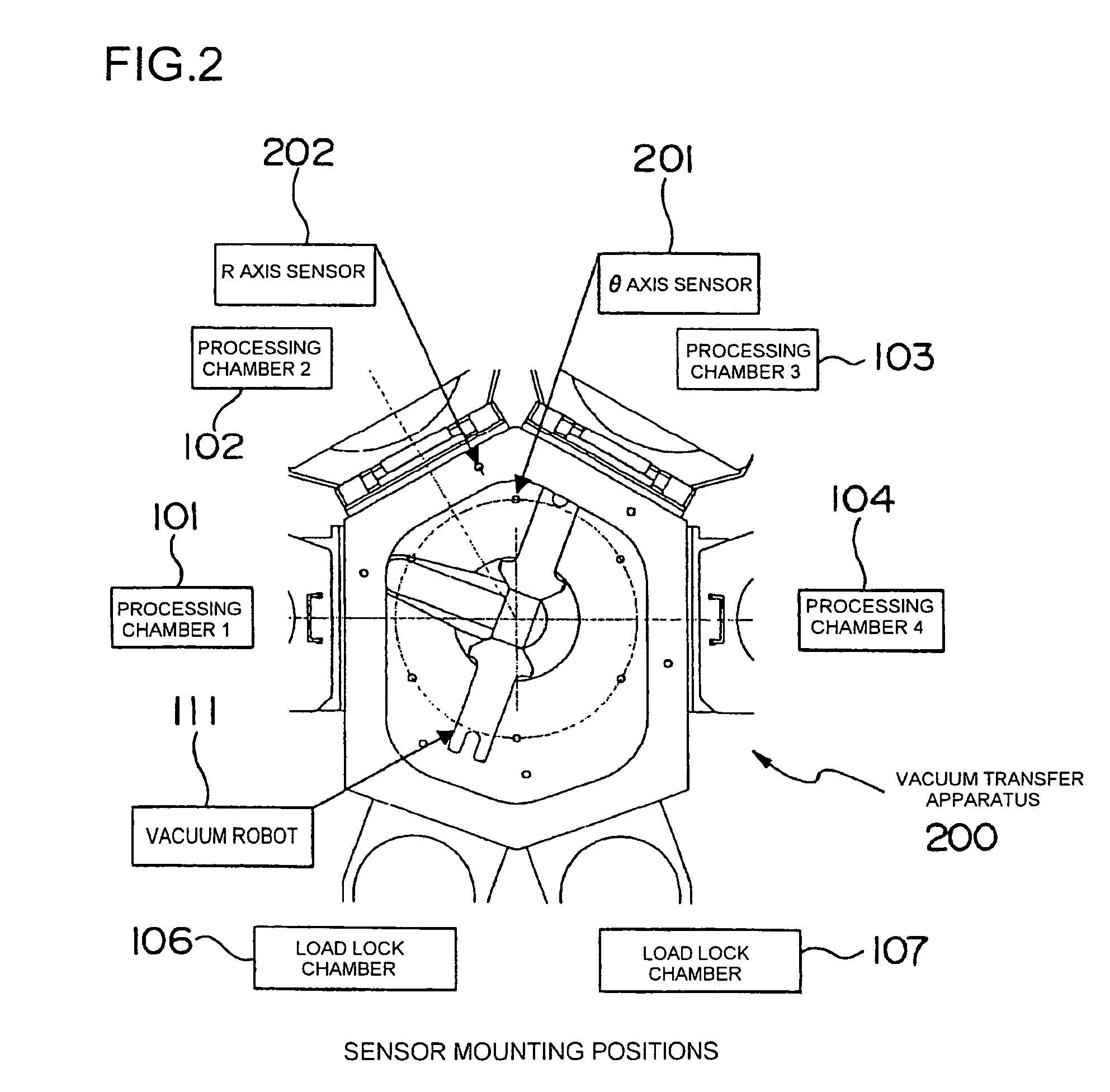

Vacuum processing method and vacuum processing apparatus

ActiveUS7353076B2Improve throughputSemiconductor/solid-state device manufacturingSpecial data processing applicationsDisplacement errorControl theory

The invention provides a semiconductor processing apparatus having a high throughput capable of appropriately coping with the positional displacement that may occur during transfer of the wafer after correcting the position thereof, without slowing down the transfer speed of the wafer. A position correction quantity of the wafer with respect to a vacuum robot is computed based on the outputs of a θ axis sensor for detecting the interception angle of the wafer during rotation of the vacuum robot and an R axis sensor for detecting the interception distance of the wafer during expansion and contraction of the vacuum robot. If the position correction quantity exceeds a predetermined standard value, an operation to change the position data is performed, and if the distance data obtained based on the outputs from the θ axis sensor and the R axis sensor exceeds a predetermined permissible value, it is determined that a displacement error has occurred and the operation is stopped.

Owner:HITACHI HIGH-TECH CORP

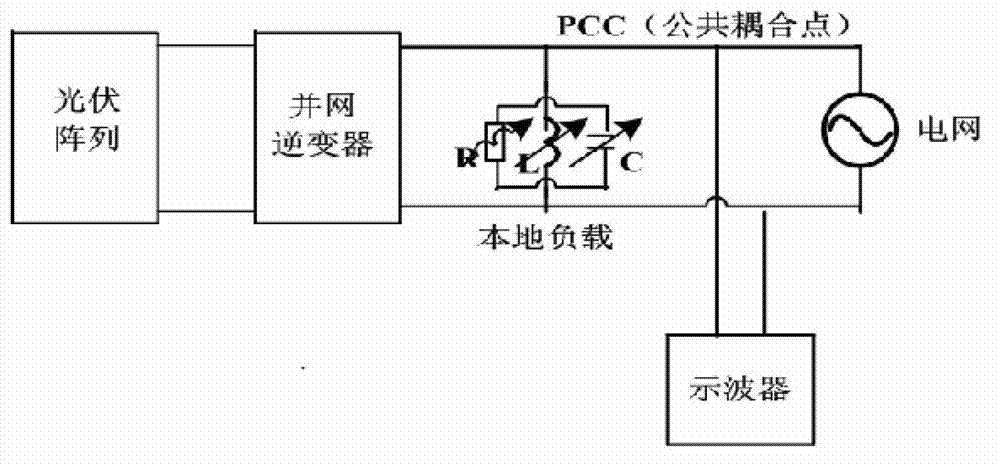

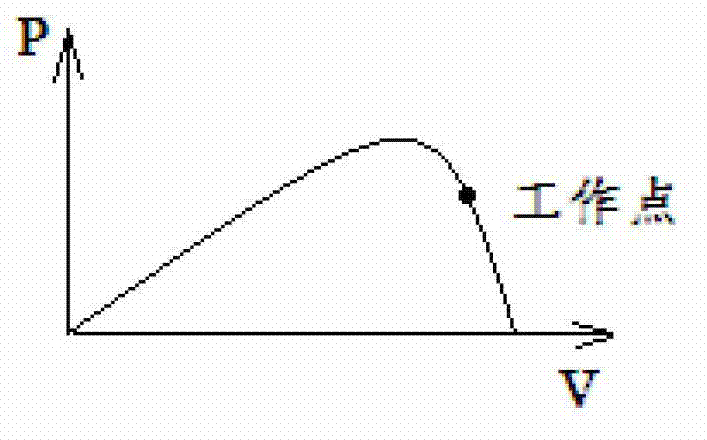

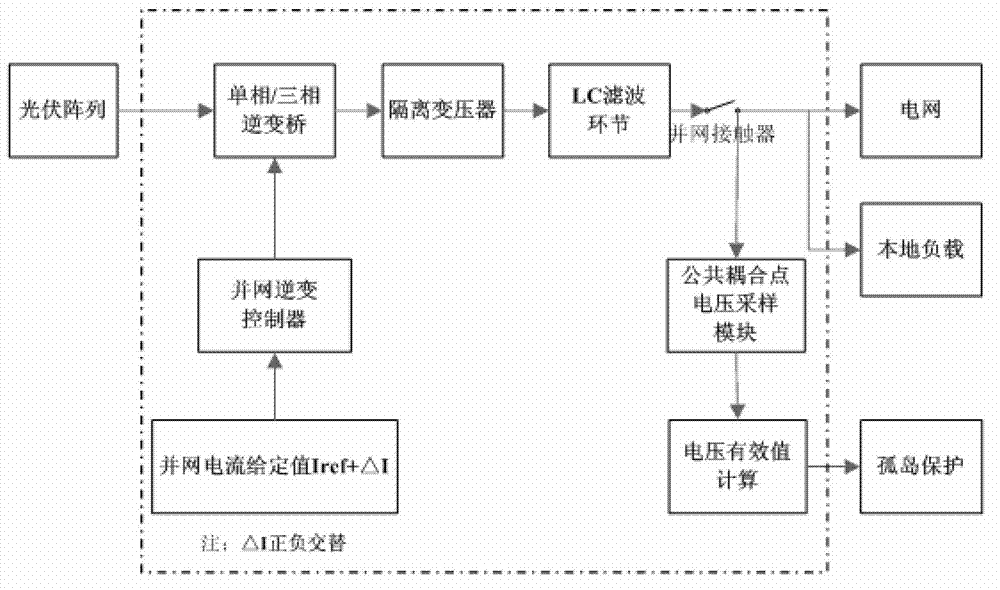

Bidirectional active power disturbance island detection method

InactiveCN102879672AEliminate detection blind spotsReduce harmonic contentElectrical testingIslandingCoupling

The invention discloses a bidirectional active power disturbance island detection method. The method comprises the following steps of: adding the disturbance quantity of positive and negative delta I into grid-connected current; calculating an absolute value of difference between Uold and Unew; comparing the absolute value of the difference between the Uold and the Unew with a set maximum permissible value of voltage difference between the Uold and the Unew; and if frequency that the absolute value of the difference between the Uold and the Unew is continuously greater than the set maximum permissible value of the voltage difference between the Uold and the Unew is greater than or equal to a set value, detecting an island phenomenon. By adoption of the bidirectional active power disturbance island detection method, the island phenomenon can be timely and effectively detected, and harmonic wave is slightly introduced to a common coupling point.

Owner:CHINA EPRI SCIENCE & TECHNOLOGY CO LTD

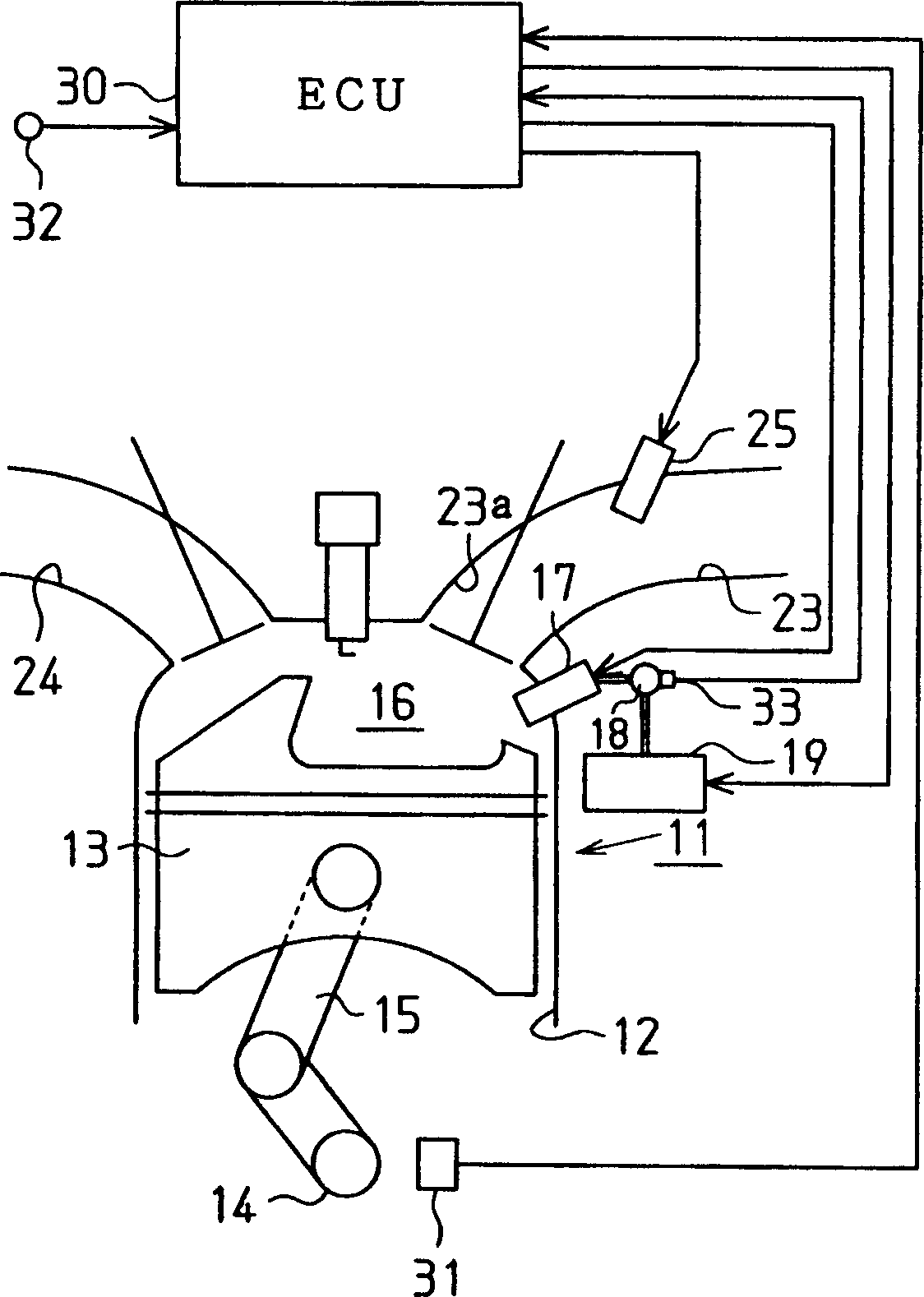

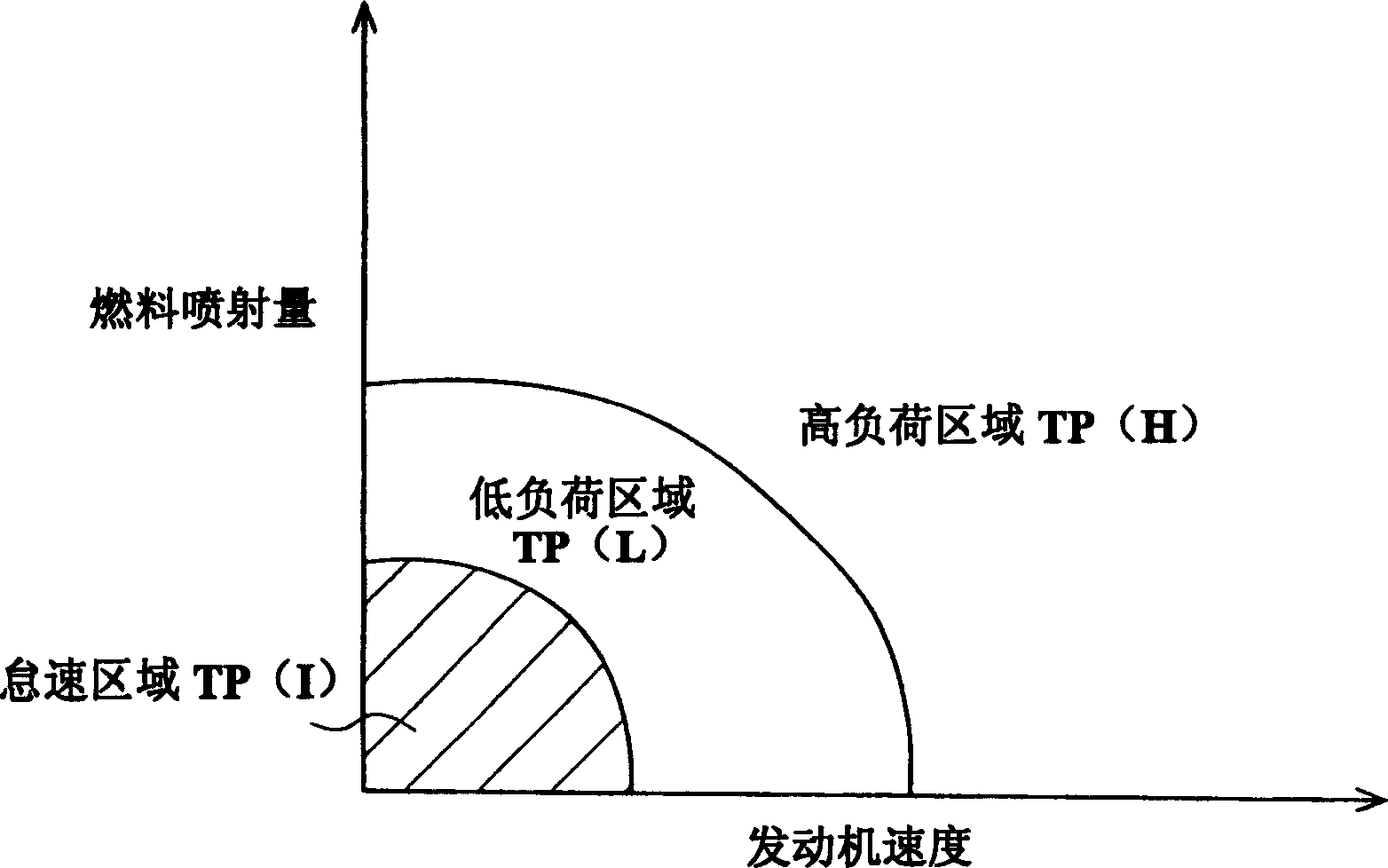

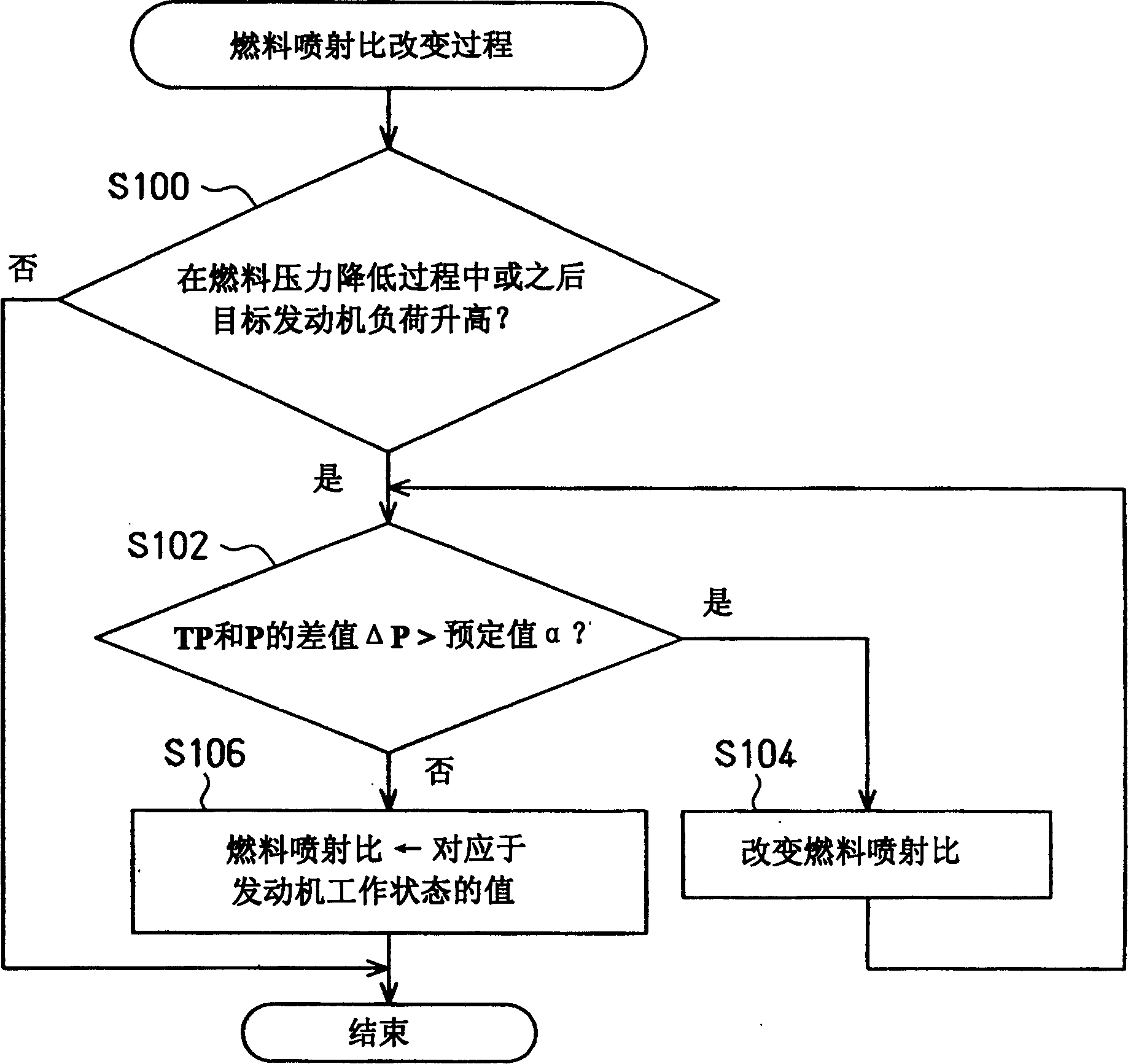

Engine fuel injection device and engine fuel injection method

InactiveCN1664340AInhibitionElectrical controlInternal combustion piston enginesCombustion chamberFuel supply

A fuel injection device for an engine includes a direct injector and an intake passage injector. When the engine load is relatively low, a fuel pressure lowering procedure is executed for lowering the pressure of fuel supplied to the direct injector. An ECU sets a fuel injection ratio, which is the ratio between the fuel injection amount of the direct injector and that of the intake passage injector, based on the engine operation state. The ECU changes the fuel injection ratio such that the ratio of the fuel injection amount of the direct injector to the total amount of the fuel fed to a combustion chamber is decreased, until the pressure of the fuel supplied to the direct injector is raised from the value lowered through the fuel pressure lowering procedure to a predetermined permissible value. This effectively suppresses hampering of the engine combustion, caused by the lowered fuel pressure.

Owner:TOYOTA JIDOSHA KK

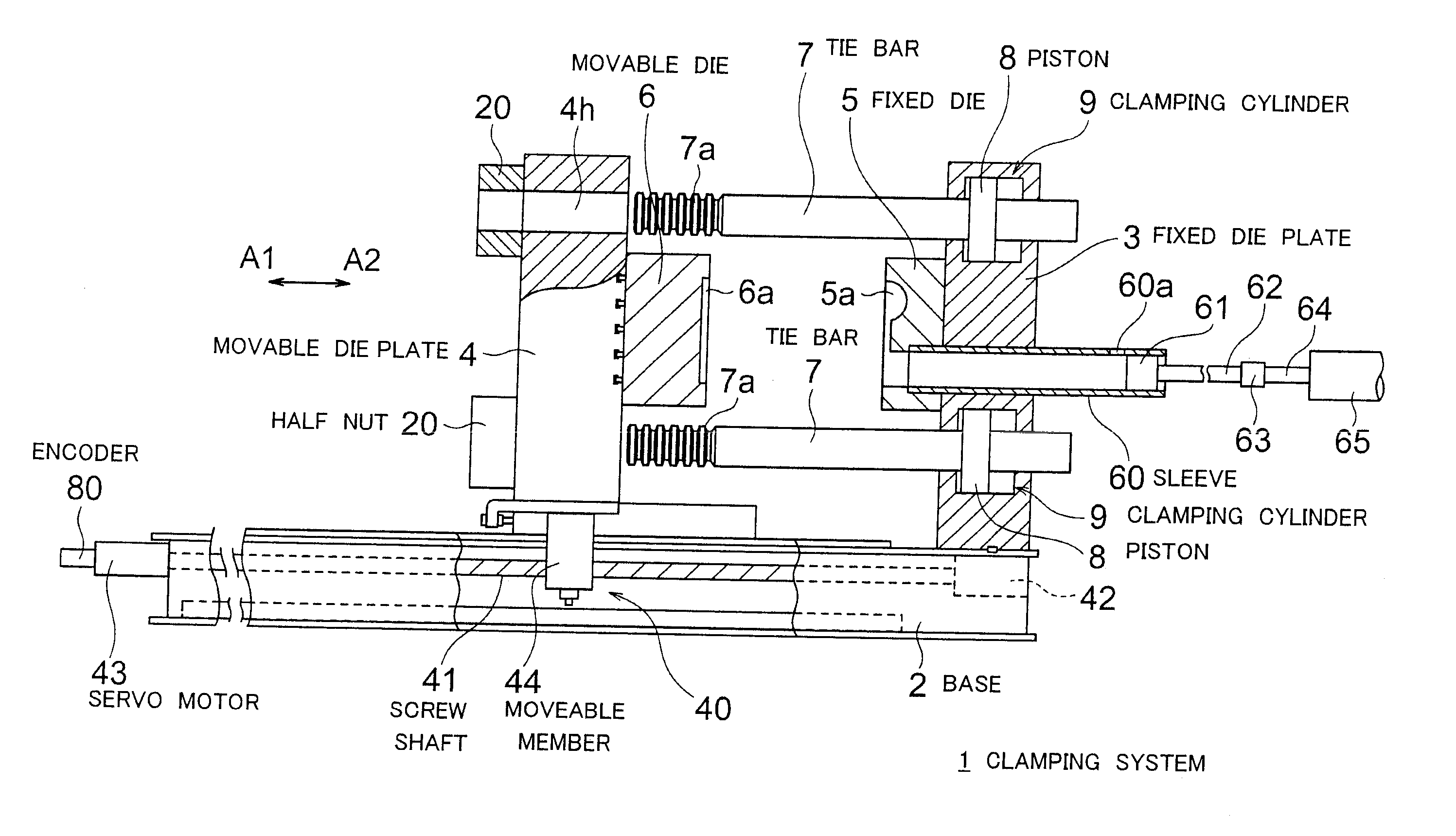

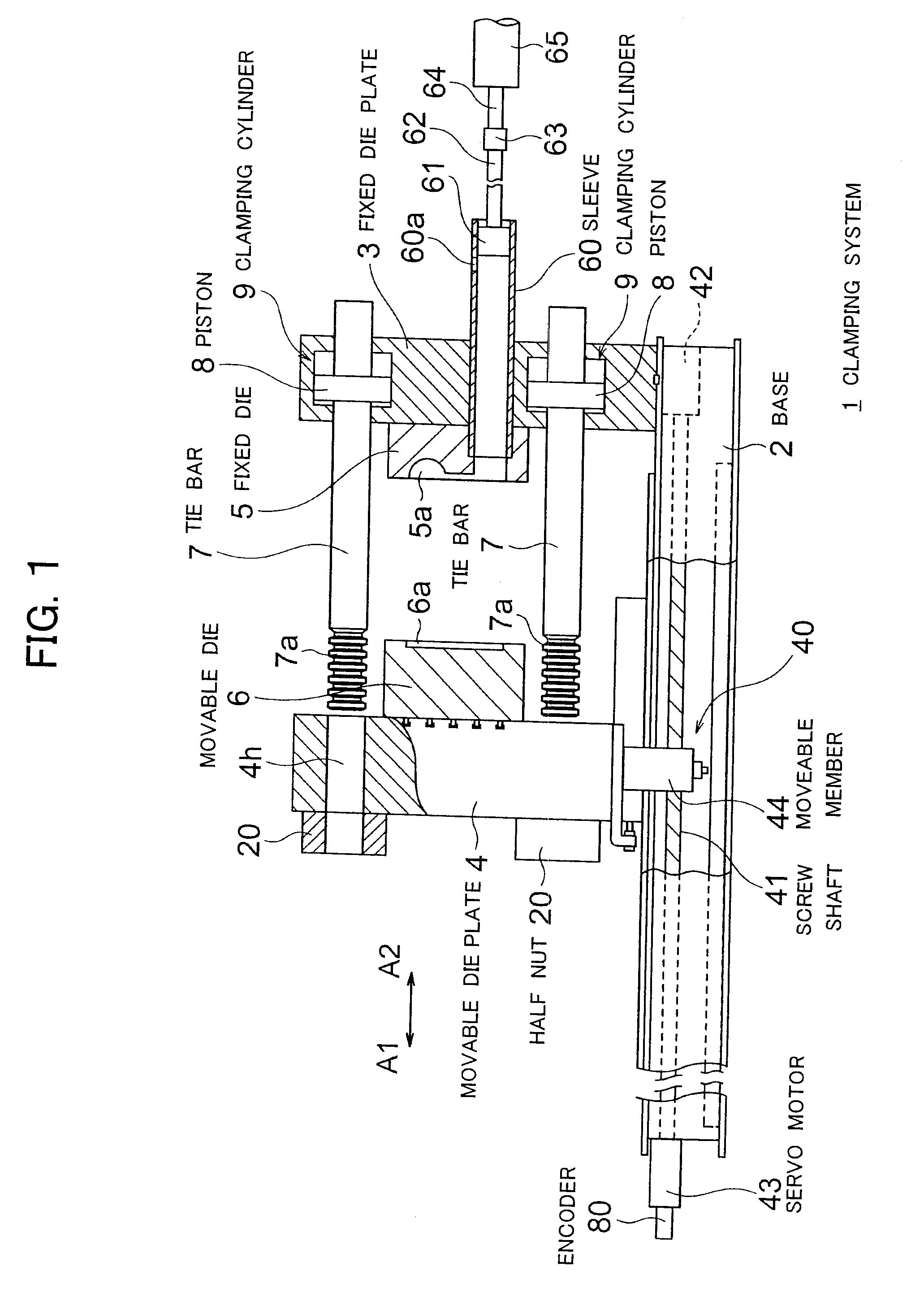

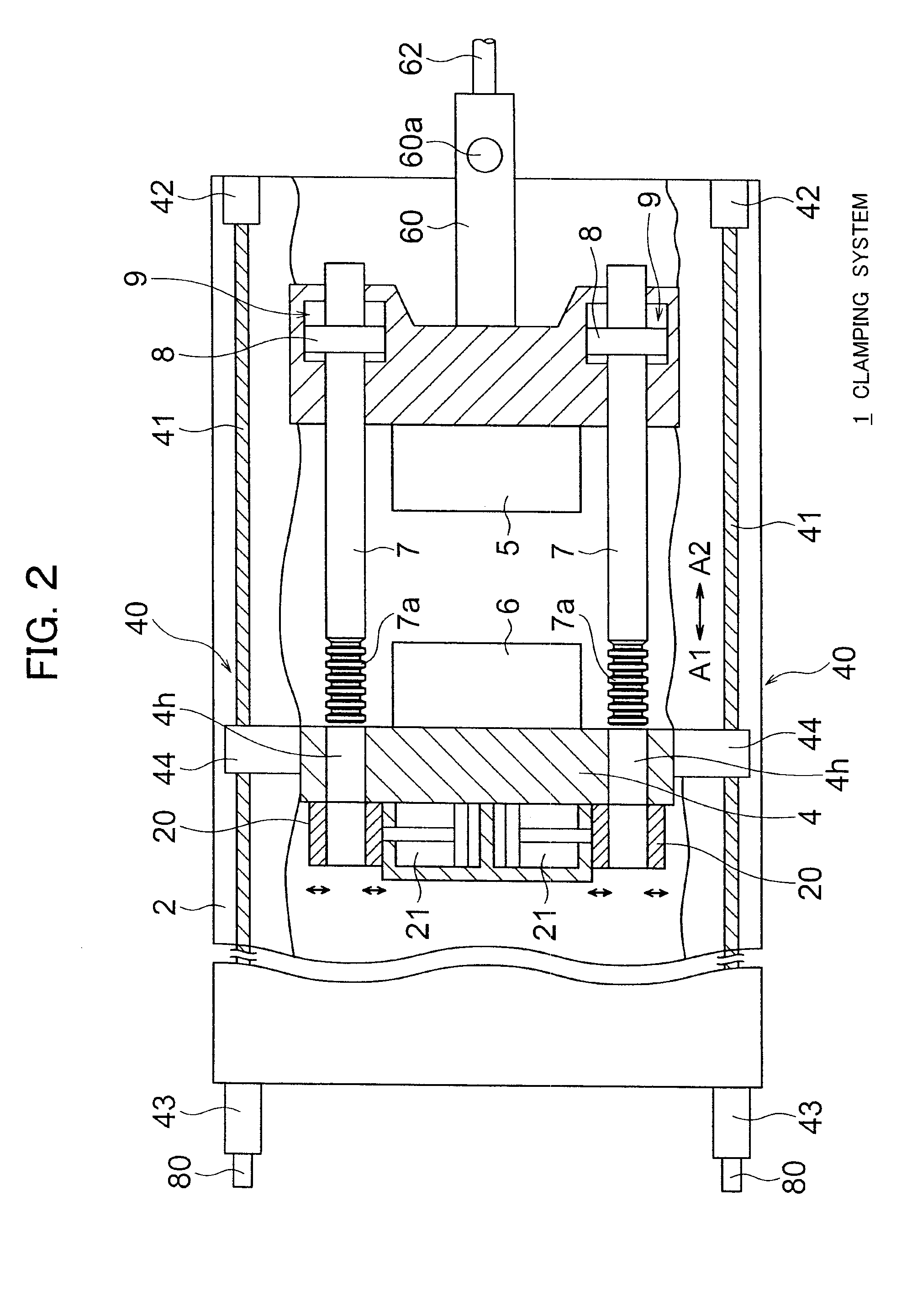

Clamping system and clamping method

InactiveUS20070048398A1Suppress degradation of degree of parallelismCasting safety devicesWood working apparatusEngineeringControl valves

A clamping system provided with a fixed die plate, a movable die plate, a plurality of tie bars, half nuts able to be coupled with or release coupled parts of a plurality of tie bars, clamping cylinders accommodating pistons of a plurality of tie bars, position sensors detecting positions of pistons, a plurality of direction control valves connected to a plurality of clamping cylinders, and a control unit controlling the plurality of direction control valves so that a difference of movement amounts of pistons among the plurality of tie bars from the time of die contact to the time of the completion of clamping becomes within a predetermined permissible value based on detection results of the position sensors.

Owner:TOSHIBA MASCH CO LTD

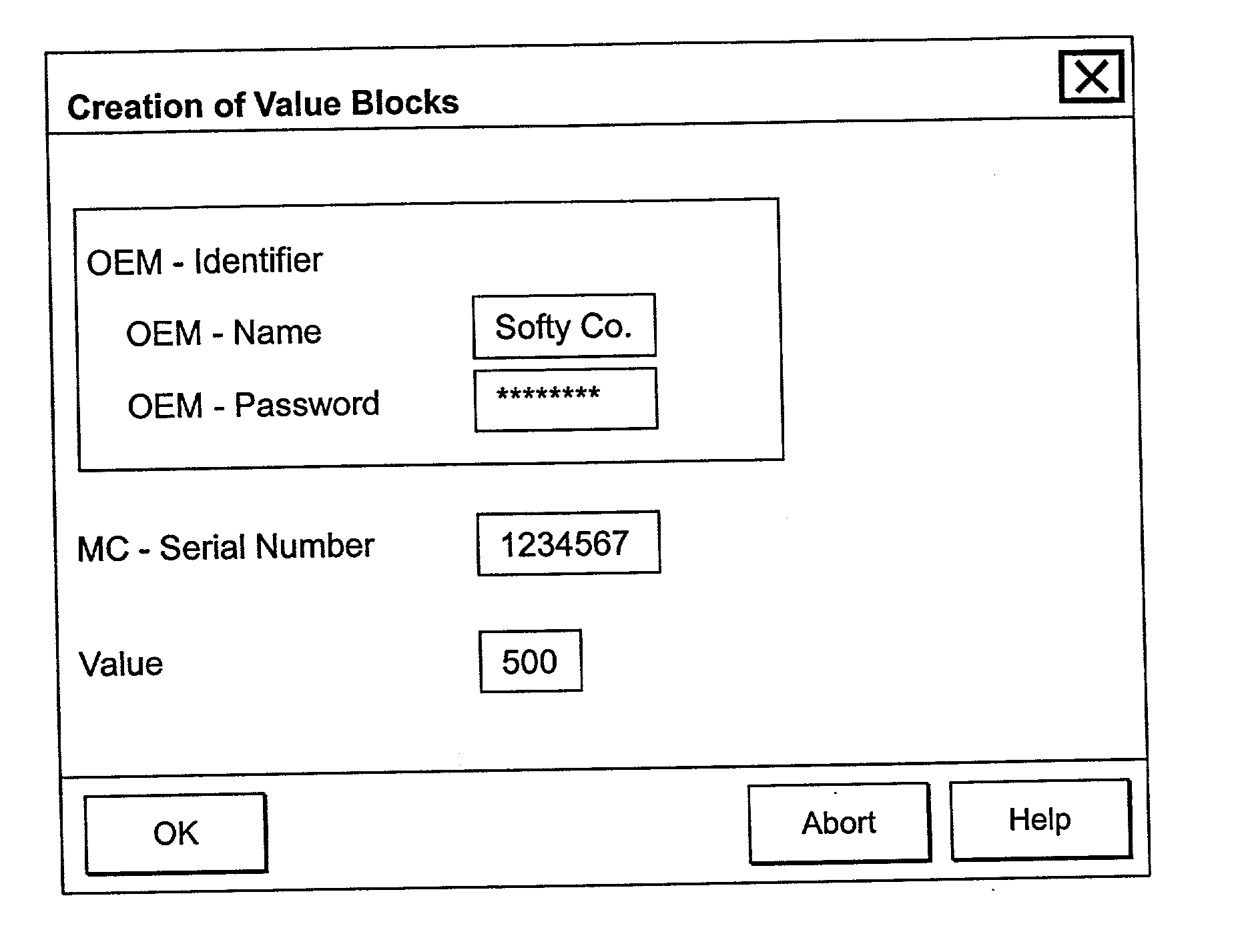

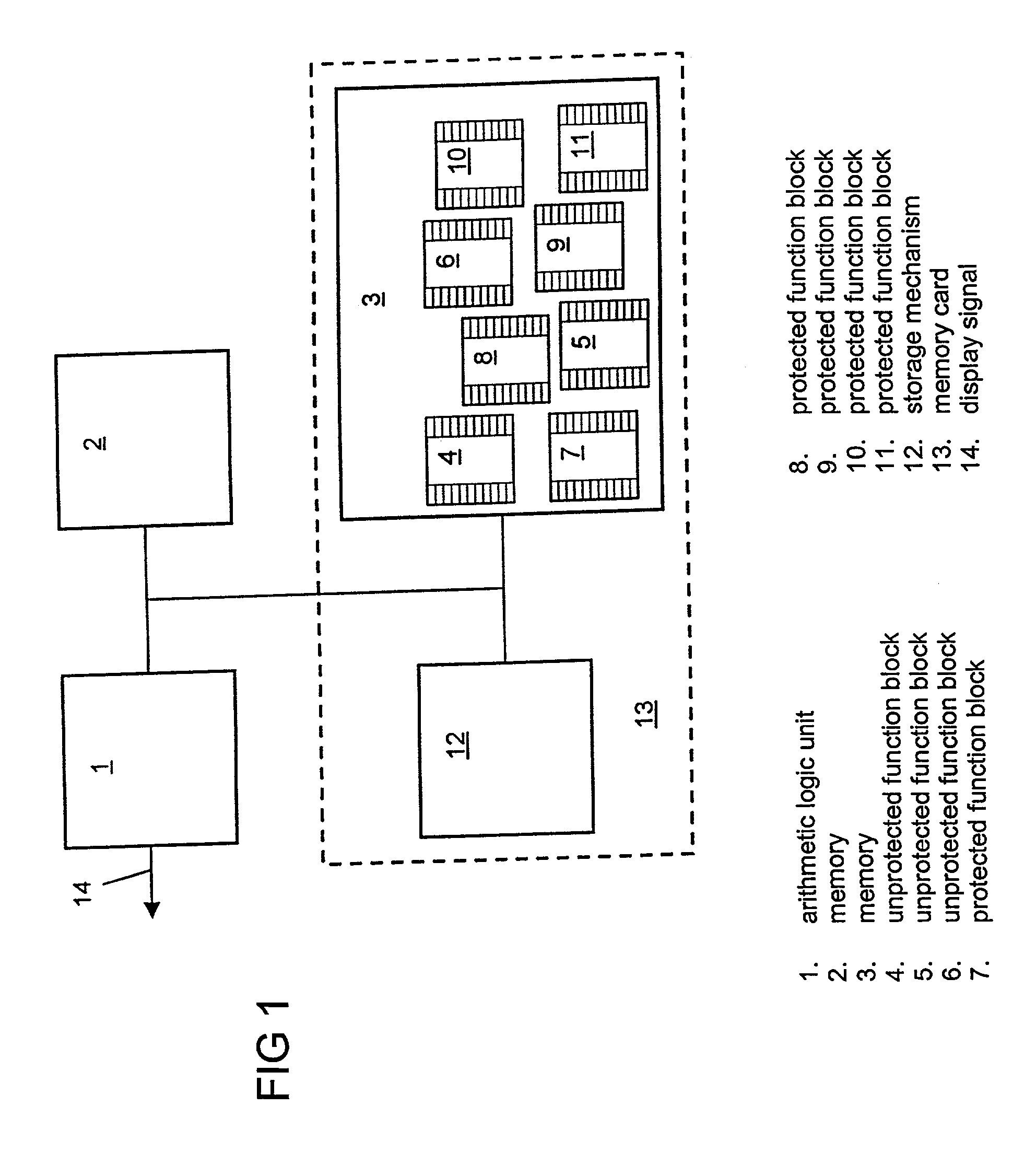

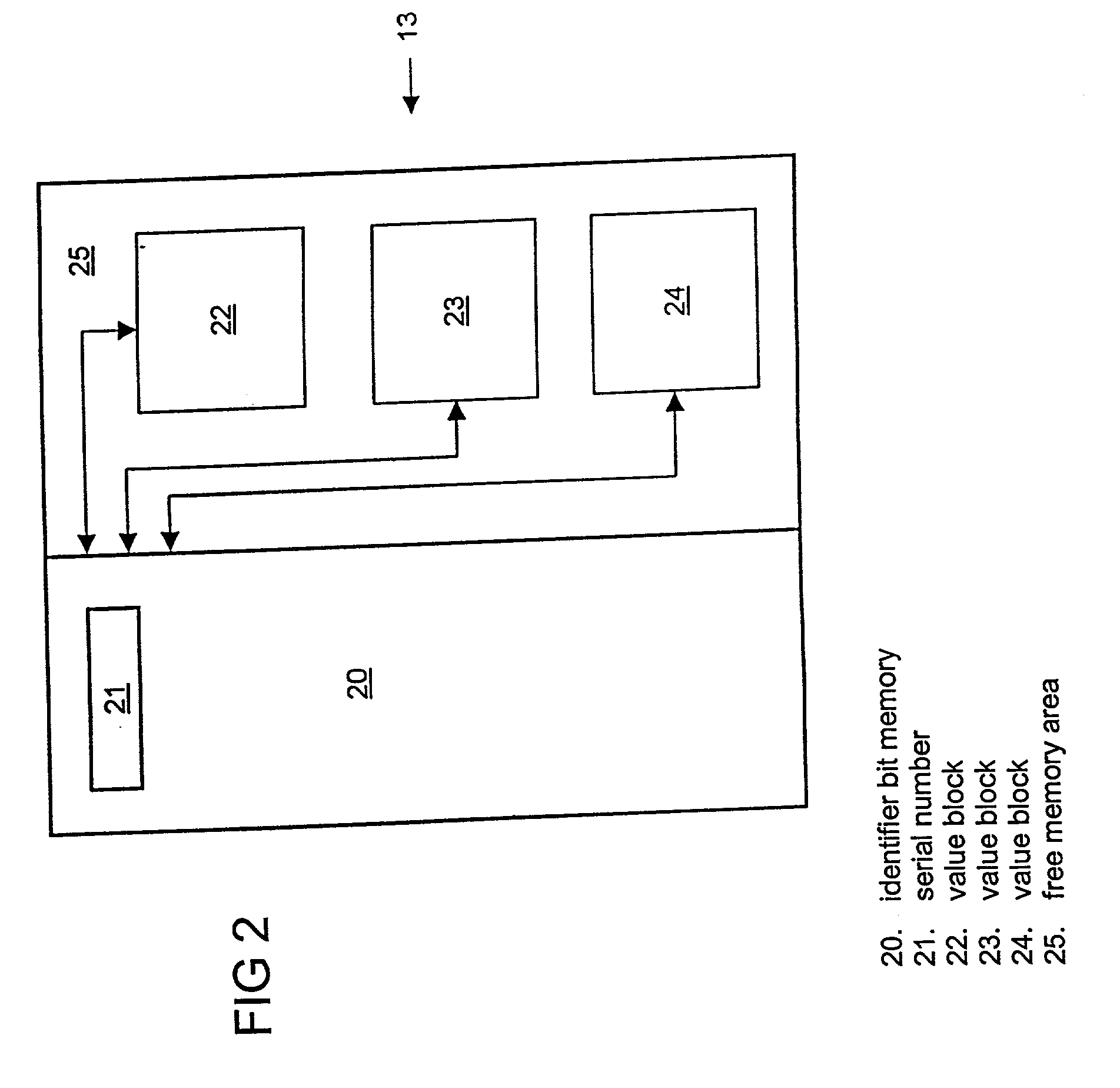

Electronic device for providing software protection

InactiveUS20020129270A1Increase valueBlock valueDigital data processing detailsCo-operative working arrangementsArithmetic logic unitSoftware protection

An electronic device with software protection for runtime software. At least one function block (4-11) of the runtime software has a priority value. A maximum permissible value for the runtime software is retrievably stored in one device (12). An arithmetic logic unit (1) determines the total value for the function blocks of the runtime software and a display signal (14) is output if the total value exceeds the maximum permissible value. Function blocks and value blocks can have an OEM identification code, such that the system manufacturer and OEM can, independently of each other, create a software protection.

Owner:SIEMENS AG

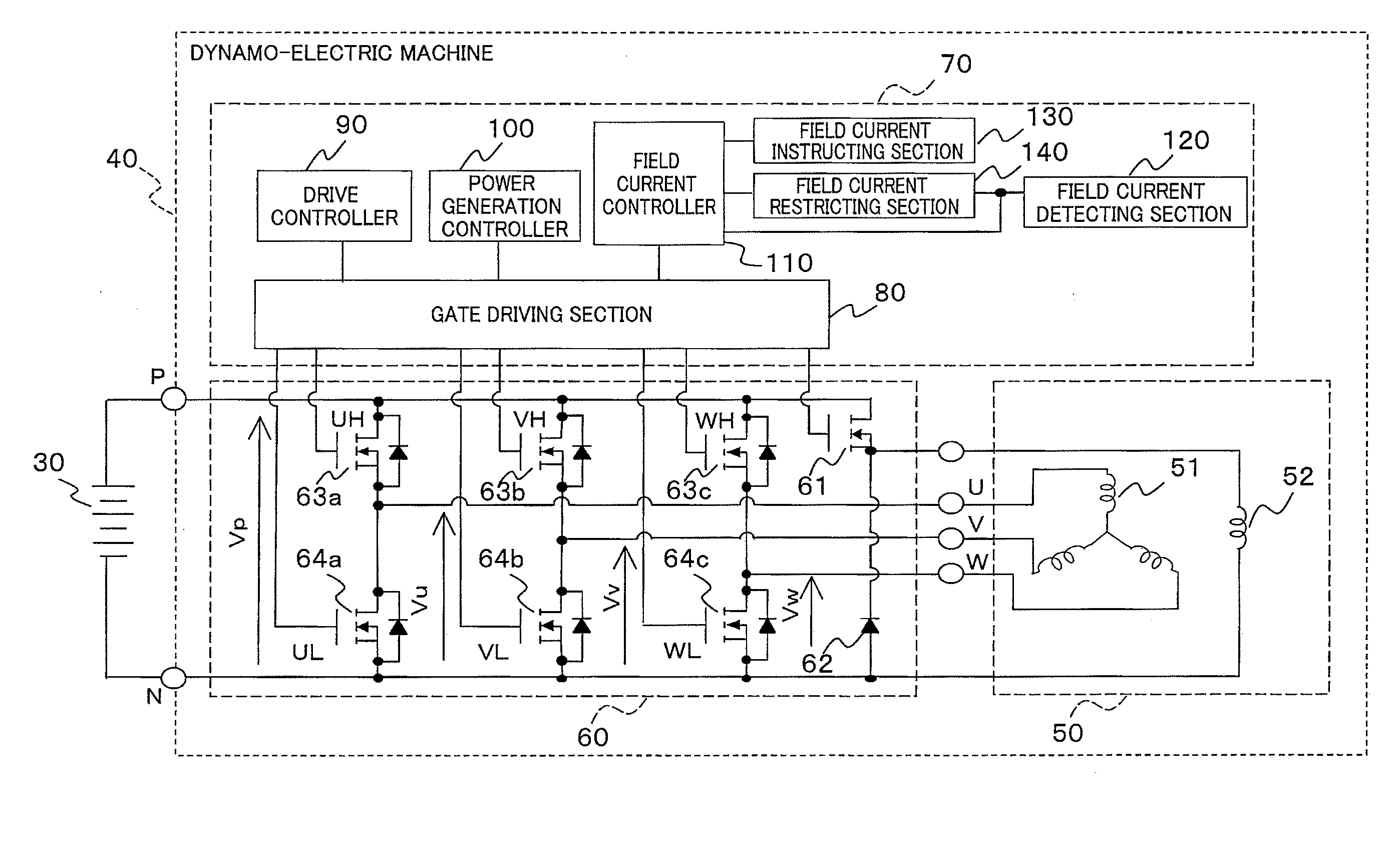

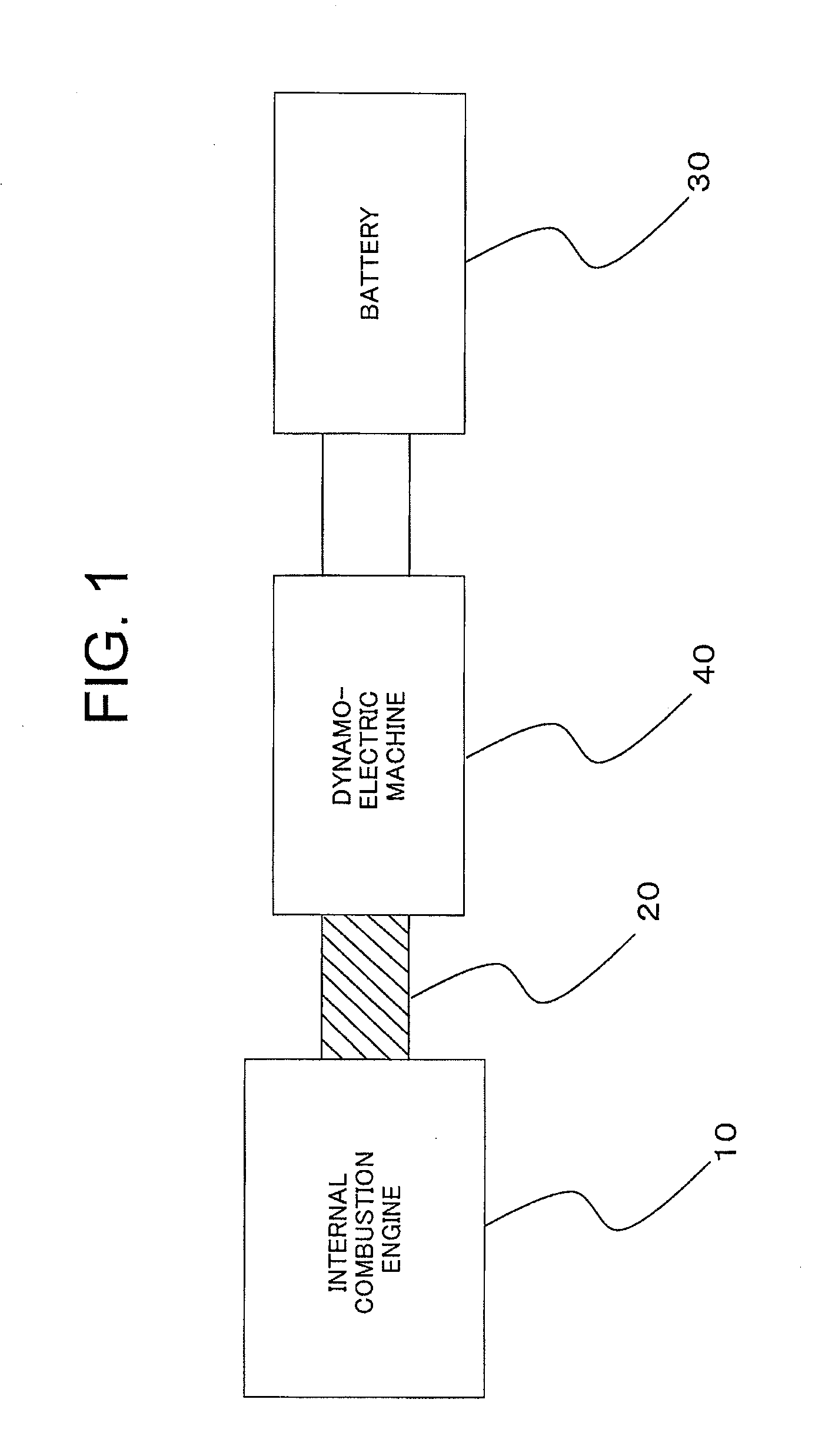

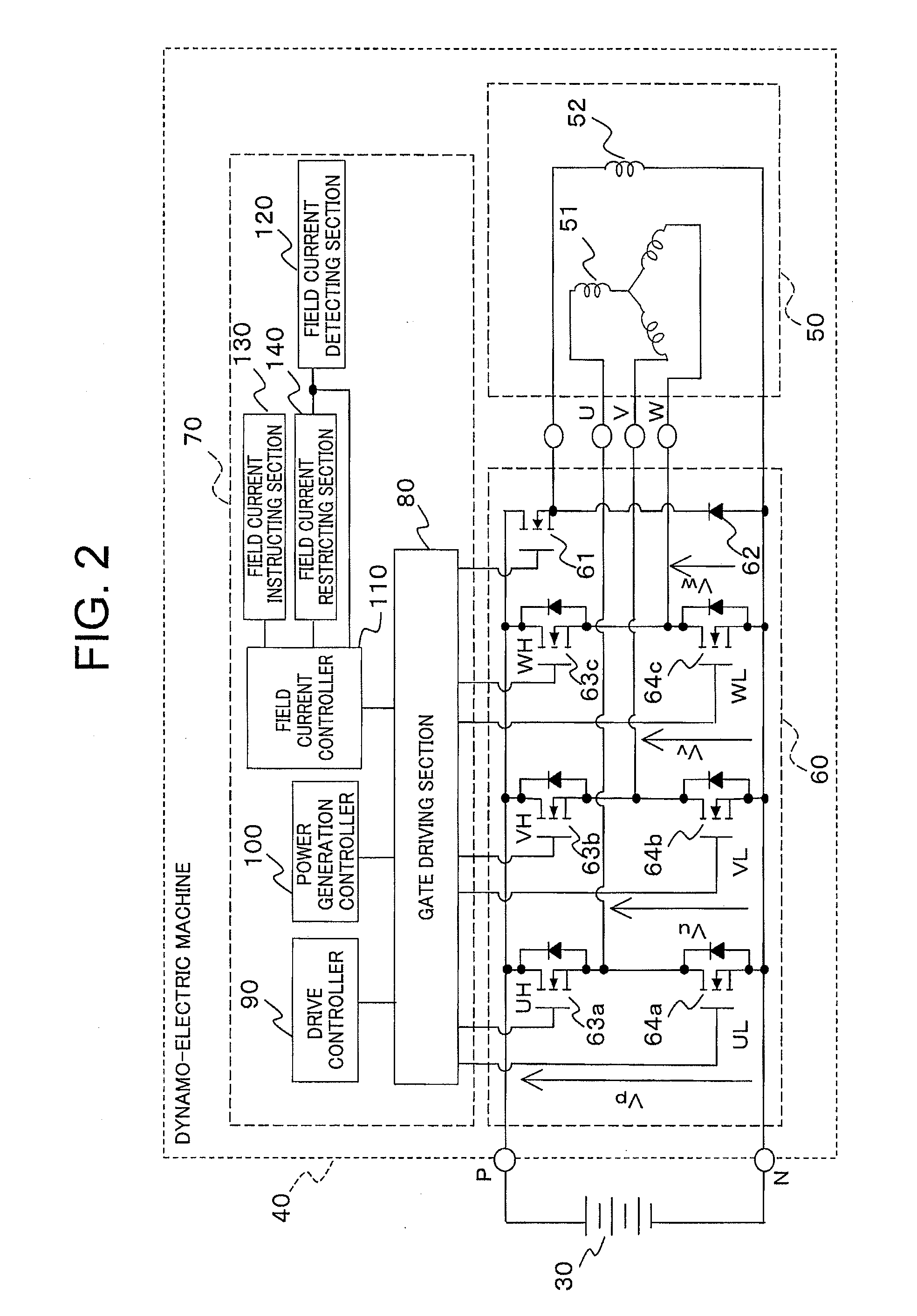

Field winding type generator-motor

ActiveUS20100301816A1Minimizing cost increaseMinimizing structure modificationElectric motor controlEmergency protective circuit arrangementsCurrent limitingElectric machine

Provided is a field winding type generator-motor capable of minimizing cost increase and structure modification while preventing a failure due to a temperature rise, without mounting a temperature sensor. The field winding type generator-motor according to the present invention includes: a dynamo-electric machine that has a field winding; a field current detecting section for detecting field current; a field current restriction deciding section for deciding whether or not the decision value has reached a predetermined decision threshold value by calculating a decision value based on the field current detected by the field current detecting section; and a field current controller for controlling the field current flowing in the field winding so that the field current is restricted to a predetermined permissible value in a case where the field current restriction deciding section decides that the decision value has reached the predetermined decision threshold value.

Owner:MITSUBISHI ELECTRIC CORP

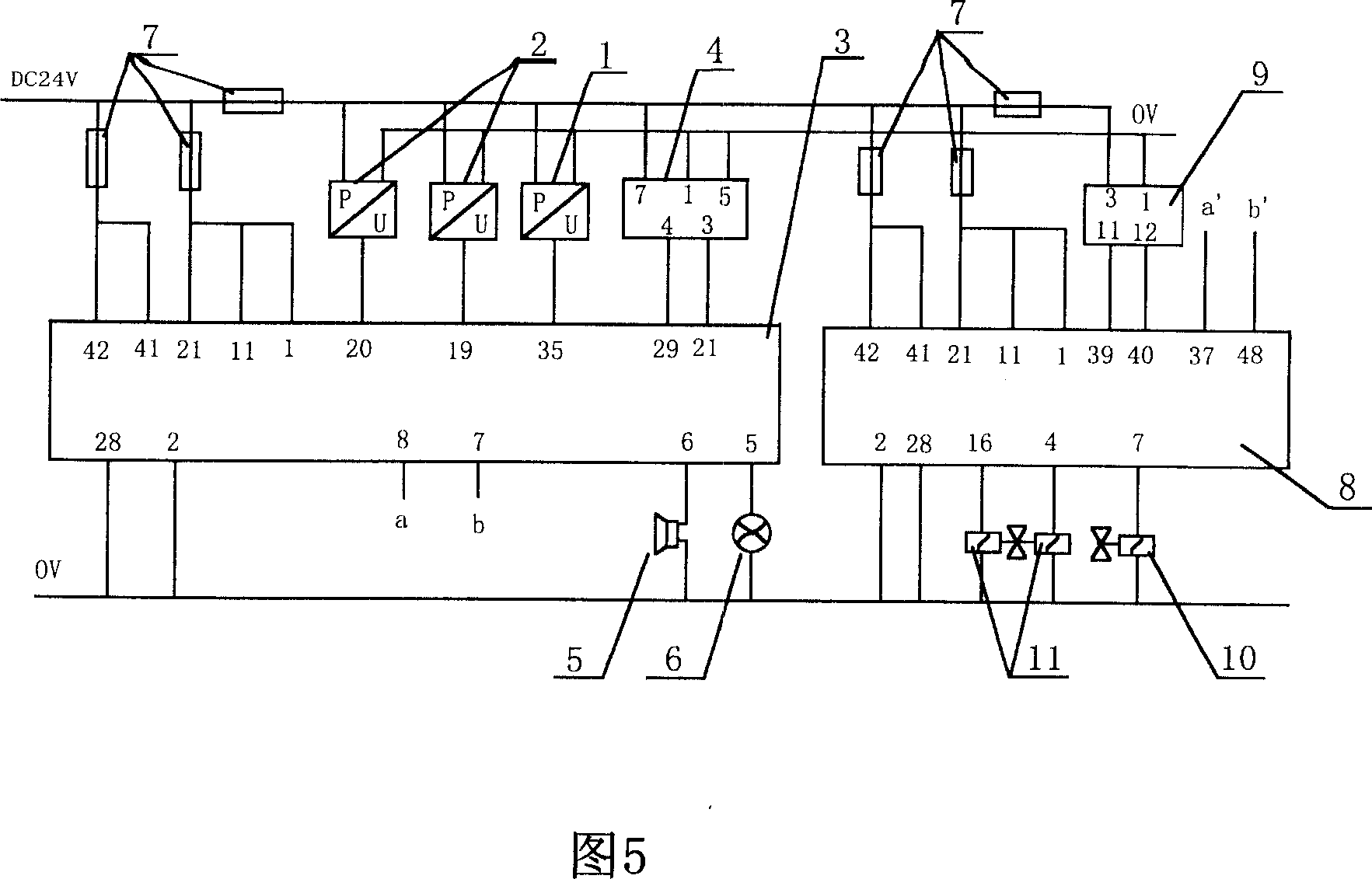

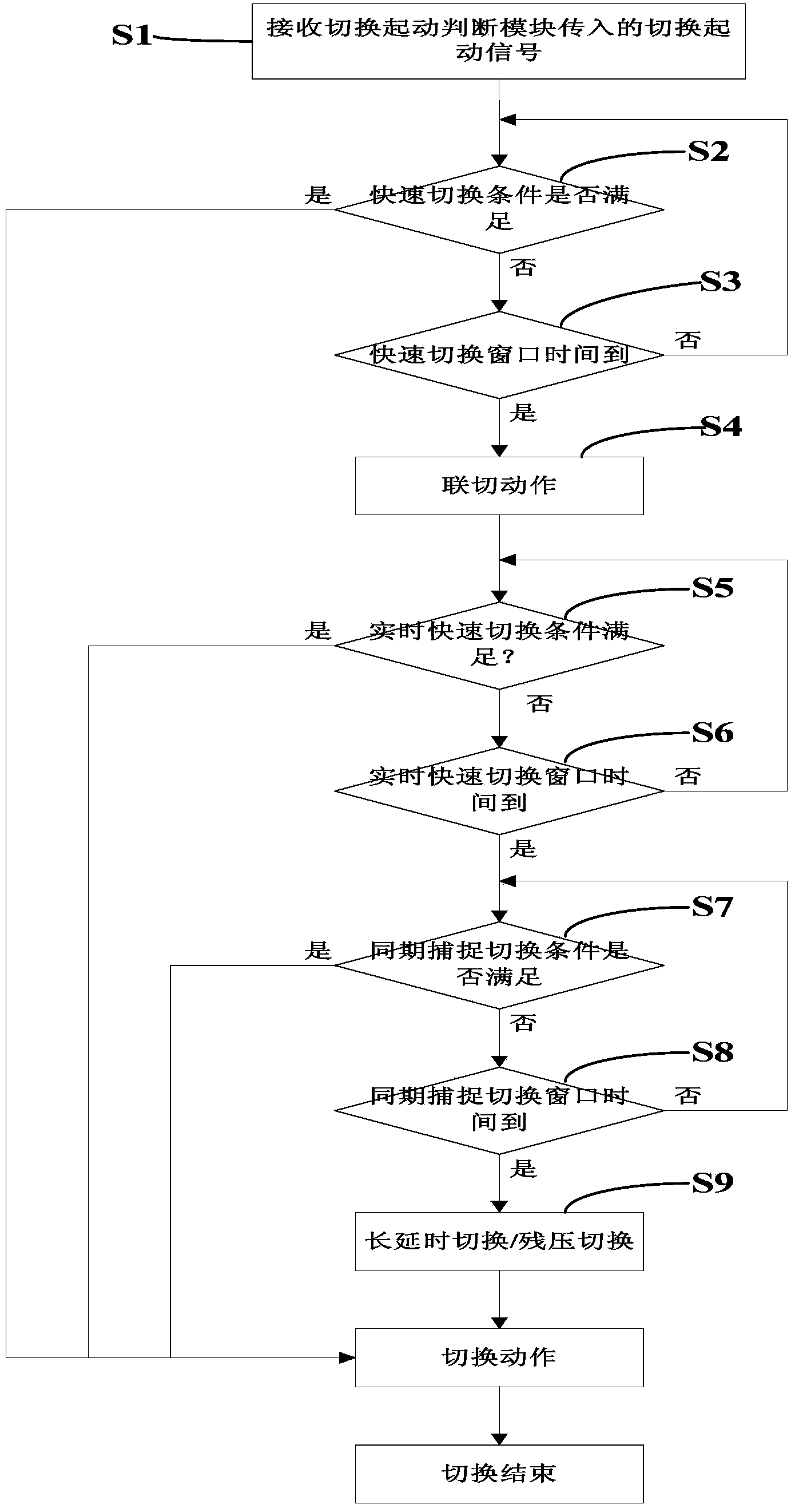

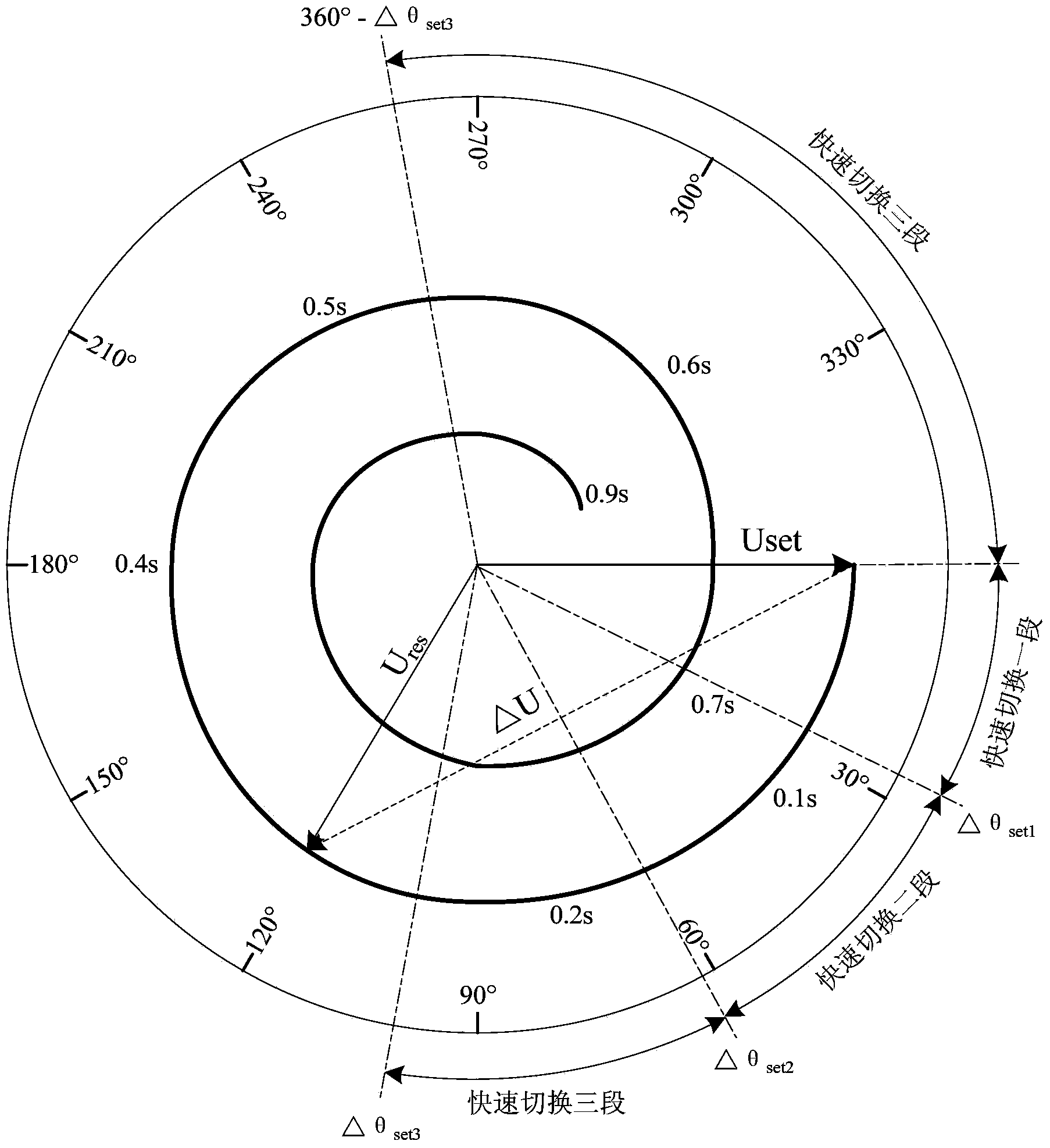

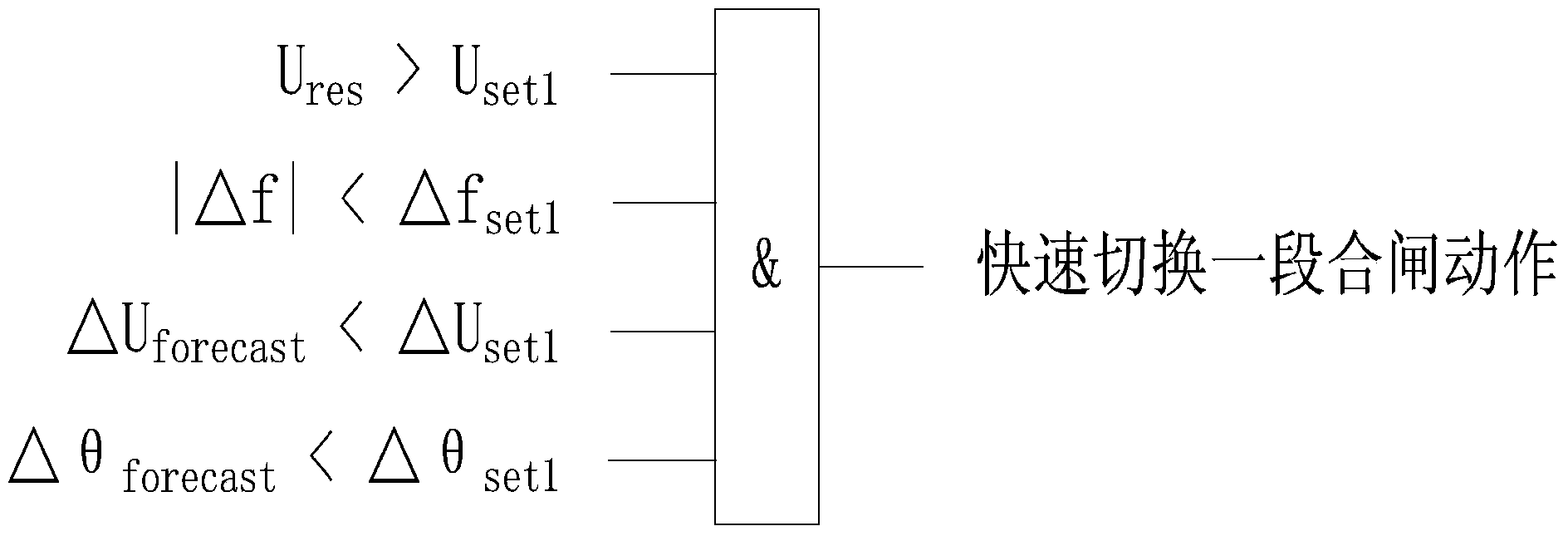

Power supply fast switch method and system

ActiveCN103730945AGood switching effectEmergency power supply arrangementsPhase differenceComputer module

The invention provides a power supply fast switch method and system. The power supply fast switch method comprises the following steps: step A, a switch starting signal transmitted from a switch starting judgment module is received; step B, whether fast switch conditions are met or not is judged, if yes, switch operation is performed, and if not, a step C is executed. The power supply fast switch method and system have the advantages that through mutual cooperation of all segments of a fast switch device and cooperation between a joint switch function and a fast switch function, the fast switch device can be adapted to various complex bus load conditions, and a better switch effect can be achieved; besides, when fast switch switching-on is judged, a current phase difference is replaced by a switching-on phase difference for judgment, as a result, the switching-on phase difference is accurately controlled to be within a permissible value range, the switch operation is faster and safer, and a device is protected against damage.

Owner:CEIEC ELECTRIC TECH

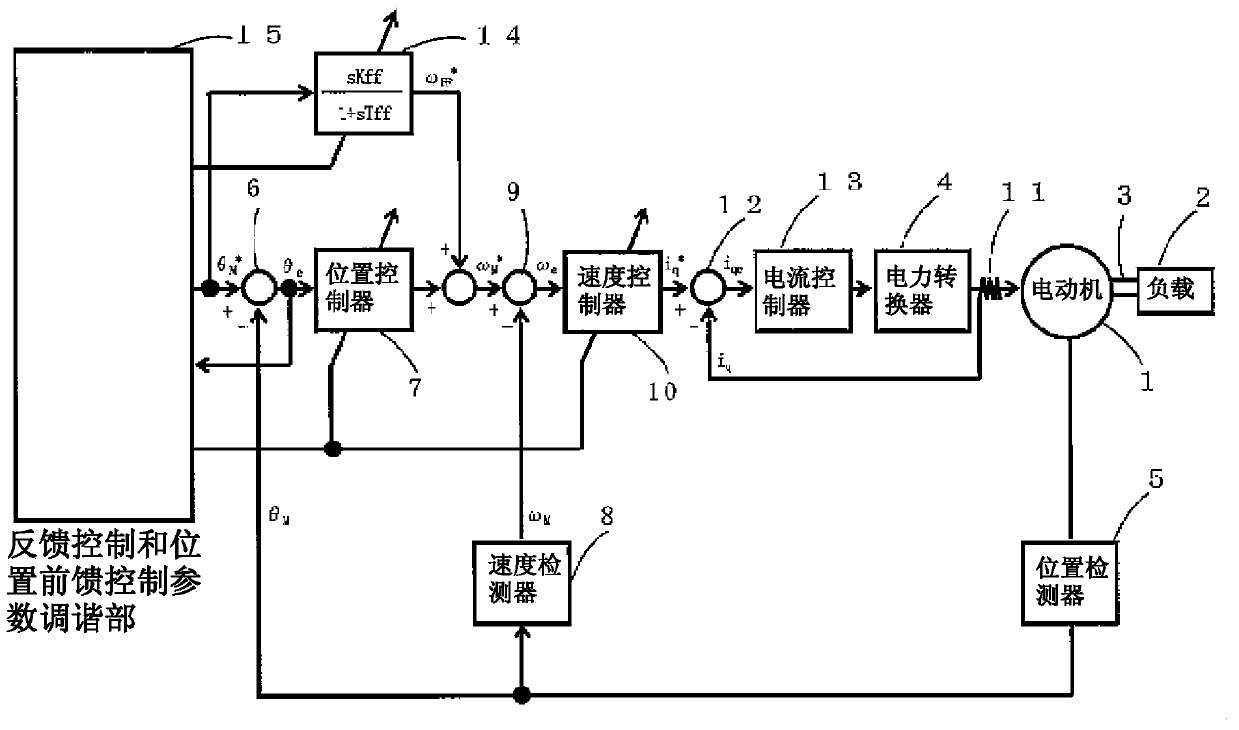

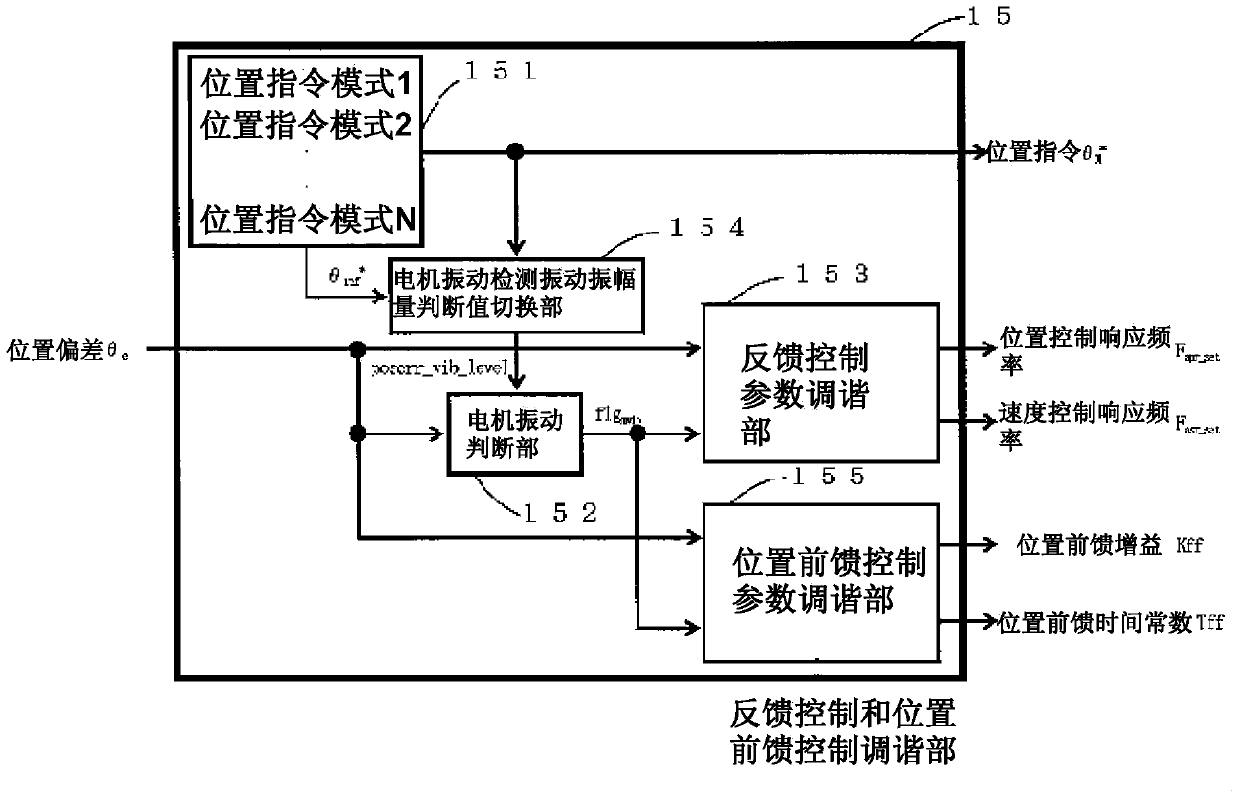

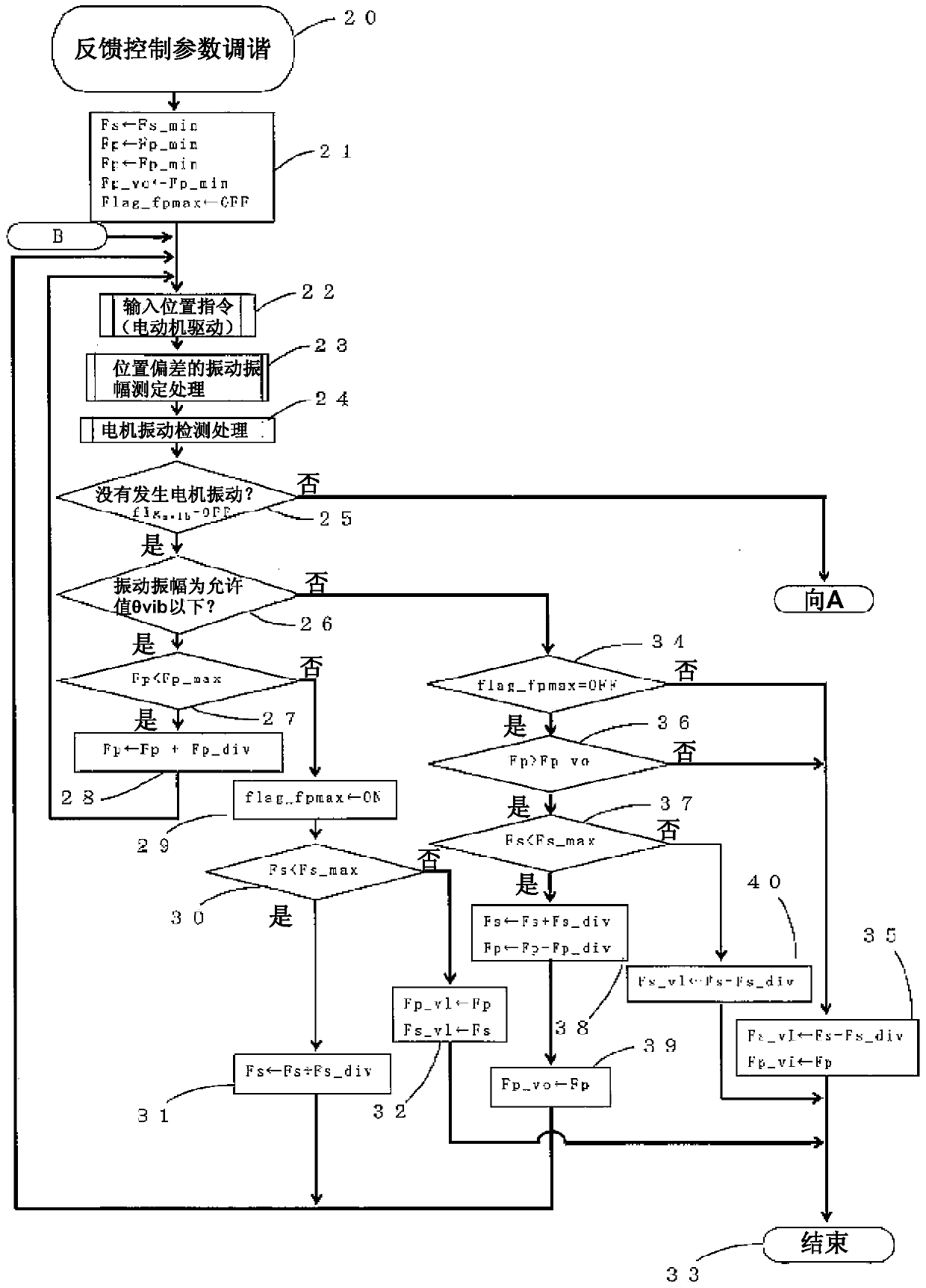

Electric motor control device and method for automatically adjusting same

ActiveCN104221278AReduce the burden onControl parameters are stableElectric motor controlControl using feedbackVibration amplitudeMotor vibration

The present invention provides an electric motor control device capable of reducing the burden on the operator and automatically adjusting control parameters to achieve stable operation, and a method for automatically adjusting the device. A control-parameter automatic adjustment device, wherein there are provided an adjustment method and a device for repeating automatic adjustment, within permissible value ranges for vibration amplitude and overshoot set by the user, until appropriate control parameters are obtained, while detecting motor vibration while the motor is stopped and motor vibration while the motor is operating and suppressing motor vibration.

Owner:HITACHI IND EQUIP SYST CO LTD