Carry-saving multiplier

A multiplier and carry-out technology, applied in the field of carry-save multipliers, can solve problems such as irregularity and high-quality layout design difficulties, and achieve the effects of regular structure, reduced multiplier area, and improved speed and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

[0056] The present invention will be described in detail below in combination with the design idea of the invention.

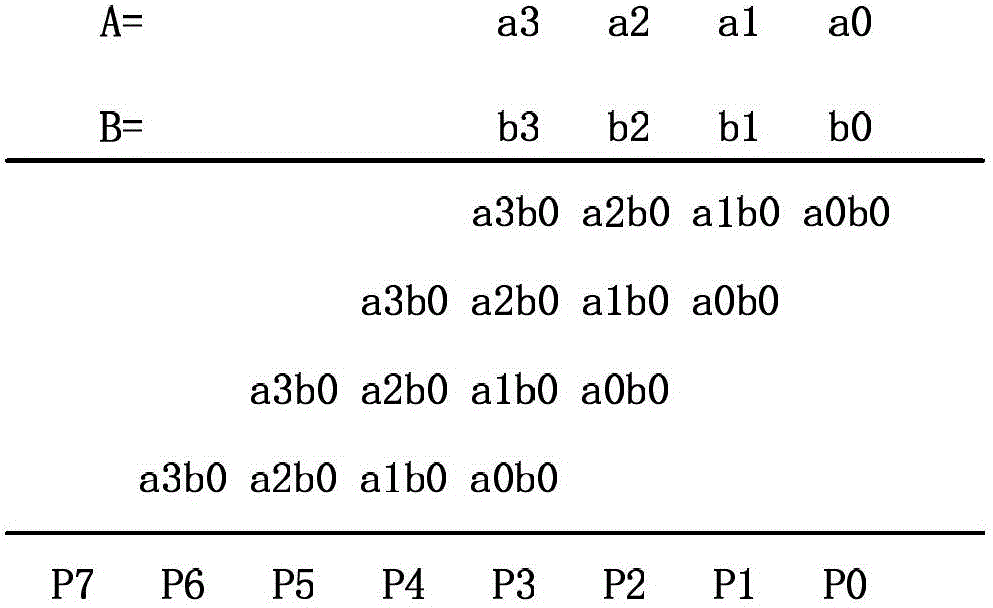

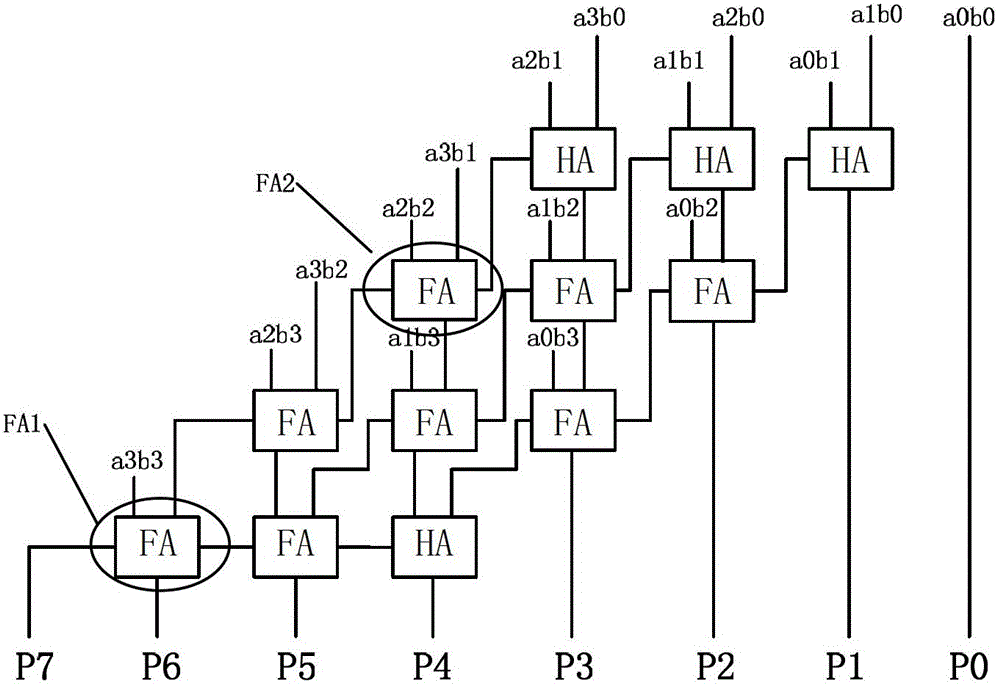

[0057] From figure 2 The traditional carry-save multiplier shown can be analyzed, and the input signals of each adder therein are not completely independent, and some signals may have common factors, and the simplification of the carry-save multiplier by the present invention starts from this point . Through analysis, it can be found that there are two full adders ( figure 2 marked as FA1 and FA2) are quite special. Its particularity lies in the certain correlation between their 3 input signals. The following is a simple analysis of the two respec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More