Implementation method of self-erasable FPGA (field programmable gate array) configuration module

A technology for configuration modules and implementation methods, applied in information storage, static memory, instruments, etc., can solve problems such as inability to protect, digital systems cannot be completed by themselves, FPGA and PROM cannot work, etc. The implementation method is simple and convenient, avoiding Erase operation by mistake and guarantee the effect of normal operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

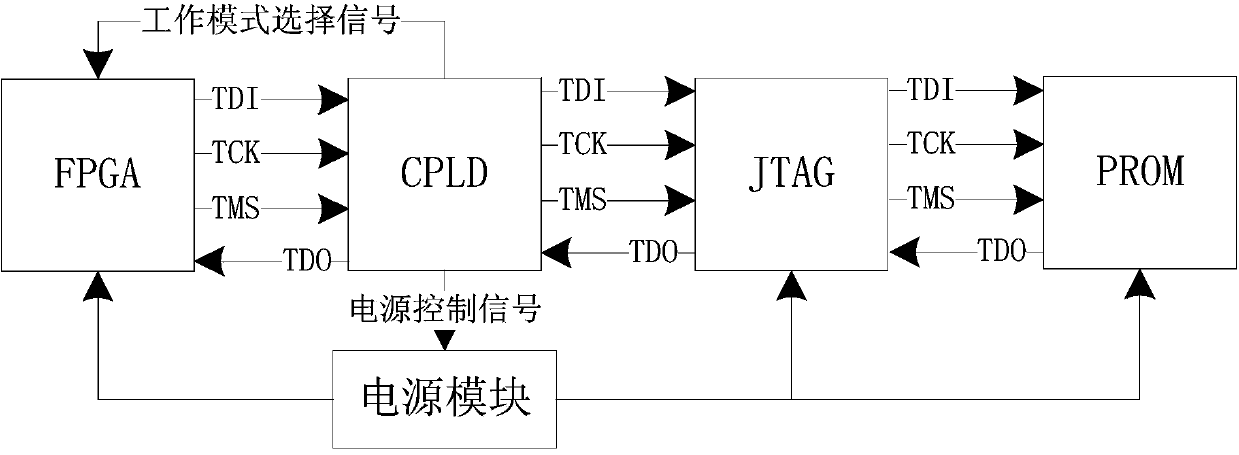

[0036] In order to meet the requirements of technical confidentiality, the digital system needs to erase the configuration information of the FPGA to avoid obtaining relevant technical information through the configuration information. For digital systems designed based on FPGA and PROM, due to the storage characteristics of FPGA, the configuration information on it will be lost after power off, so it is only necessary to erase the configuration information on the PROM. The access, programming and erasing of PROM can be realized through JTAG. The present invention designs a self-erasable FPGA configuration module, which simulates JTAG to issue erasing instructions to the PROM by generating relevant signals through the FPGA, thereby completing the self-erasing operation.

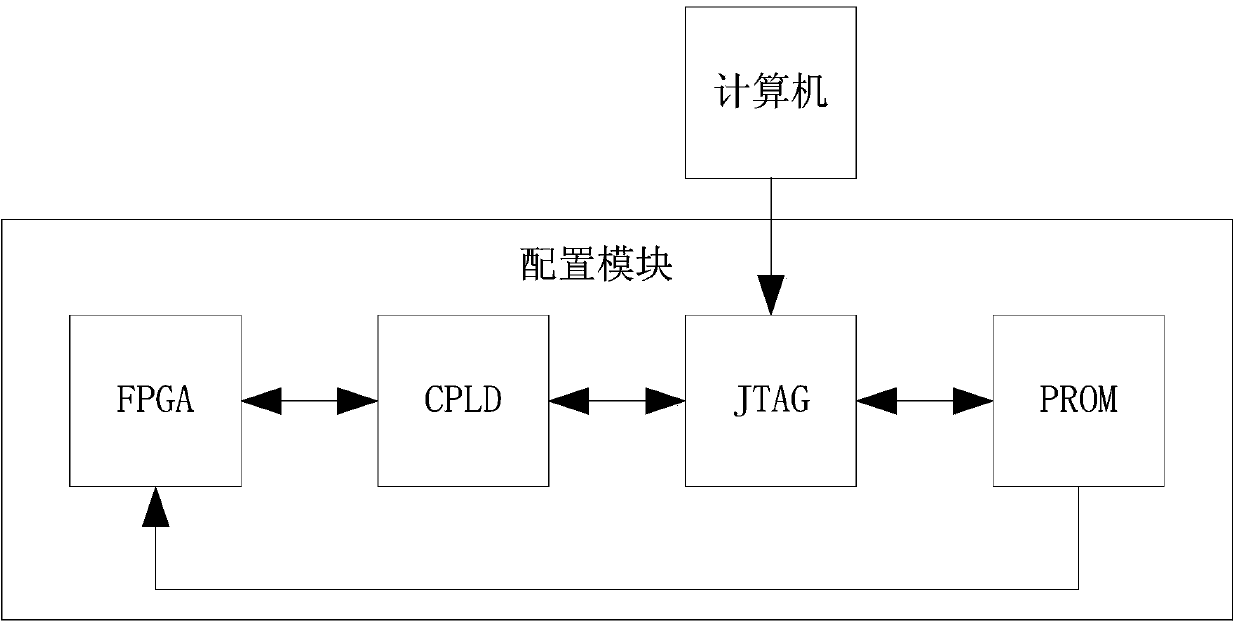

[0037] Such as figure 1 Shown is the schematic diagram of the FPGA confi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More