High-resolution clock phase-shift architecture and algorithm implementation method

A high-resolution, clock-phase technology, applied in the direction of automatic power control, electrical components, etc., can solve problems such as low phase shift resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The embodiments listed in the present invention are only used to help understand the present invention, and should not be interpreted as limiting the protection scope of the present invention. For those of ordinary skill in the art, they can also Improvements and modifications are made to the present invention, and these improvements and modifications also fall within the protection scope of the claims of the present invention.

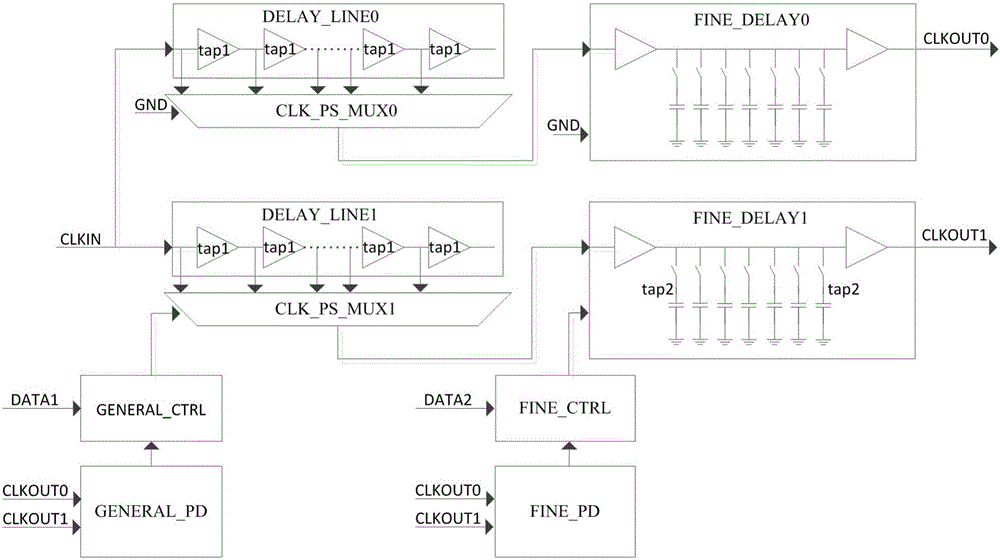

[0037] Such as figure 1As shown, CLKIN is the input clock. In order to make the reference phase-shifted clock highly match the target phase-shifted clock and offset the inherent phase delay, CLKIN enters DELAY_LINE0 and DELAY_LINE1 at the same time. CLKIN generates CLKOUT0 through DELAY_LINE0, CLK_PS_MUX0 and FINE_DELAY0, where CLK_PS_MUX0 is configured as a fixed 0, and FINE_DELAY0 is also configured as 0, that is, CLKOUT0 is the reference phase shift clock. CLKIN generates CLKOUT1 through DELAY_LINE1, CLK_PS_MUX1 and FINE_DELAY1, and CLKOUT1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More