Dynamic self-adaptive bus arbiter based on microprocessor-on-chip

An on-chip multi-processor and dynamic self-adaptive technology, applied in electrical digital data processing, instruments, etc., can solve problems such as unpredictability and complex priority setting, achieve good bus bandwidth, reduce bus waiting time, and improve system performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

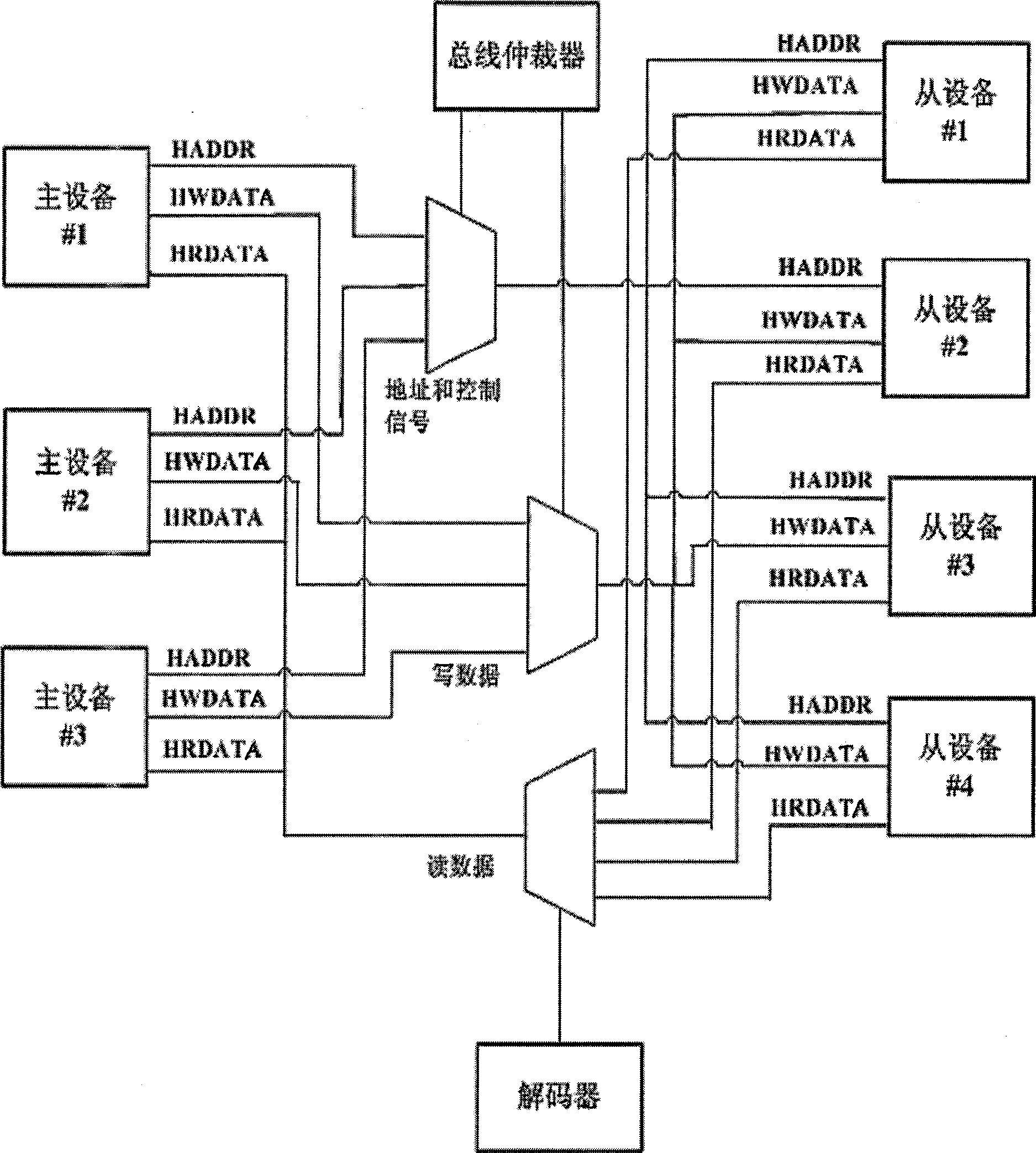

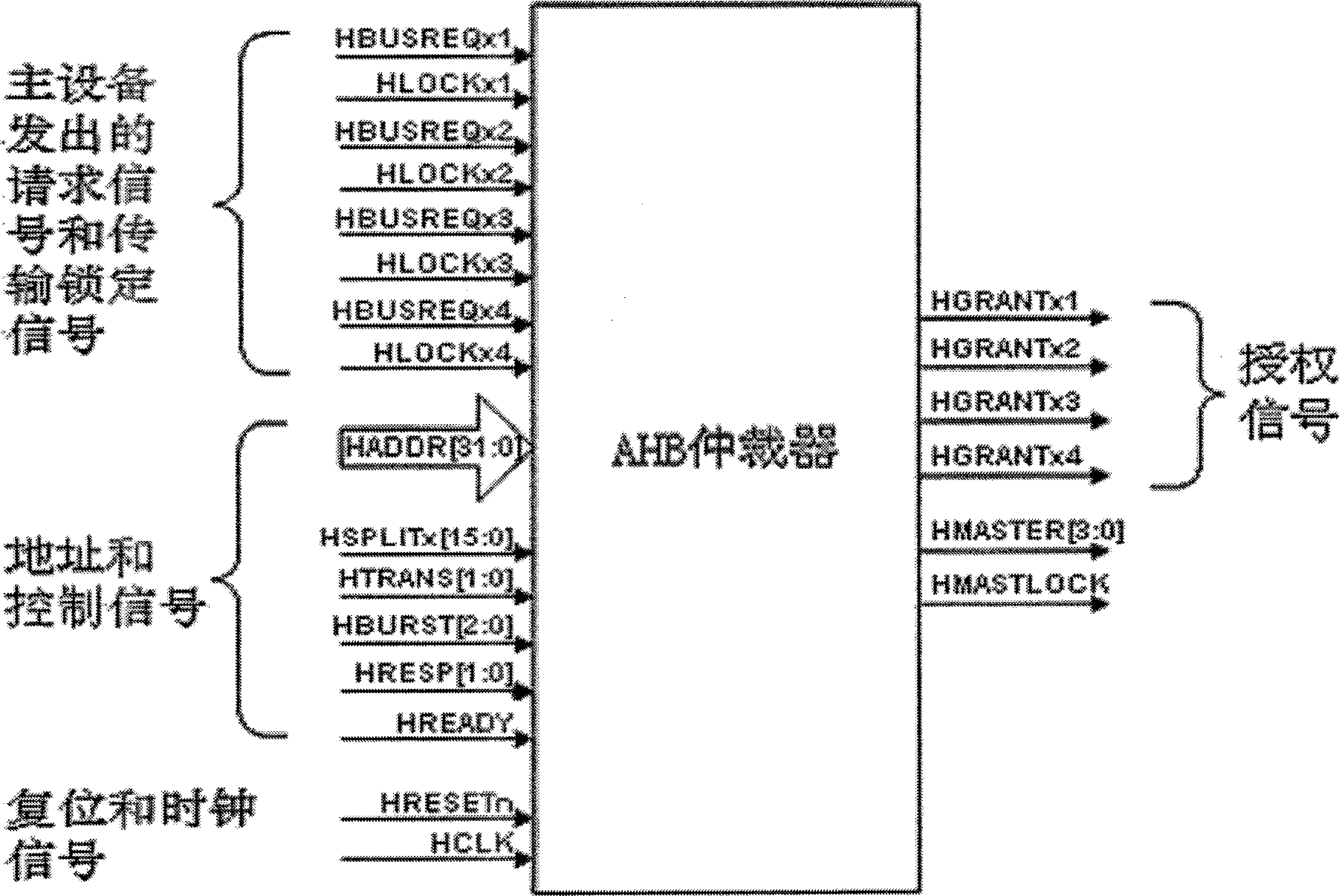

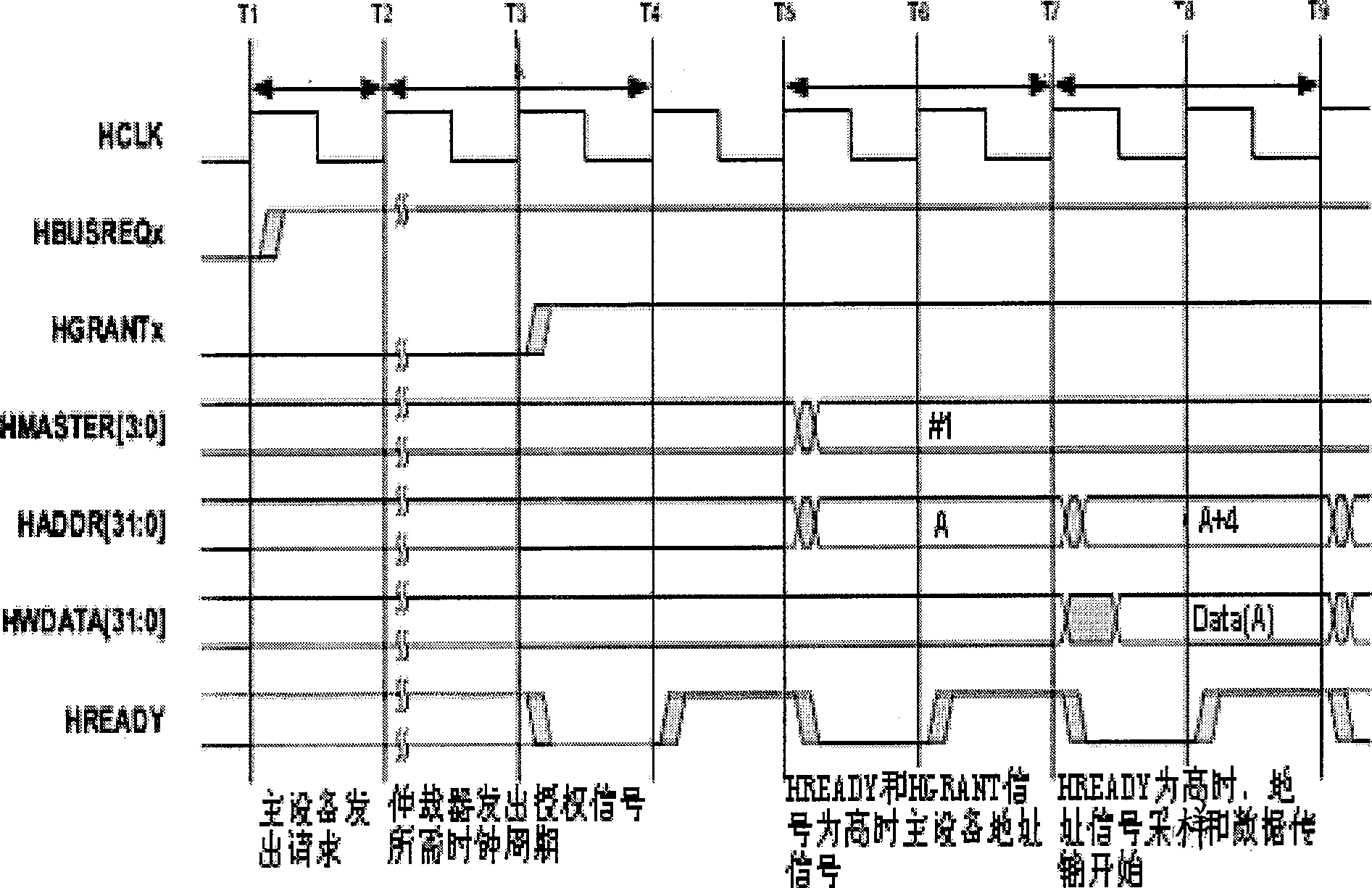

[0027] A kind of dynamic adaptive bus arbiter based on on-chip multiprocessor system according to the present invention on the shared AMBA-AHB bus of four processors, see appendix Figure 7 The modules included are: interface control module 1 conforming to the AMBA-AHB bus standard, random number generation module 2, dynamic "lottery" number generation module 3, timer module 4 and Lottery bus arbitration module 5; interface control module 1 is responsible for and For communication on the bus, the timer module 4 sends an interrupt request to the dynamic "lottery ticket" number generation module 3 according to the current processor waiting for the bus situation, thereby determining the number of "lottery tickets" of each main device at present, and the random number generation module 2 generates the number that meets the range requirements. Random number, the Lottery bus arbitration module 5 generates the ID number of the processor that obtains the right to use the bus according ...

Embodiment 2

[0034]A hierarchical bus system including a shared system bus and four processors as master devices, the system includes: four first-level buses independently occupied by each processor for access to its private memory; bus bridge , which is used for the connection between the first-level bus and the second-level bus, and controls the processor's access to different buses; the shared memory can be accessed by four processors, and is used for synchronization and data exchange between different processors; and the second The second-layer bus is the bus shared by each processor, including: a dynamic adaptive bus arbitrator, the number of "lottery tickets" held by each processor represents the ratio of the bus bandwidth occupied by each processor, and a weighted random algorithm is used to control the processor's performance on the system. The use priority of the bus, in response to the activation of the interrupt signal of the internal timer of the arbitrator, continuously increas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More