Method for reliable inter-core communication between hierarchical multi-core processors

A technology of a multi-core processor and a communication method, which is applied in the field of reliable communication between hierarchical multi-core processor cores, can solve the problems of complex hardware architecture, cannot be well adapted to various hardware occasions, and is difficult to program design, and achieves reliable core performance. the effect of intercommunication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

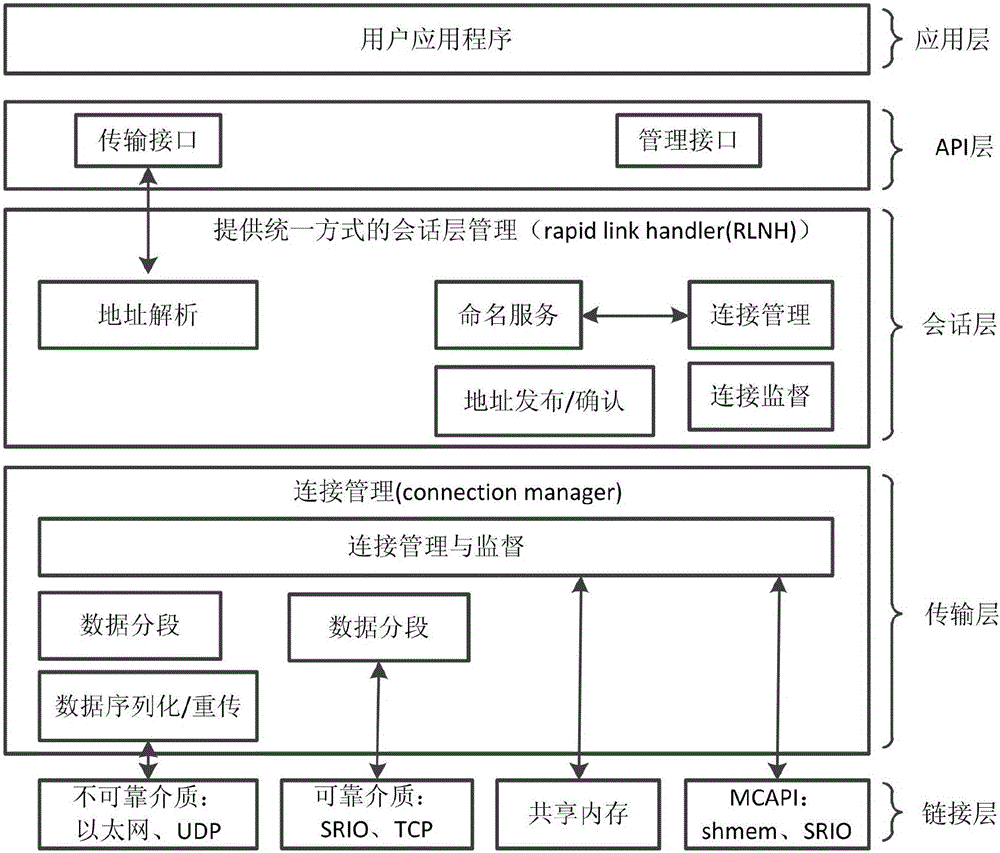

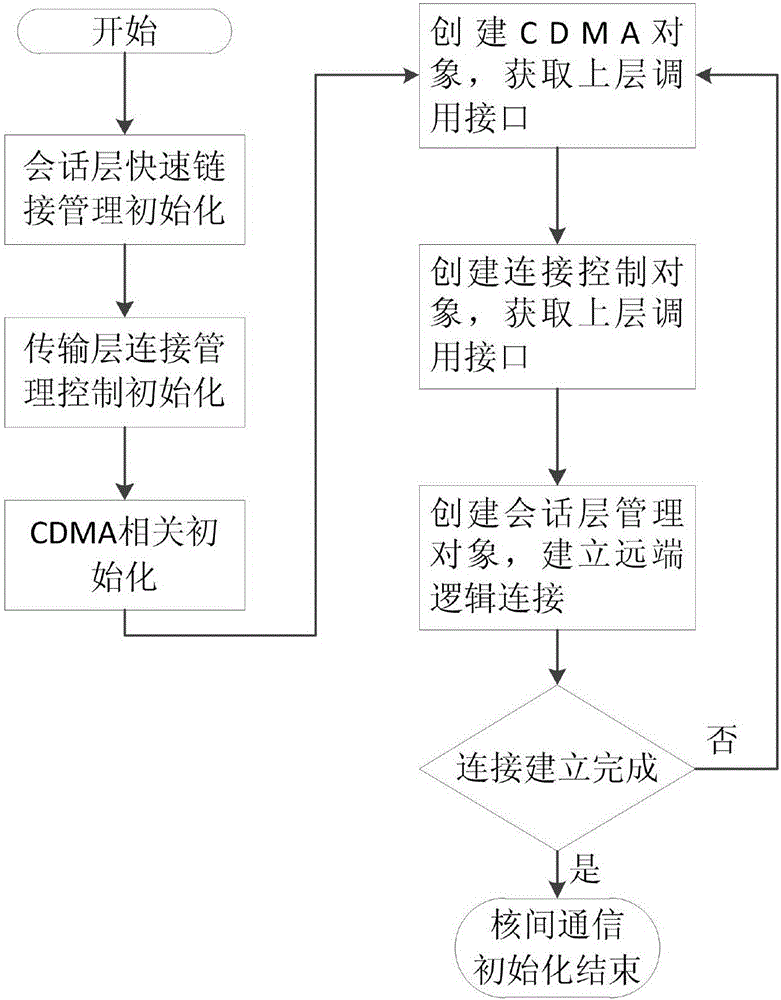

[0039] Such as figure 1 As shown, the present invention provides a method for reliable communication between layered multi-core processor cores, comprising the following steps:

[0040] Step 1: Divide the multi-core communication system into five levels from bottom to top:

[0041] (1) Link layer

[0042] The link layer provides a variety of physical link methods for the upper transport layer. It can choose unreliable media, such as Ethernet and UDP, and reliable media, such as SRIO and TCP. At the same time, there are shared memory, MCAPI and other methods to choose from, which are suitable for the application environment of various multi-core processors. The design of the link layer makes the technology of the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More