Novel CSD constant multiplier algorithm structure for 256-point FFT processor

A technology of algorithm structure and multiplier, which is applied in complex mathematical operations, electrical digital data processing, special data processing applications, etc., can solve the problems of low hardware cost and complex structure of CSD constant multiplier, and achieve good power consumption and save calculation Time, reduce the effect of hardware investment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

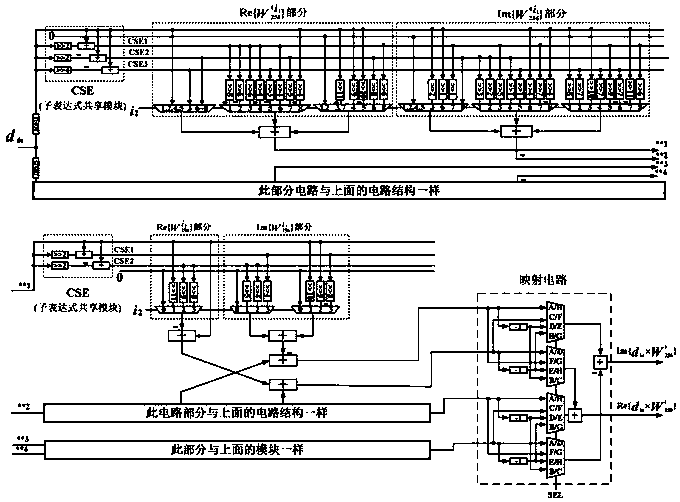

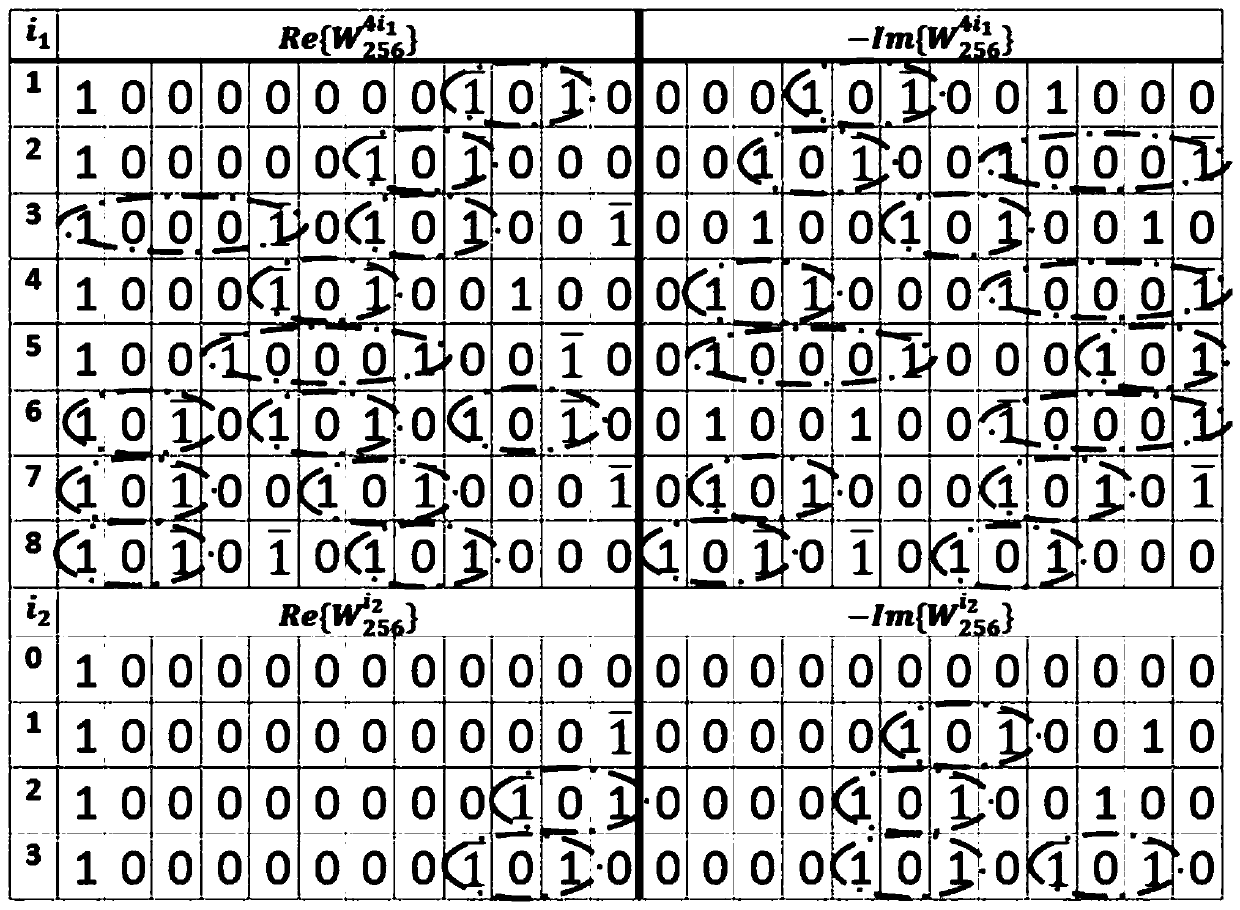

[0020] The present invention provides a novel cascaded CSD constant multiplier algorithm structure for a 256-point FFT processor, the algorithm structure comprising the following steps:

[0021] Step 1, using symmetry to change the number of twiddle factor constant values from 256 to the original 1 / 8 or 36, and the twiddle factor is represented by the following formula:

[0022]

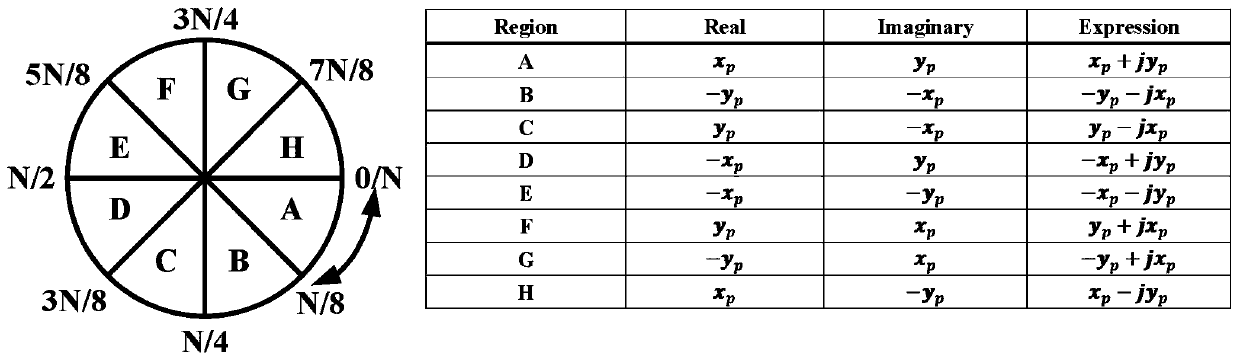

[0023] like image 3 As shown, the symmetric map is equally divided into A-H8 areas, and N in the figure is the number of FFT points, where the real part of the A area is expressed as x p , the imaginary part is denoted as y p , the constant denoted as x p +jy p ; The real part of the B area is expressed as -y p , the imaginary part is expressed as -x p , the constant is expressed as -y p -jx p ; The real part of the region C is denoted as y p , the imaginary part is expressed as -x p , the constant denoted as y p -jx p ; The real part of the D area is expressed as -x p , the imagina...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More