Frequency search and error correction method in clock data recovery circuit

A technology of clock data recovery and frequency search, which is applied in the field of frequency search and error correction, can solve problems such as inability to sample data correctly, operations that cannot implement phase alignment, fractional harmonic false locking, etc., so as to avoid frequency false locking and shorten Frequency lock time, increase the effect of anti-interference ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some structures related to the present invention are shown in the drawings but not all structures.

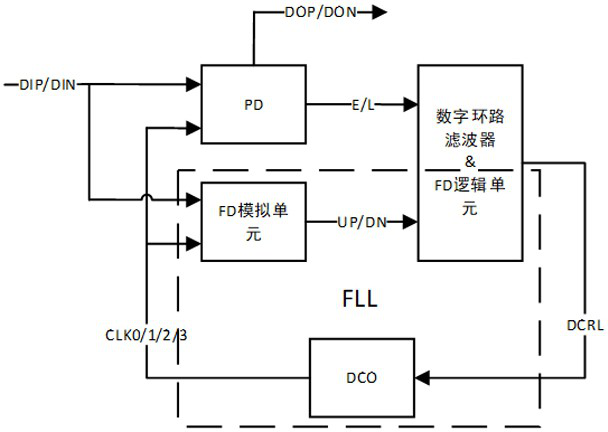

[0030] figure 1 A structural diagram of a clock data recovery circuit according to the present invention is shown. The clock data recovery circuit (CDR) is used to recover the clock in the random signal DIP / DIN with noise, and at the same time use the recovered clock to sample the input random information DIP / DIN to obtain a high-quality recovered signal. In order to recover the clock, it is necessary to use a frequency locked loop (FLL) to get an accurate clock frequency.

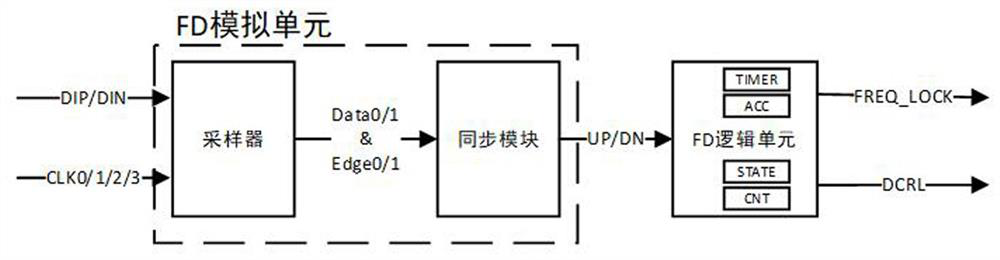

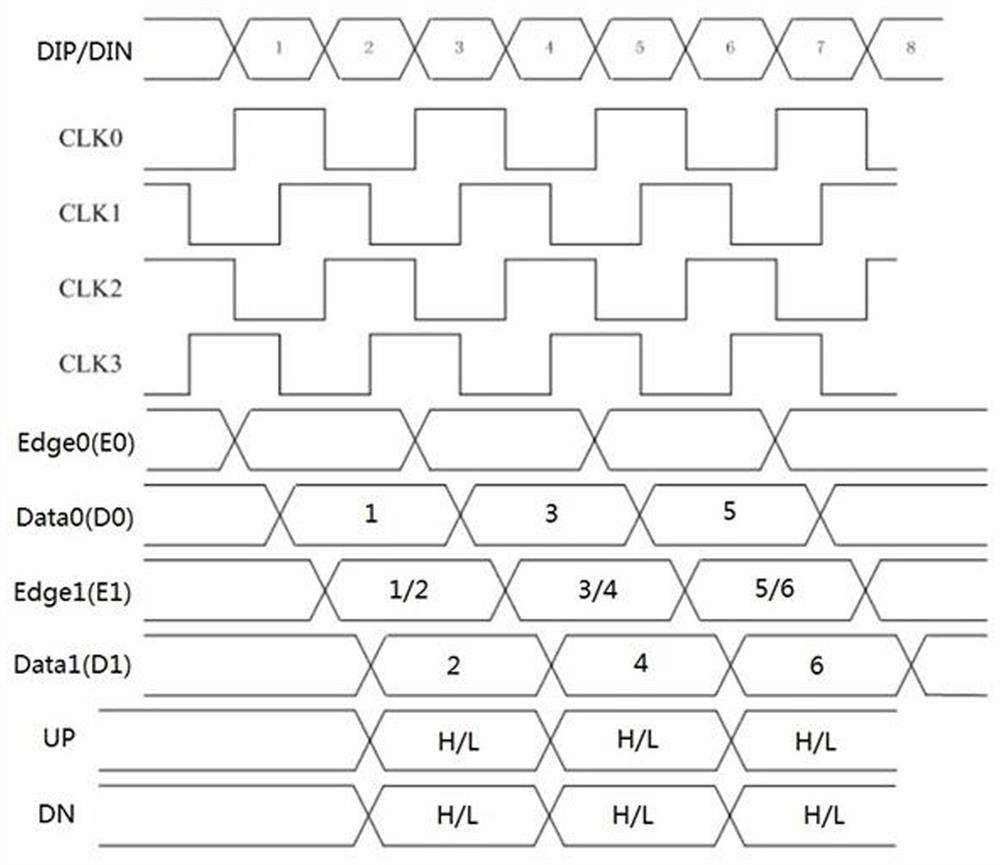

[0031] Generally speaking, the input ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More