Multiplying device, data processing method, chip and electronic equipment

A multiplier and data technology, applied in the computer field, can solve the problem of high complexity of multiplication operations, and achieve the effects of reducing complexity, reducing area, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

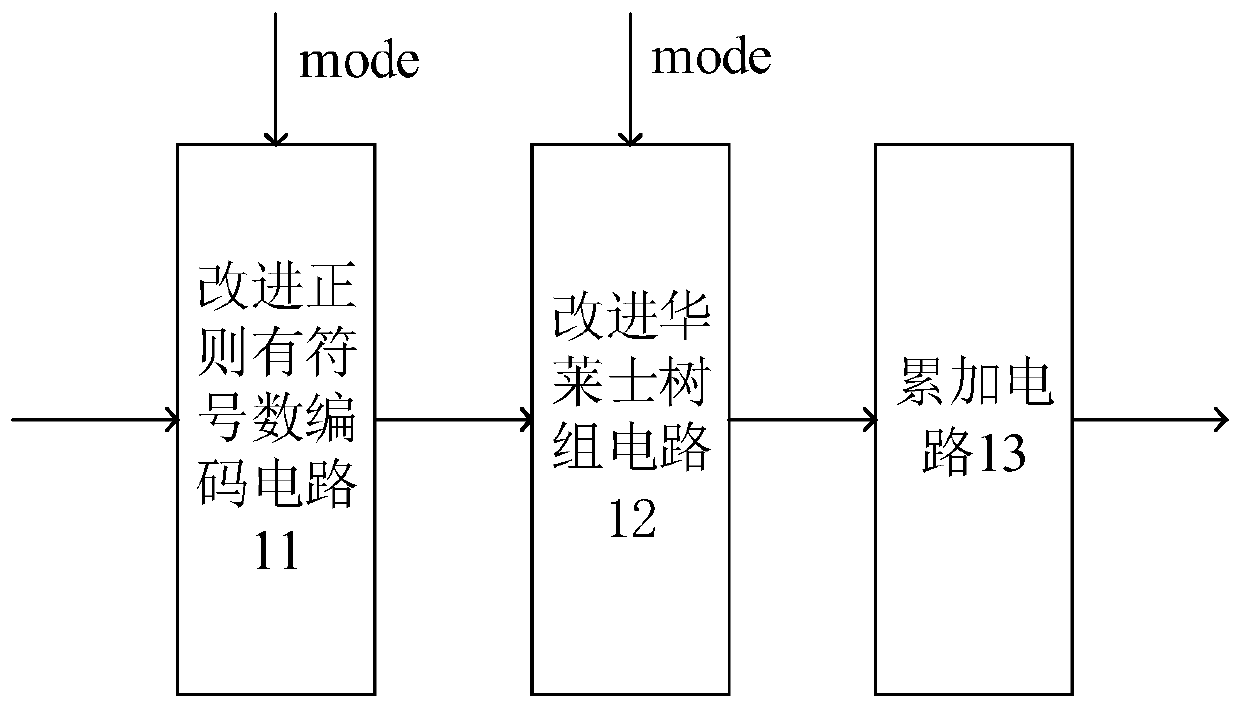

[0071] The multiplier provided by this application can be applied to AI chips, field programmable gate array FPGA (Field-Programmable Gate Array, FPGA) chips, or other hardware circuit devices for multiplication processing. The specific structural diagram is as follows figure 1 shown.

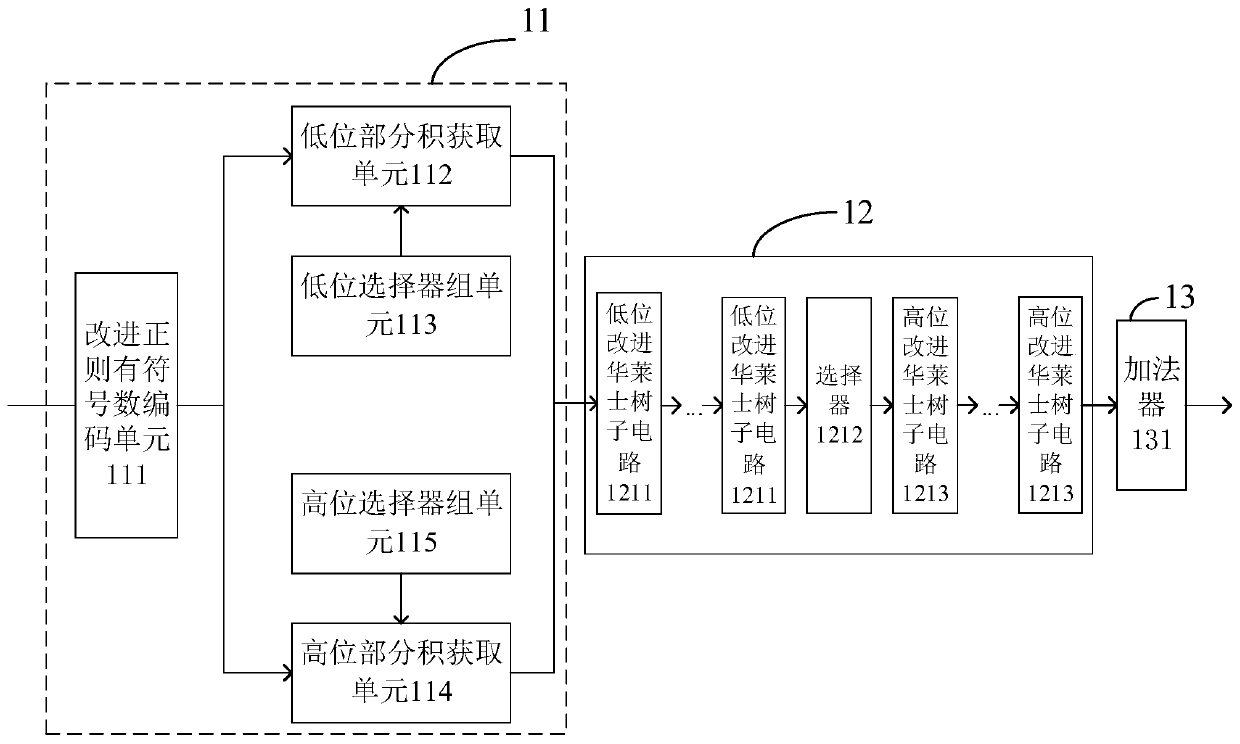

[0072] Such as figure 1 Shown is a structural diagram of a multiplier provided by an embodiment. Such as figure 1 As shown, the multiplier includes: an improved regular signed number encoding circuit 11, an improved Wallace tree group circuit 12 and an accumulation circuit 13; the improv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More