Multi-input shift summation accumulator based on Wallace tree

A wallace tree and multi-input technology, which is applied in the direction of instruments, machine execution devices, and calculations using numerical representation, can solve the problems of non-negligible circuit delay, large circuit area, difficult control of circuit clock and pipeline design, etc., to achieve Save carry chain overhead, improve clock frequency and accumulation efficiency, and save hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

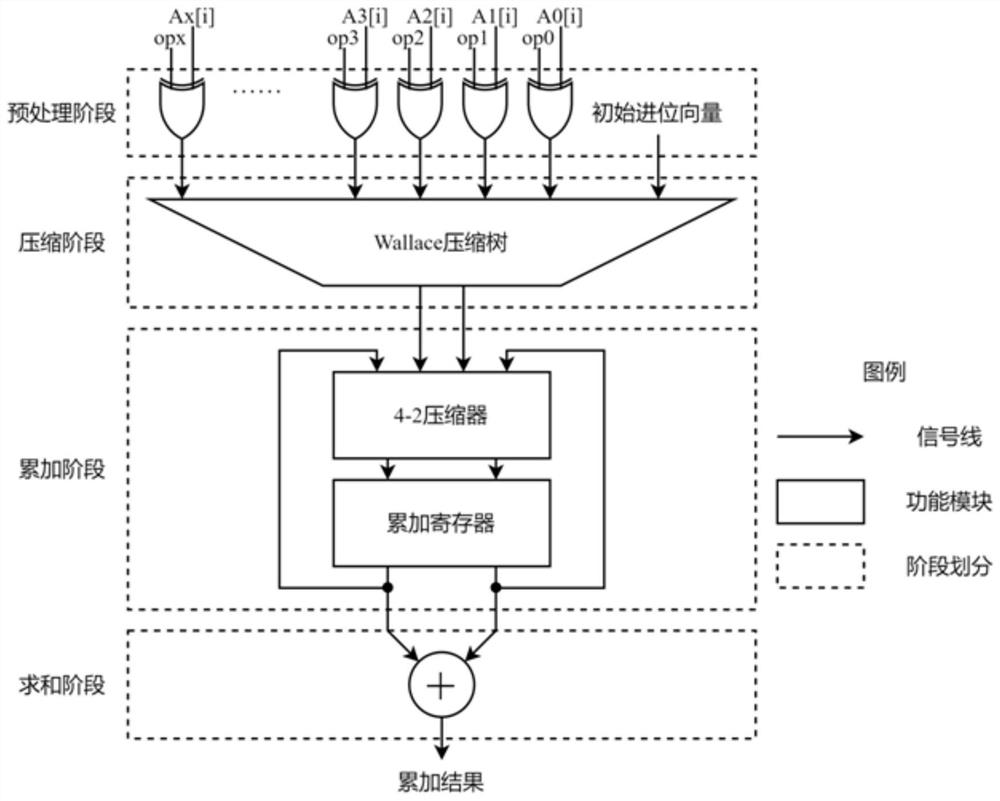

[0017] The present embodiment provides a kind of multi-input shift sum accumulator based on Wallace tree which is convenient for design pipeline, supports original code format and subtraction, such as figure 2 As shown, it specifically includes: XOR gate array, initial carry vector generation module, Wallace compression tree, 4-2 compressor, accumulation register and adder; wherein,

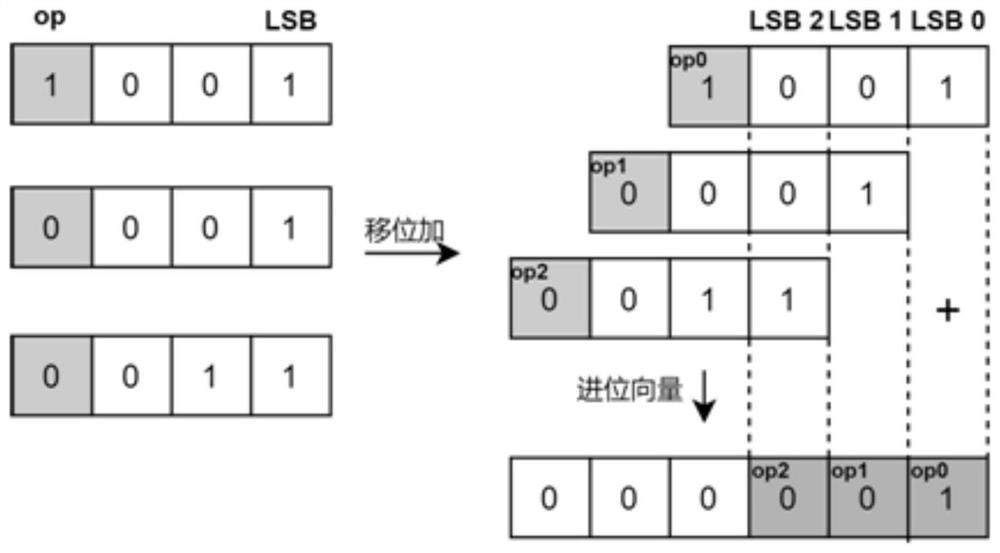

[0018] The shift summation accumulator includes x+1 input data, which are: A0[i], A1[i],...,Ax[i]; the input data is input to the XOR gate array, and for each input data , the XOR gate array performs a logical XOR operation on each bit of the input data and its corresponding operator (0 for addition, 1 for subtraction), and outputs it to the Wallace compression tree; Inverse code of the input data, and reserve the input data that needs to be mathematically adde...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More