A testing method for a second-order booth coded wallace tree multiplier circuit

A test method and multiplier technology, which is applied in the test of multiplier circuit and the test field of Wallace tree multiplier circuit, can solve the problems of Wallace tree multiplier bit width, difficult traversal method test, large test vector set, etc., to achieve Reduced test time, reduced test vector set size, effect of reduced size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

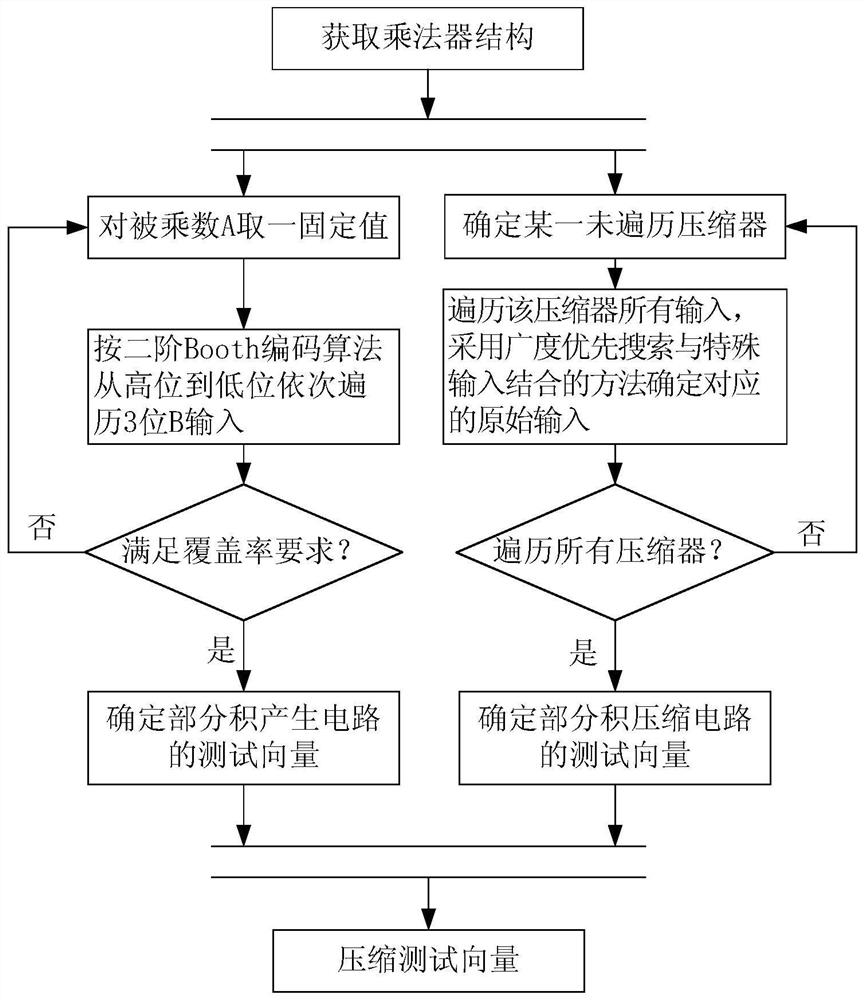

Method used

Image

Examples

Embodiment approach

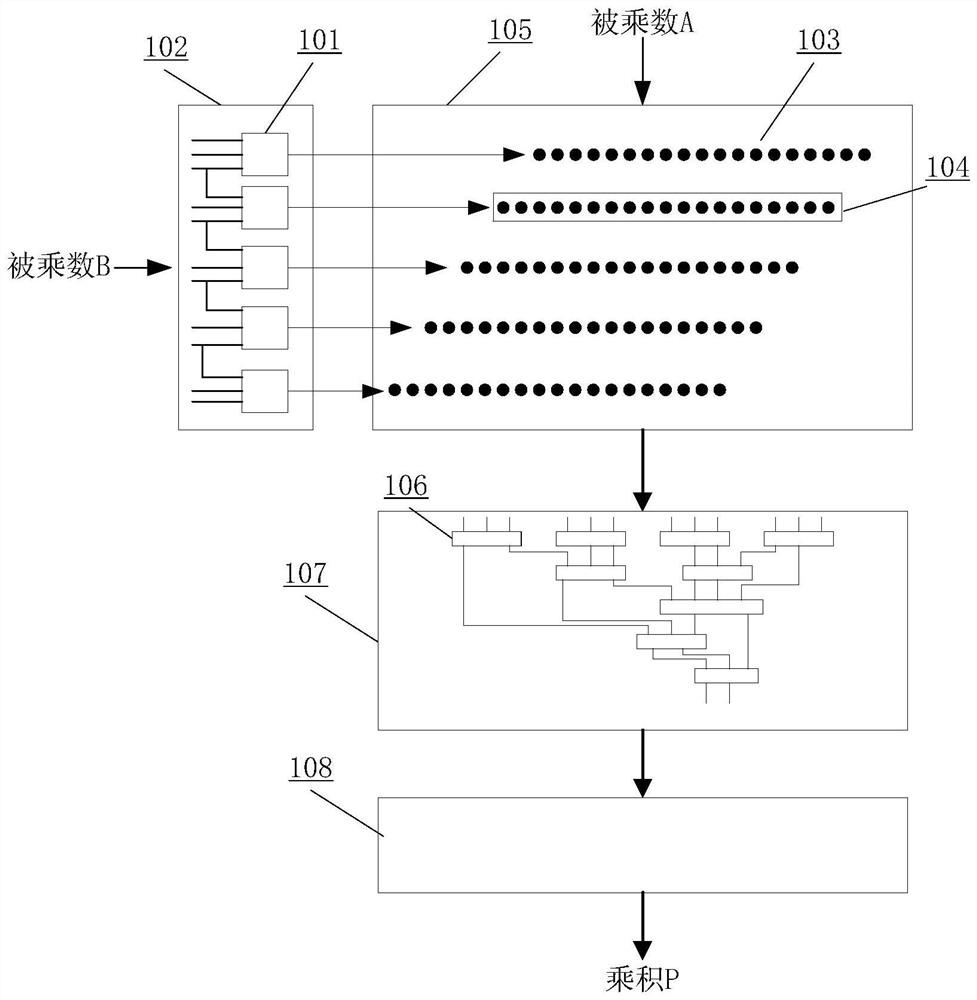

[0133] Take the complement multiplier of the Wallace tree structure of the second-order Booth code of a kind of 25 * 18 bit width as example, for this multiplier, the specific implementation mode of the present invention is as follows:

[0134] Get Multiplier Structure: Get the gate-level schematic diagram of the multiplier.

[0135] Analysis and processing multiplier structure: The multiplier contains 9 Booth coding units, among which 8 high-order Booth coding units are the same, and the input is the adjacent 3-bit multiplier B; there is another 1 low-order Booth coding unit, and the input is the lowest 2 bits Multiplier B. The multiplier includes 9 partial products, each of which contains 26 bits, corresponding to 25 bits of multiplicand A and 1 sign bit. The output of the partial product is jointly controlled by the A input and the Booth encoding unit. The above-mentioned circuit component product produces a circuit part. The multiplier includes 2:1 compressor, 3:2 compr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More