An Improved Analog Circuit Signal Noise Reduction Method

An analog circuit and signal technology, applied in the field of improved analog circuit signal noise reduction, can solve problems such as poor, effective engineering practice effects of simulated signals, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

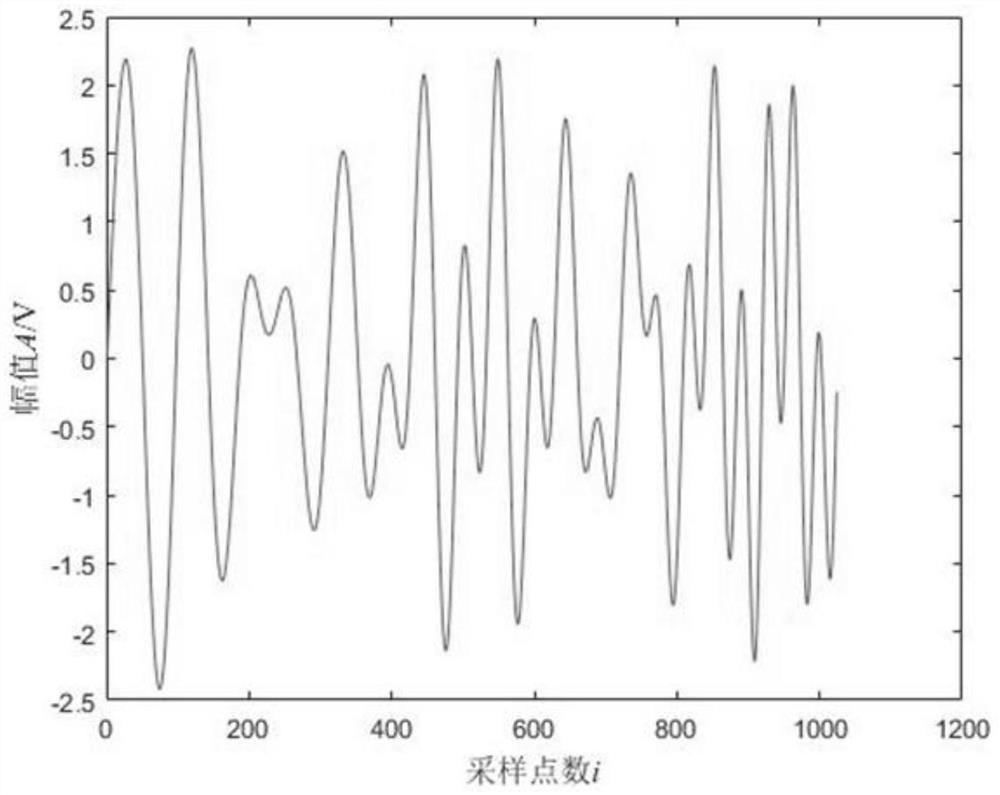

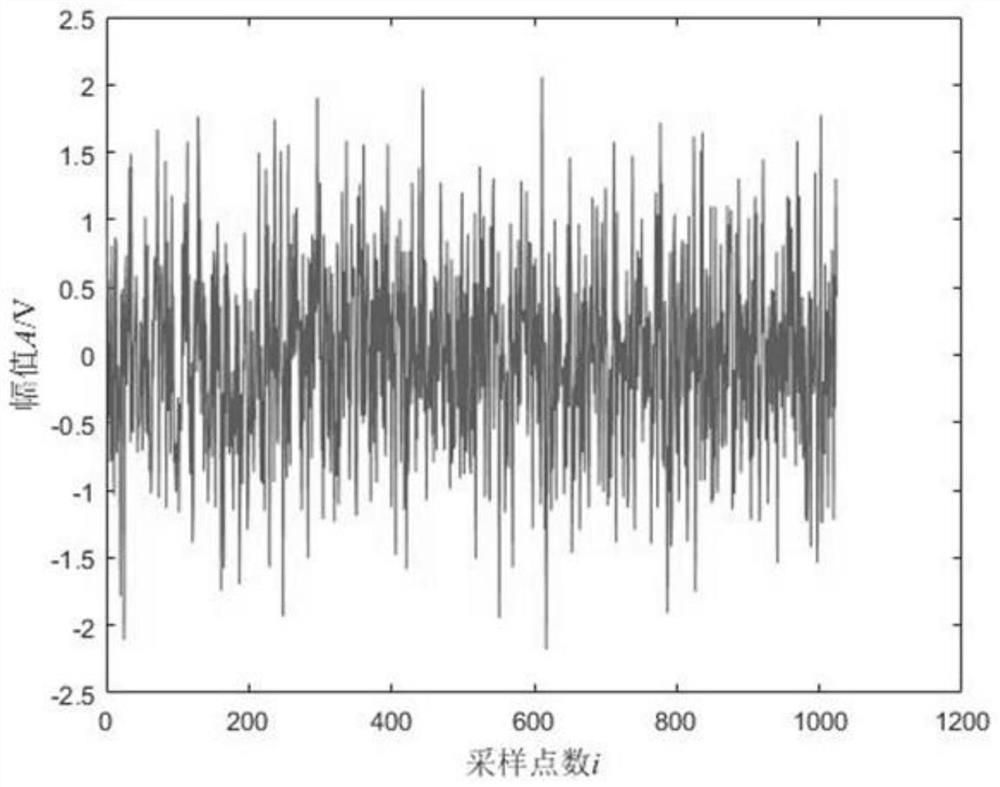

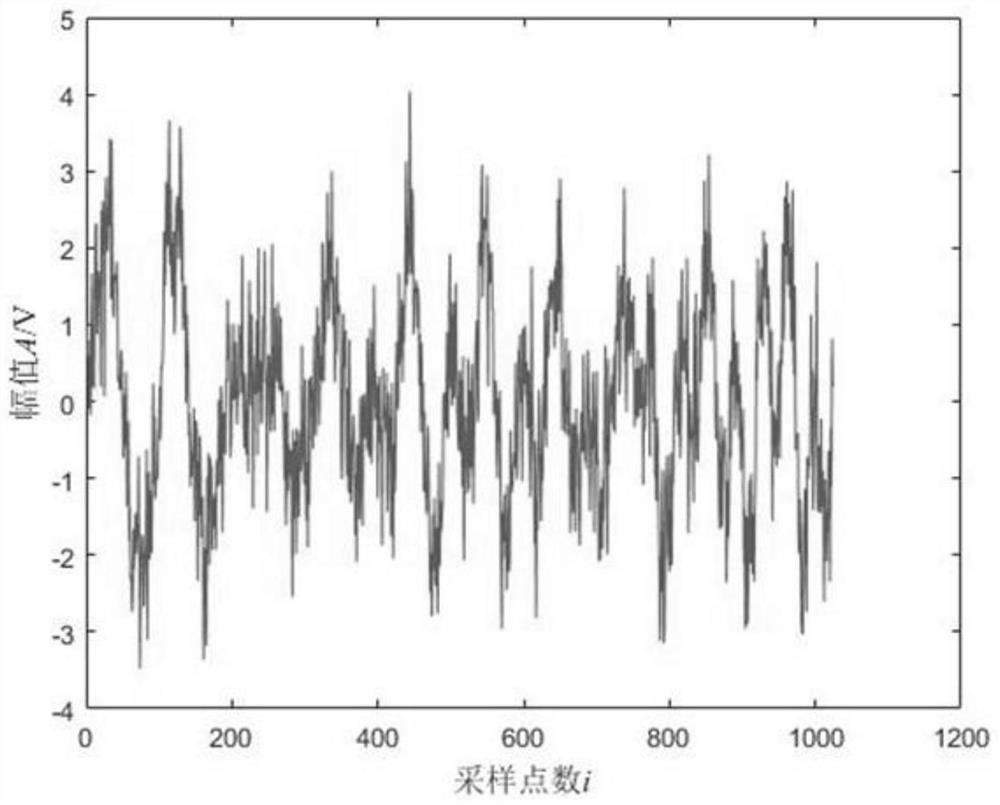

[0082] In order to verify the effectiveness of the method in the present invention, the FM-AM signal mixed with noise as shown in the following formula is considered: In the formula, the original signal x(t) is given by the appendix figure 1 Pure signal x shown 0 (t) and appendix figure 2 The SNR shown is a 3dB white Gaussian noise n(t) synthesis, and the signal waveform is shown in the appendix image 3 As shown, the sampling frequency is 1024 Hz and the simulation time is t ∈ [0, 1].

[0083] In order to intuitively judge the quality of noise reduction, the introduction correlation index C is used as a reference, and the correlation index The closer C is to 1, the closer the signal after noise reduction is to the pure signal, that is, the better the noise reduction effect.

[0084] The results of noise reduction processing using the method in the present invention are as follows Figure 4 As shown, the variation curve of the filtered signal dimension with the singula...

Embodiment 2

[0095] The first embodiment is based on the ideal conditions where the model is known and the parameters are adjustable. In practical applications, the measured signal is often unknown. In order to illustrate the application effect of the algorithm in the present invention to the actual signal, the actual signal is verified.

[0096] attached Figure 11 is the noise reduction result of a sine wave signal with a signal-to-noise ratio of 0dB. Figure 12-14 It is the noise reduction result of several unknown signals randomly extracted in a missile circuit. It can be seen that the variation trend of the filtered signal dimension in the actual measurement process is completely consistent with the simulation experiment, and the noise reduction effect is better.

Embodiment 3

[0098] This embodiment verifies the suppression effect of the method in the present invention on the modal aliasing phenomenon.

[0099] Consider the LCD decomposition of the following signal:

[0100] x(t)=cos(60πt+sin(100πt))+n(t); wherein, the signal-to-noise ratio of Gaussian white noise n(t) is 3. The LCD decomposition of x(t) is directly carried out to obtain the following Figure 15 The decomposition results shown; use the algorithm in the present invention to perform SVD on it and then LCD, and the decomposition results are shown in the attached Figure 16 shown.

[0101] Contrast attached Figure 15 and attached Figure 16 It can be seen that when the noisy signal is directly LCD, each component of the original signal is separated into more ISC components; after the improved SVD noise reduction in the present invention, the number of components is reduced, and the decomposition quality is significantly improved. Mode aliasing is significantly reduced.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More