Structure, method and system for measuring RIE lag depth

a technology of reactive ions and lag depth, applied in the direction of individual semiconductor device testing, semiconductor/solid-state device testing/measurement, instruments, etc., can solve the problems of reducing the etching rate, affecting the control of deep trench side wall passivation, and affecting the etching ra

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

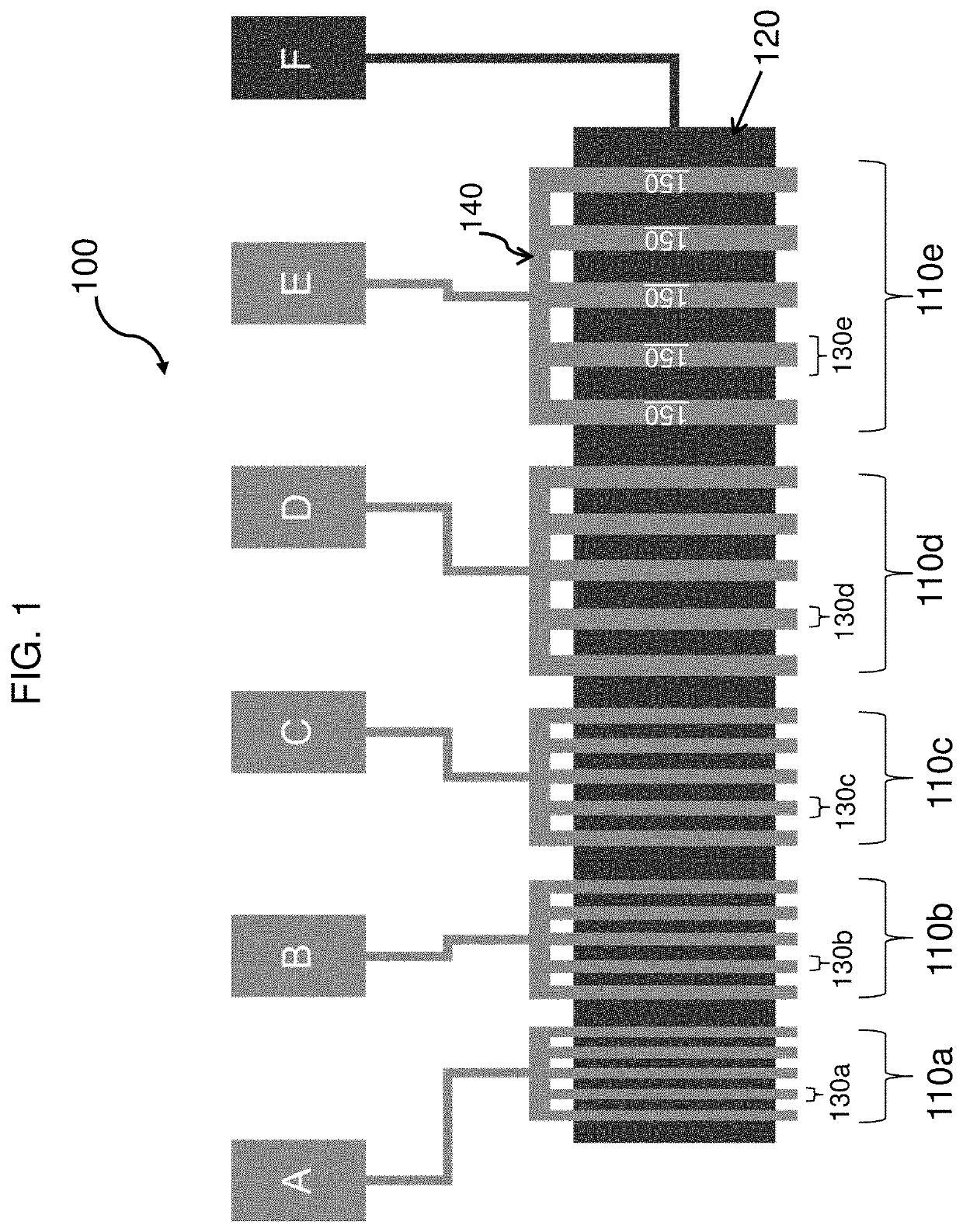

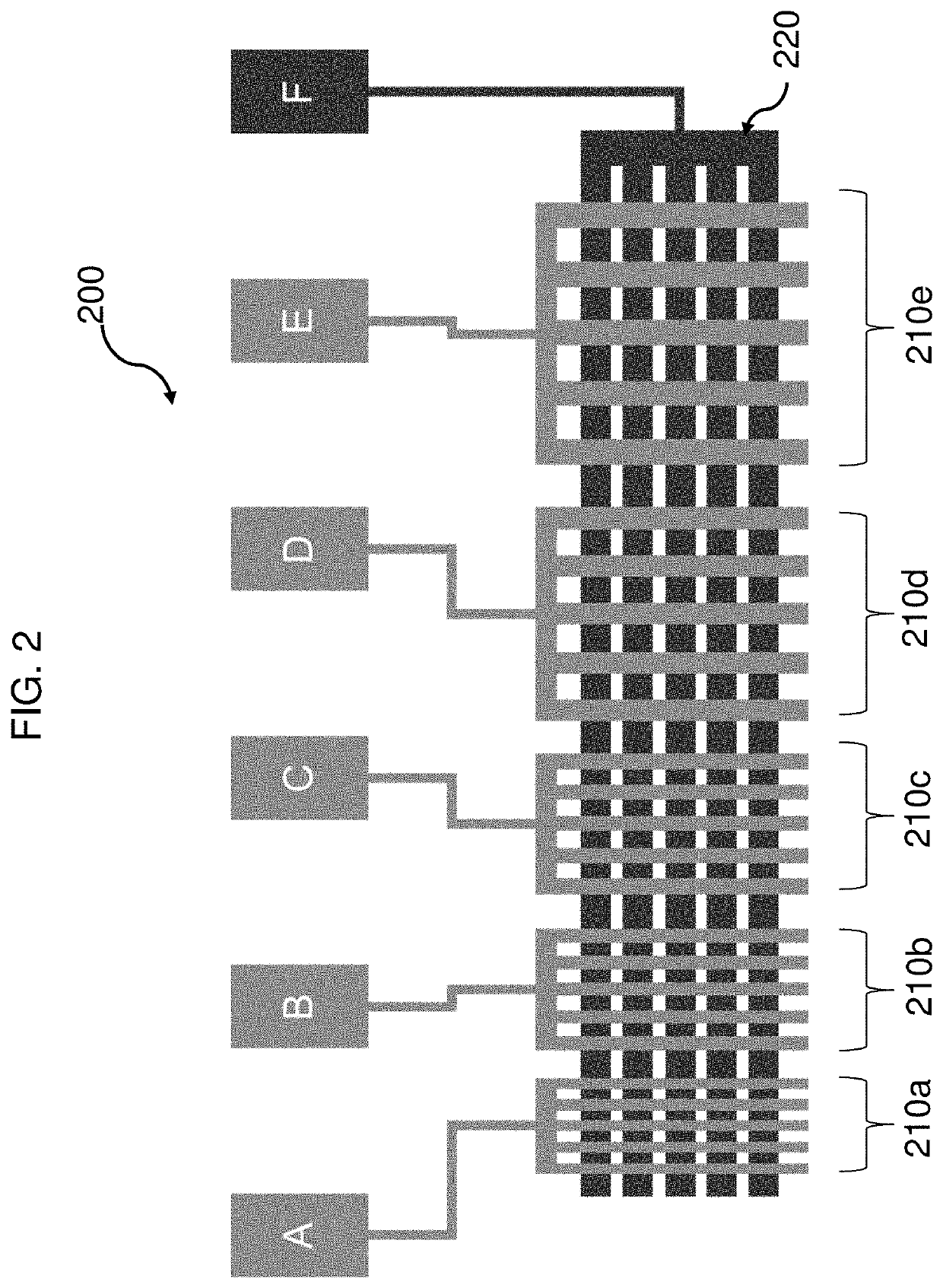

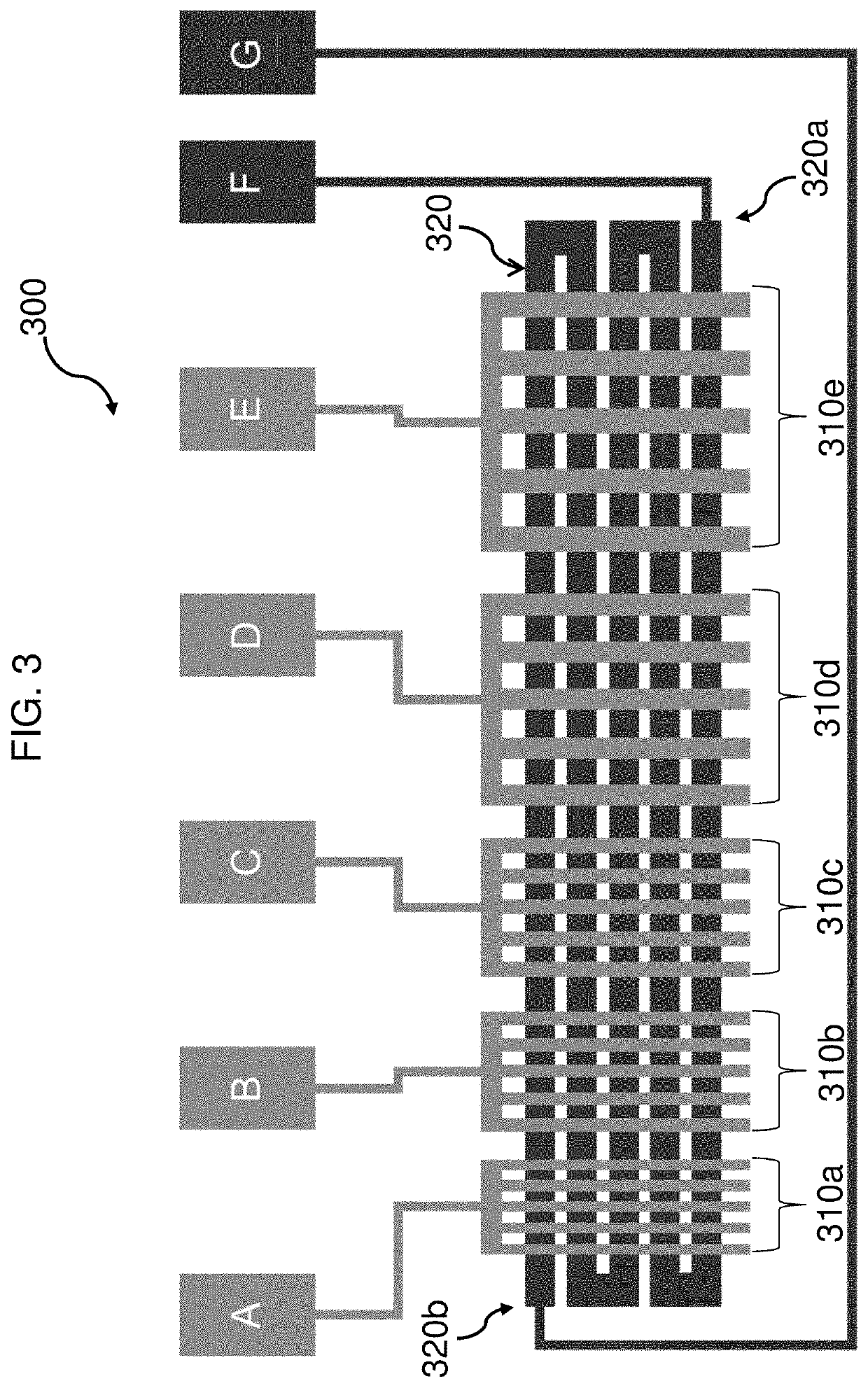

[0017]The subject matter disclosed herein relates to reactive ion etching (RIE) lag depth of semiconductor devices. More specifically, various aspects described herein relate to structures, methods and systems for measuring RIE lag depth and identifying electrical shorts of semiconductor devices.

[0018]As noted above, RIE lag can cause wide width wires to short to underlying metal even though smaller width wires have depths on target that do not short. Typically, expensive and / or destructive analysis techniques are required to determine the cause of a short (a type of failure).

[0019]The structures, methods and systems of the disclosure provide for measuring RIE lag depth and identifying the existence of an electrical short caused by unacceptable RIE lag in a less expensive and non-destructive manner. More specifically, the structures, methods and systems of the disclosure utilize less expensive electrical measuring techniques that do not destroy (e.g., require cutting) the semiconduc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| angle | aaaaa | aaaaa |

| widths | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com