Dynamic self-management buffer zone

A buffer device and self-management technology, applied in the direction of input/output to the record carrier, etc., can solve the problems of waste of logic resources, poor scalability, occupation, etc., and achieve the effect of simplifying logic design, avoiding waste of space, and convenient for expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

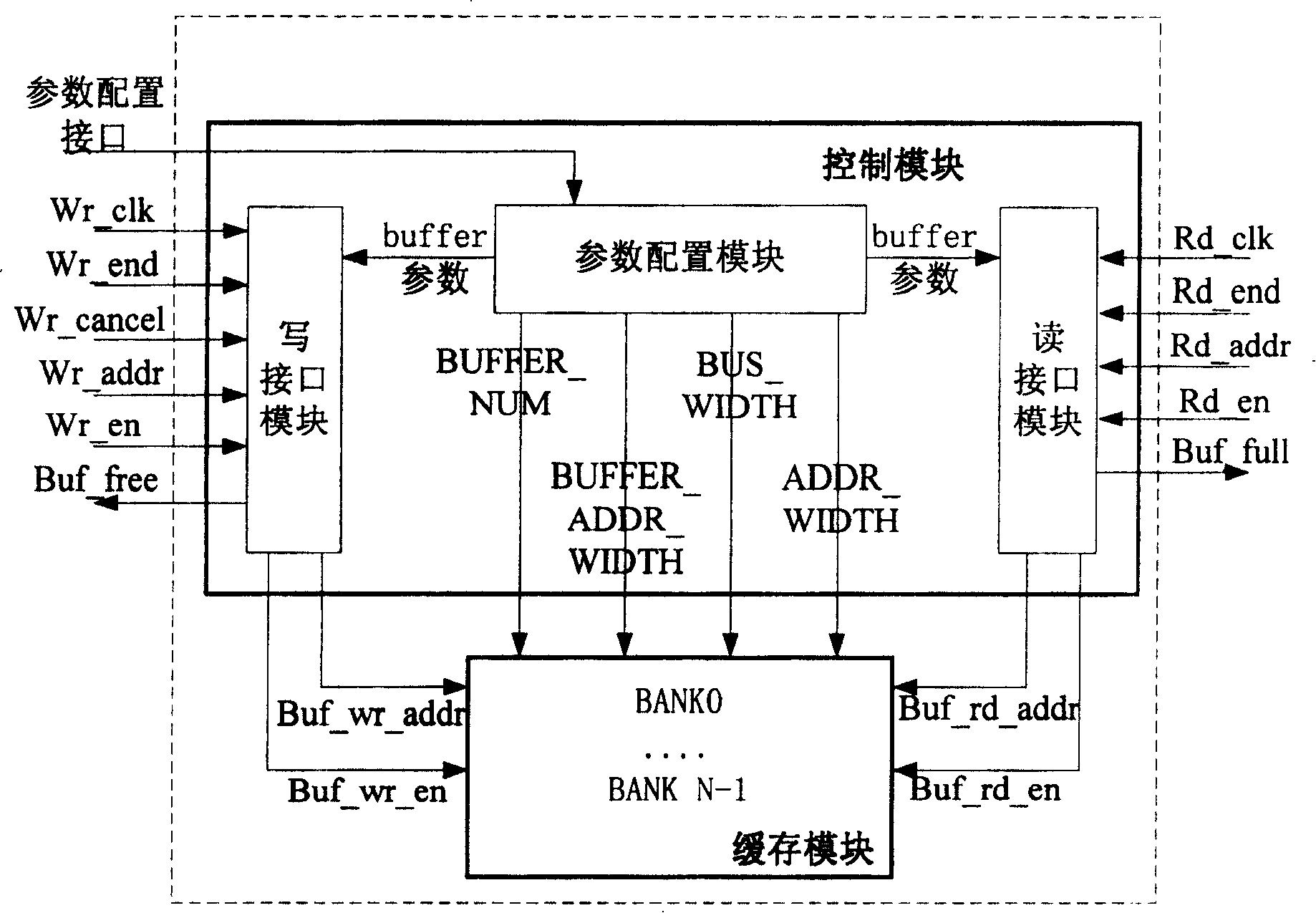

[0026] The invention provides a new buffer. The buffer provides a unified interface to the external modules. The operator does not need to care about the internal BANK structure of the buffer, and all bank switching is managed by the buffer itself.

[0027] Such as image 3 The buffer structure diagram of the present invention shown includes a control module (Control Module) and a cache module (Buffer). The cache module is internally divided into multiple BANKs; the control module controls the reading and writing of BANKs, as well as the configuration of BANKs inside the cache module. The control module further includes a write interface module, a read interface module, and a parameter configuration module. The internal management of all buffers is uniformly controlled by the control module, including realizing BANK parameter configuration, BANK empty and full flag generation, BANK automatic switching, BANK reading and writing, etc. Detailed description will be given below. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More