Matrix multiplication accelerating method oriented to general multi-core DSP

A matrix multiplication and matrix technology, applied in the field of matrix multiplication acceleration for general multi-core DSP structures, can solve problems such as difficult to meet processor DSP

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

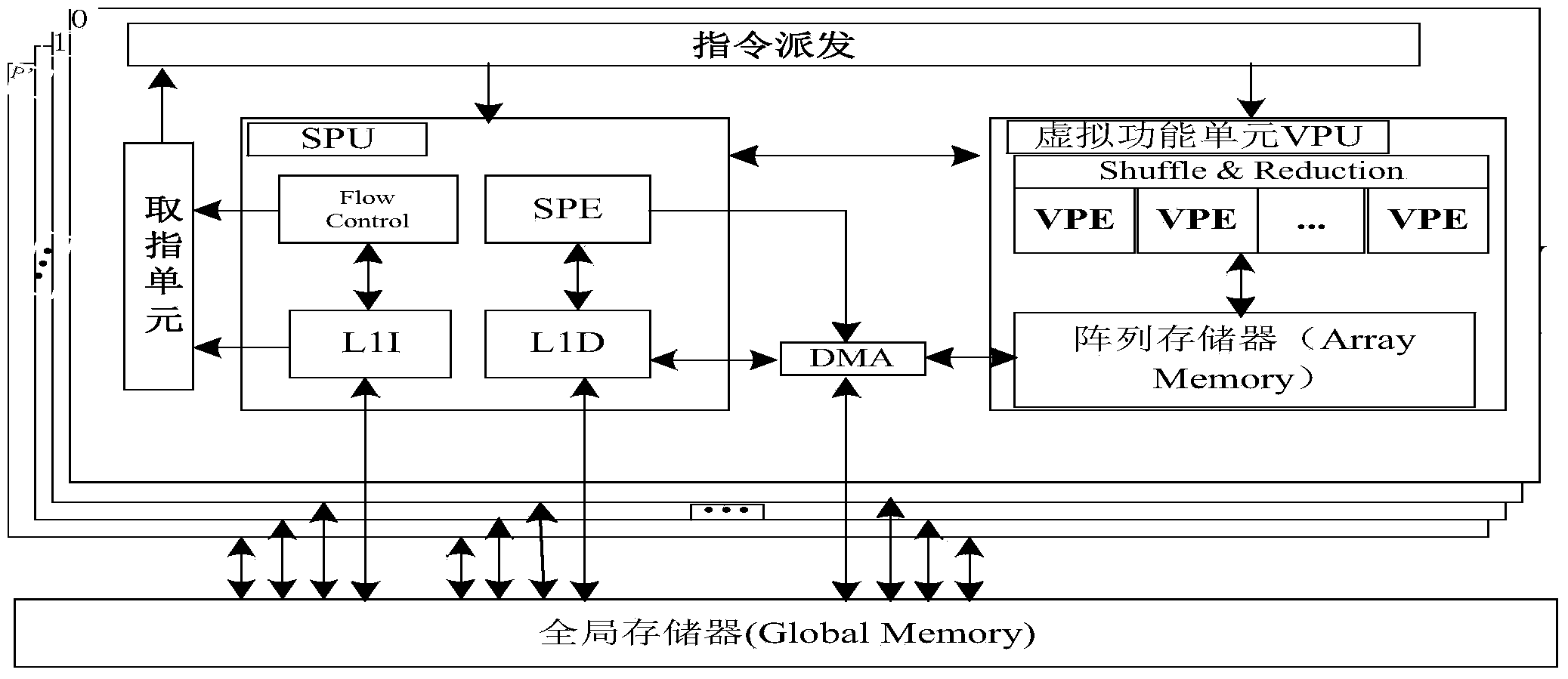

[0116] figure 1 It is a general multi-core DSP architecture;

[0117] exist figure 1 Among them, each single-core DSP is composed of SPU and VPU. SPU is composed of L1I (Level 1 Instruction) Cache, L1D (Level 1 Data) Cache, SPE (Special Processing Unit), scalar registers and flow controller. L1I is used for instructions Cache; L1D is used for data cache; SPE is used for some instruction flow control, configuration of vector units and main communication tasks; VPU includes AM (Array Memory), vector registers and multiple concurrently executable VPE (Virtual Processing Unit ), AM is mainly used for array cache, and the vector SIMD unit composed of multiple VPEs is mainly used for numerical operation acceleration.

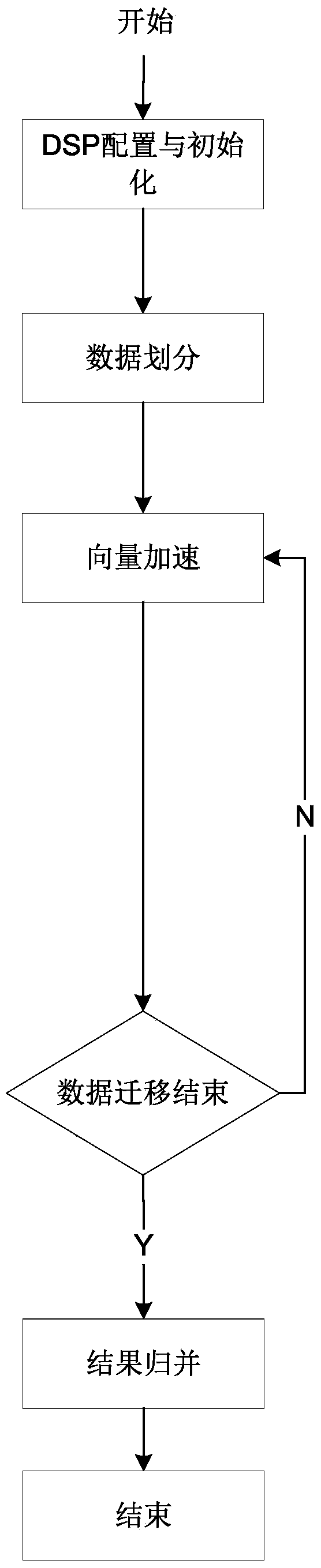

[0118] figure 2 It is the overall flow chart of the matrix multiplication acceleration method for general-purpose multi-core DSP in the present invention

[0119] The steps of the present invention are as follows:

[0120] The first step, DSP configuration and i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More