Negative Voltage Clamp Circuit

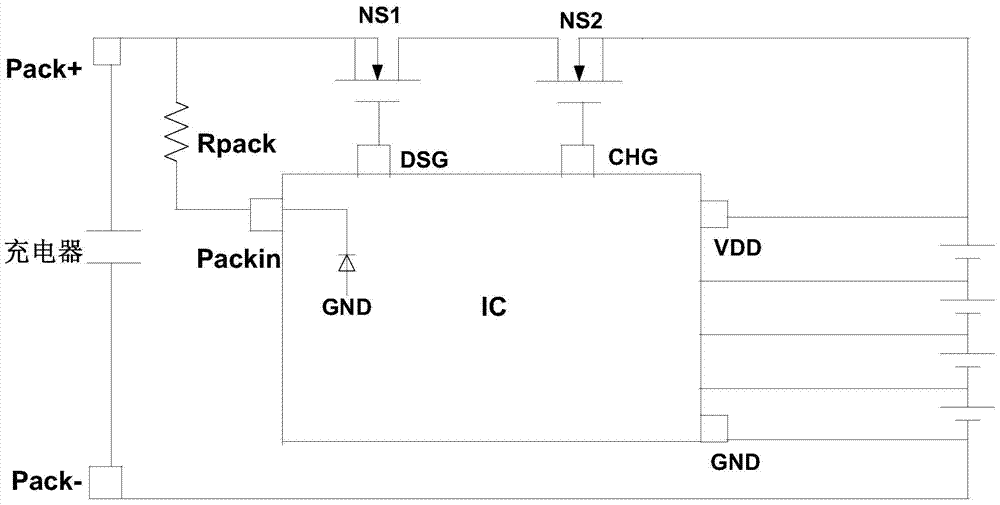

A clamp circuit and negative voltage technology, applied in the field of new negative voltage clamp circuit, can solve the problems of abnormal chip operation and unstable lithium battery protection system.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with specific embodiment and accompanying drawing, set forth more details in the following description so as to fully understand the present invention, but the present invention can obviously be implemented in many other ways different from this description, Those skilled in the art can make similar promotions and deductions based on actual application situations without violating the connotation of the present invention, so the content of this specific embodiment should not limit the protection scope of the present invention.

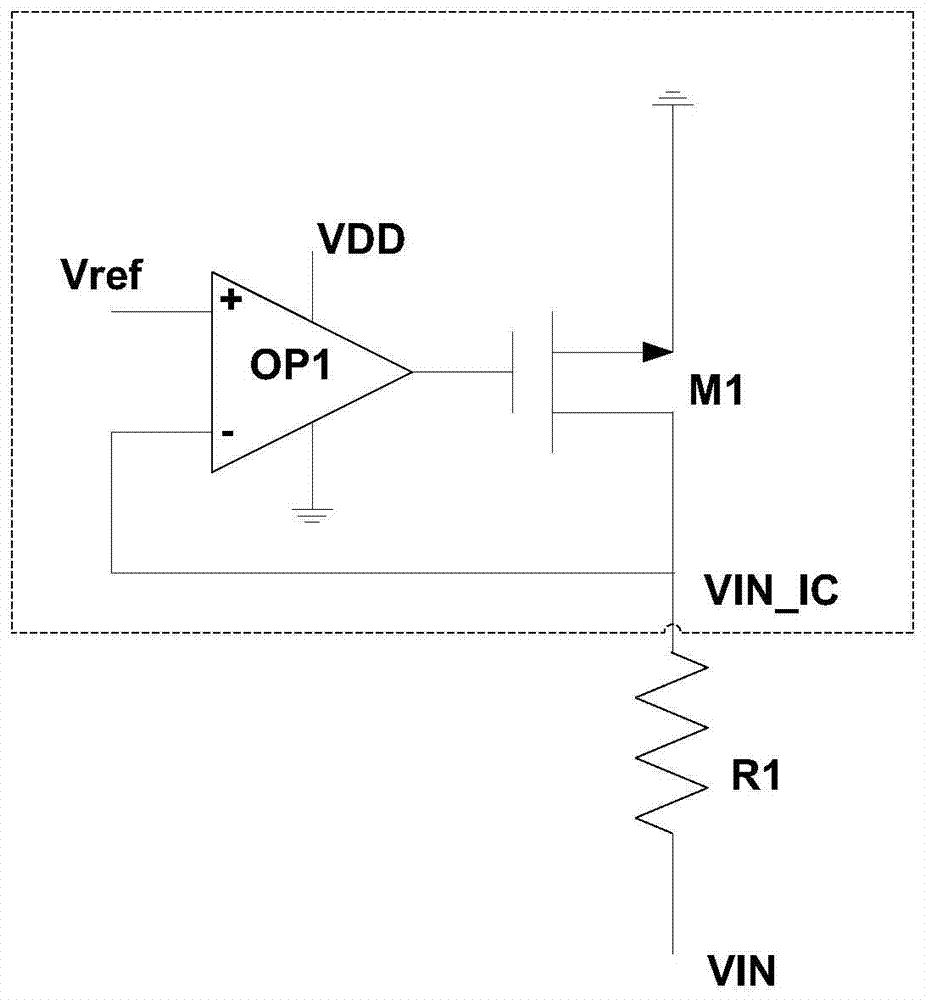

[0027] figure 2 It is a schematic structural diagram of a negative voltage clamping circuit according to an embodiment of the present invention. Such as figure 2 As shown, the negative voltage clamping circuit 200 mainly includes an NMOS transistor M1, an external current limiting resistor R1 and an operational amplifier OP1. Wherein, the positive input terminal of the oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More