Implementation method for bus arbiter for dynamically allocating bandwidth

A technology of bus arbitration and dynamic allocation, applied in the direction of instrumentation, electrical digital data processing, etc., can solve problems such as message transmission error, data interruption, bus occupation, etc., and achieve the effect of simple processing logic and increased speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In view of the deficiencies in the prior art, the inventor of this case was able to propose the technical solution of the present invention after long-term research and extensive practice. The technical solution, its implementation process and principle will be further explained as follows.

[0037] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

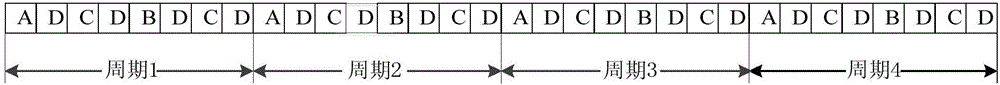

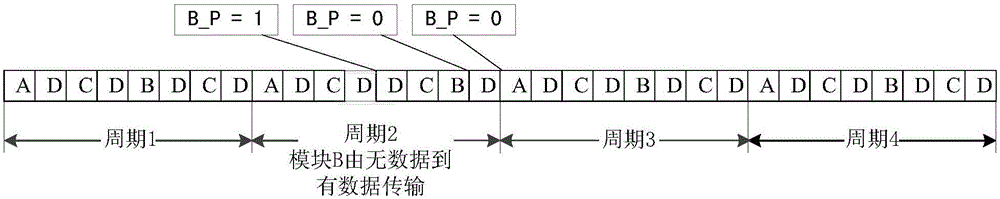

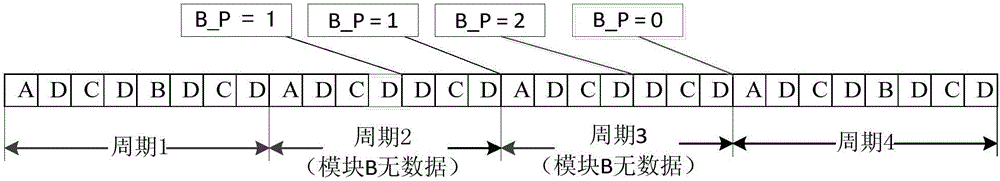

[0038] In the embodiment of the present invention, it is assumed that four data request modules A, B, C, and D are connected to the data bus, and the weights of these four modules are set to 1, 1, 2, and 4 in turn, and each 8 time slots is used as an arbitration cycle , the time slots in each cycle are...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More