Method for decoding data received from a data source using hardware configuration data received from the same data source

A hardware configuration and data technology, applied in data recording, electrical digital data processing, time or data compression/expansion, etc., can solve the problems of not providing real-time decoding performance, power consumption, and expensive digital signal processors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

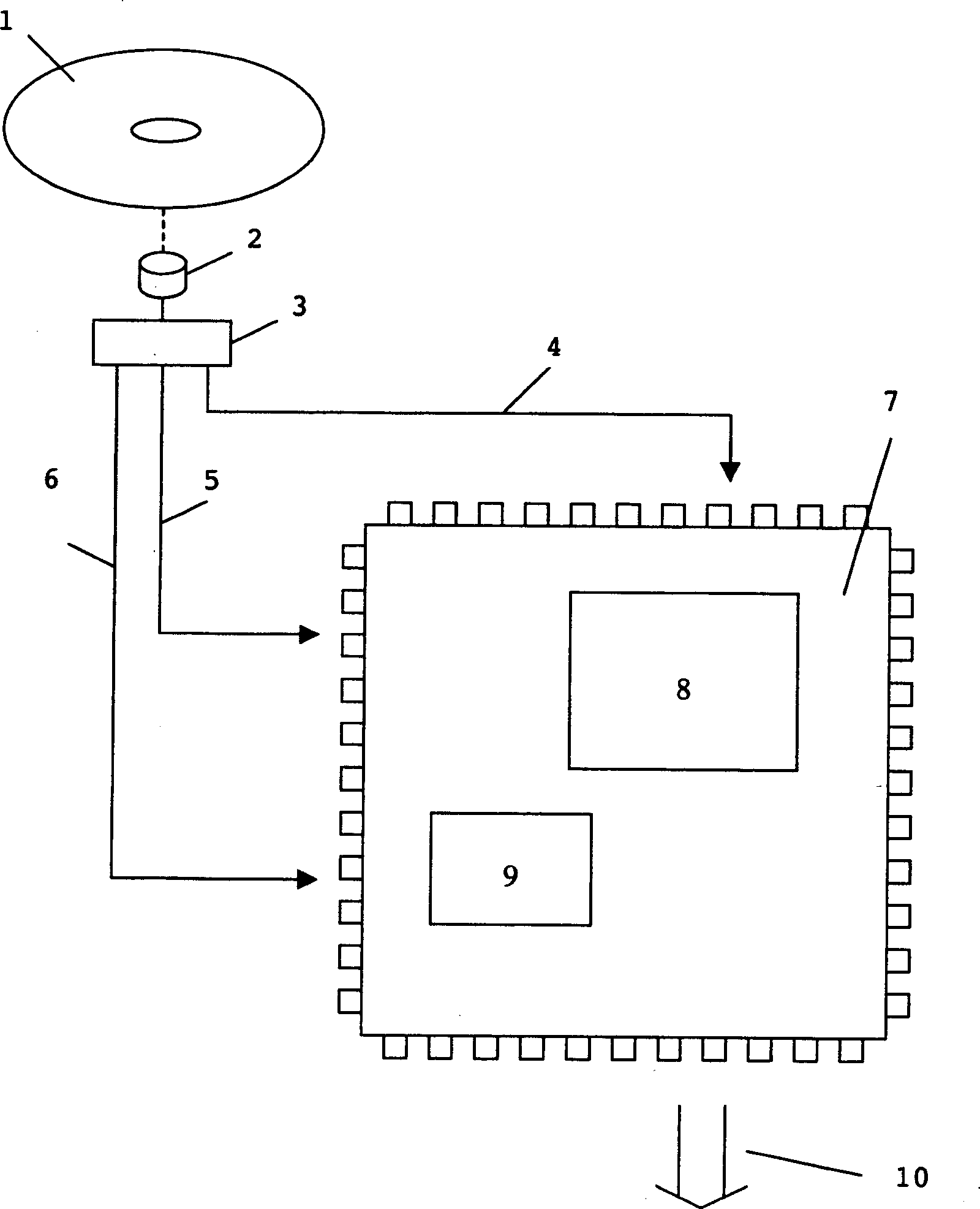

[0014] Reconfigurable architectures allow the implementation of arbitrary logic functions, covering a wide range of cost, complexity, and performance. Therefore, the present invention is based on the idea that these reconfigurable architectures can provide the decoders required by recent or future multimedia decoding schemes at a reasonable cost level cheaper than a high-performance general-purpose processor or a high-performance DSP. processing power. A reconfigurable architecture for multimedia decoding will include a programmable HW, but may also include dedicated HW and SW programmable units such as a Reduced Instruction Set Computer (RISC) or other processors such as array processors, etc. Therefore, implementing a multimedia decoder on a reconfigurable architecture may require two data streams: the configuration data stream for the reconfigurable HW; and the SW program. However, it is also possible to reduce to just the HW configuration flow or just the SW procedure. F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More