Simulation method of FLASH/electrically erasable programmable read-only memory (EEPROM)

A simulation method and functional technology, applied in the field of smart card chip simulation, can solve problems such as difficult assembly and implementation, no FLASH/EEPROM implementation form, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

[0011] The present invention will be further described below in conjunction with the drawings.

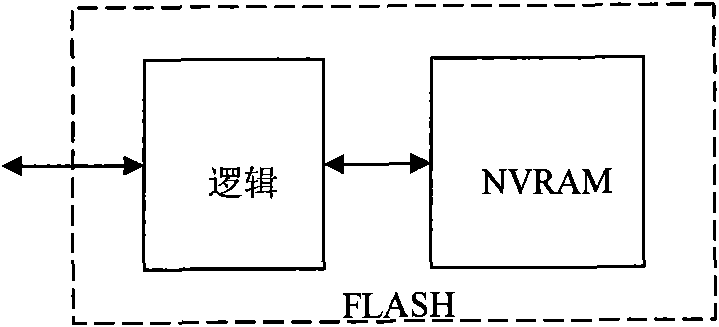

[0012] The invention discloses a FLASH / EEPROM simulation method based on NVRAM, which uses the characteristics of NVRAM to save data after power-off, and simulates the data storage function of FLASH / EEPROM; through logic circuits, it simulates FLASH / EEPROM erasing and programming Timing; Use FPGA internal RAM to simulate the page buffer area of FLASH / EEPROM;

[0013] Use FPGA internal logic to realize the function of erasing "1" and writing "0" of FLASH / EEPROM.

[0014] The logic circuit is described as follows:

[0015] Design a counting logic, such as figure 2 As shown, whether it is an erasing operation or a programming operation, the address signal of the NVRAM is generated by the output signal of the counter and the external input address signal at the same time. The read and write signal is generated according to the counter when it reaches a certain time, combined with the progra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More