Hybrid address mapping method for multi-core multi-threading processor

A multi-threaded processor, address mapping technology, applied in the direction of memory address/allocation/relocation, etc., can solve the problem of high probability of the same row, and achieve the effect of wide application range and low probability of body conflict

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] The implementation steps of the hybrid address mapping method for multi-core multi-thread processors in this embodiment are as follows:

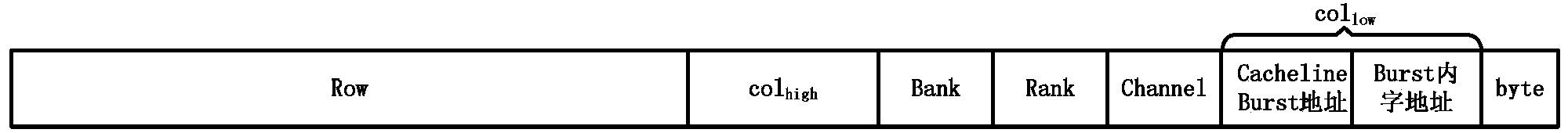

[0043] 1) Map the access address from high bit to low bit as follows figure 1 shown

[0044] high ,bank,rank,channel,col low ,byte>

[0045] Among them, row represents the row address, col high Represents the high bit of the column address, bank represents the body address, rank represents the row address, channel represents the channel address, col low Represents the low bit of the column address, byte represents the byte index address, and the low bit of the column address is used to store the Cache line burst access address (Cacheline burst address) and burst access internal word address (burst internal word address);

[0046] 2) Perform a bit operation to obtain a new memory access address according to the row address in the memory access address obtained through mapping, and perform access to the SDRAM according to the new me...

Embodiment 2

[0054] The implementation steps of the hybrid address mapping method for multi-core multi-thread processors in this embodiment are basically the same as in Embodiment 1, the main difference being step 2), and the detailed steps of step 2) include:

[0055] B1) Partial addresses are respectively intercepted from the row address as the first part of the row address and the second part of the row address;

[0056] B2) performing XOR operation on the first part of row address and body address to obtain a new body address, and performing XOR operation on the second part of row address and row address to obtain a new row address;

[0057] B3) Replace the bank address in the originally mapped memory access address with the new bank address and the new bank address, and access the SDRAM according to the replaced memory access address.

[0058] In this embodiment, the first part of the row address is located at the high side of the row address; the second part of the row address is loc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More