Wafer-level packaging method based on si conductive pillars and its monolithic integrated mems chip

A technology of wafer-level packaging and MEMS structure layer, which is applied in the direction of circuits, electrical components, and electric solid-state devices, can solve the problems of high cost, complicated process, and affecting the performance of MEMS devices, and achieve low cost, simple manufacturing process, and anti-corrosion. The effect of strong environmental interference ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

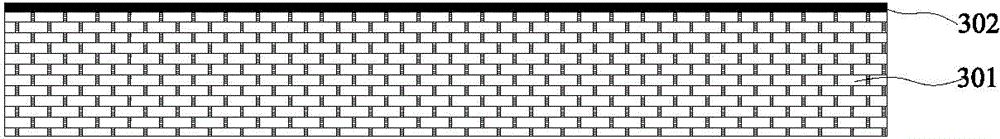

[0045] (1) MEMS wafer formation:

[0046] Oxidize the cover plate 301 to generate a cover plate insulating layer 302, such as image 3 As shown, the material of the cover plate 301 is single crystal Si heavily doped with boron, and the resistivity is about 0.01 Ω·cm, so the material of the cover plate insulating layer 302 is SiO 2 ; Glue coating, exposure, development, etching, deglue and other semiconductor processing techniques on the cover insulating layer 302 to form a cover cavity 306a on the front of the cover 301, such as Figure 4 As shown; the MEMS structure layer 303 is bonded and annealed with the cover plate 301 with the upper cavity, and the MEMS structure layer 303 is thinned to the required thickness by grinding, as Figure 5 As shown, the material of the MEMS structure layer is single crystal Si heavily doped with boron; on the MEMS structure layer 303, a deep hole 305 is etched through standard semiconductor processing steps, and in the deep hole 305, the cov...

Embodiment 2

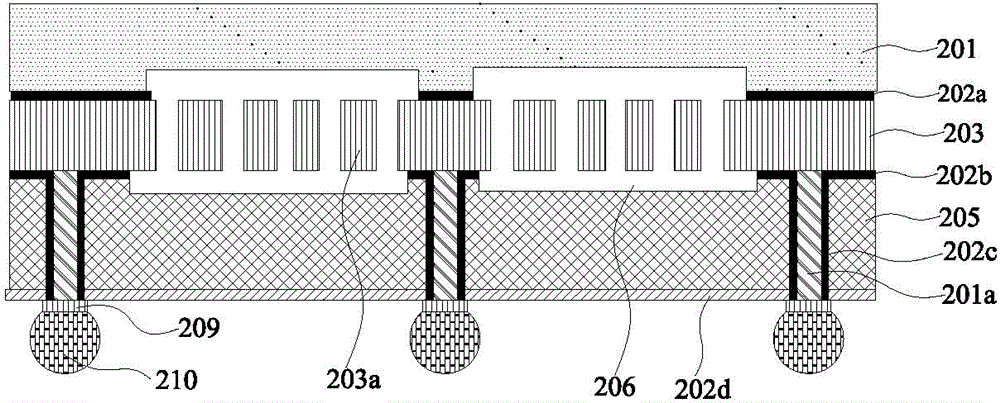

[0061] The difference between this embodiment and Embodiment 1 lies in the forming steps of the monolithic integrated MEMS chip. The monolithic integrated MEMS chip of this embodiment is formed as follows: plant solder balls 310 on metal solder bumps 309, and then Deep grooves 308 on the outside cut the composite wafer to form Figure 16 The monolithic integrated MEMS chip used for common packaging shown in the present embodiment can be directly flip-chip welded on the user's PCB board for use.

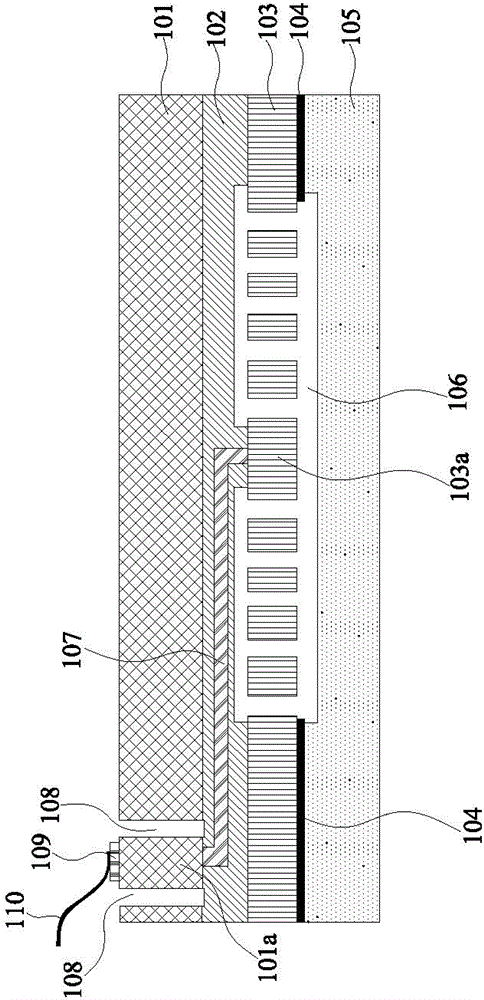

[0062] The monolithic integrated MEMS chip that present embodiment makes, as Figure 16 As shown, it is formed by bonding a cover plate 301, a MEMS structure layer 303 and an ASIC chip 400. The material of the cover plate 301 is a heavily doped Si sheet, and its resistivity is about 0.01 Ω·cm, which is a good conductive material. The MEMS structure layer 303 is divided into a MEMS structure 303a and a MEMS conductive block 303b. The MEMS structure 303a is a movable part of the MEMS s...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap