Heterogeneous multi-core programmable system and memory configuration thereof as well as programming method of computing unit

A computing unit and heterogeneous multi-core technology, applied in multi-program devices, general-purpose stored program computers, memory address/allocation/relocation, etc., can solve problems such as small storage space, complex system programming, and low system efficiency, and achieve Save space waste, compile accurately, and improve programming efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

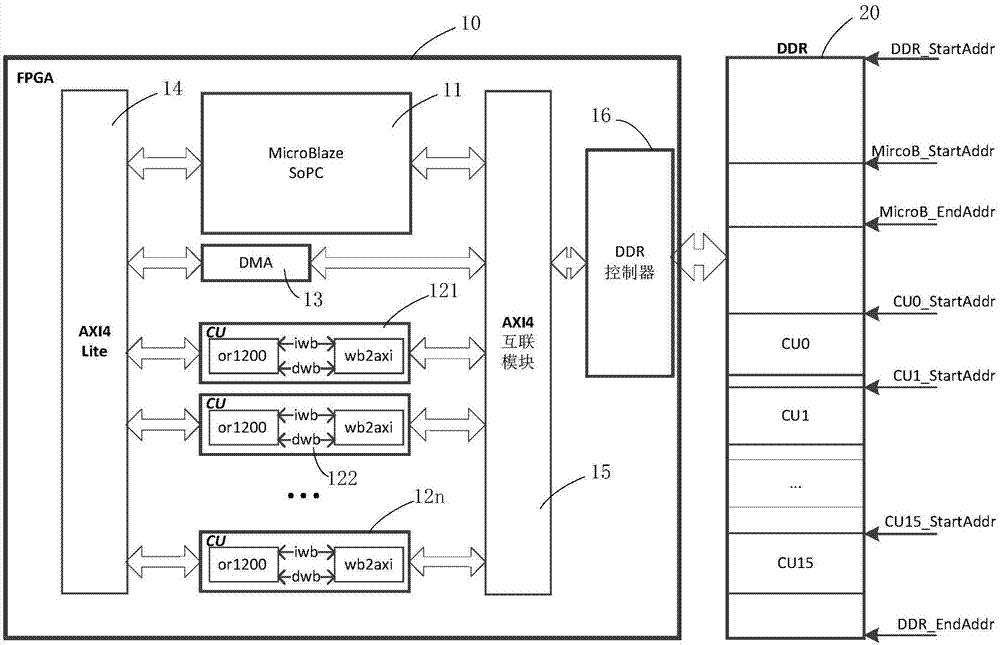

[0052] The present invention conceives a heterogeneous multi-core programmable system implemented in a single FPGA chip, which uses two CPUs with different architectures to implement a host and multiple computing units. The host is responsible for task allocation and result processing, and multiple computing units are responsible for parallel processing tasks. The task of the computing unit is configurable online, and the task of single instruction multiple data or multiple instruction multiple data can be realized.

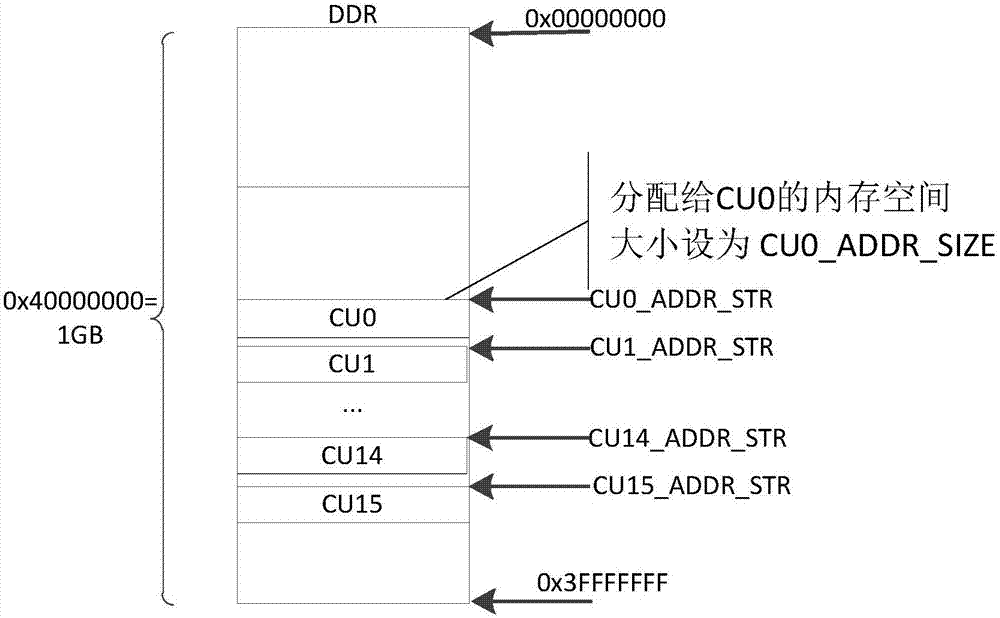

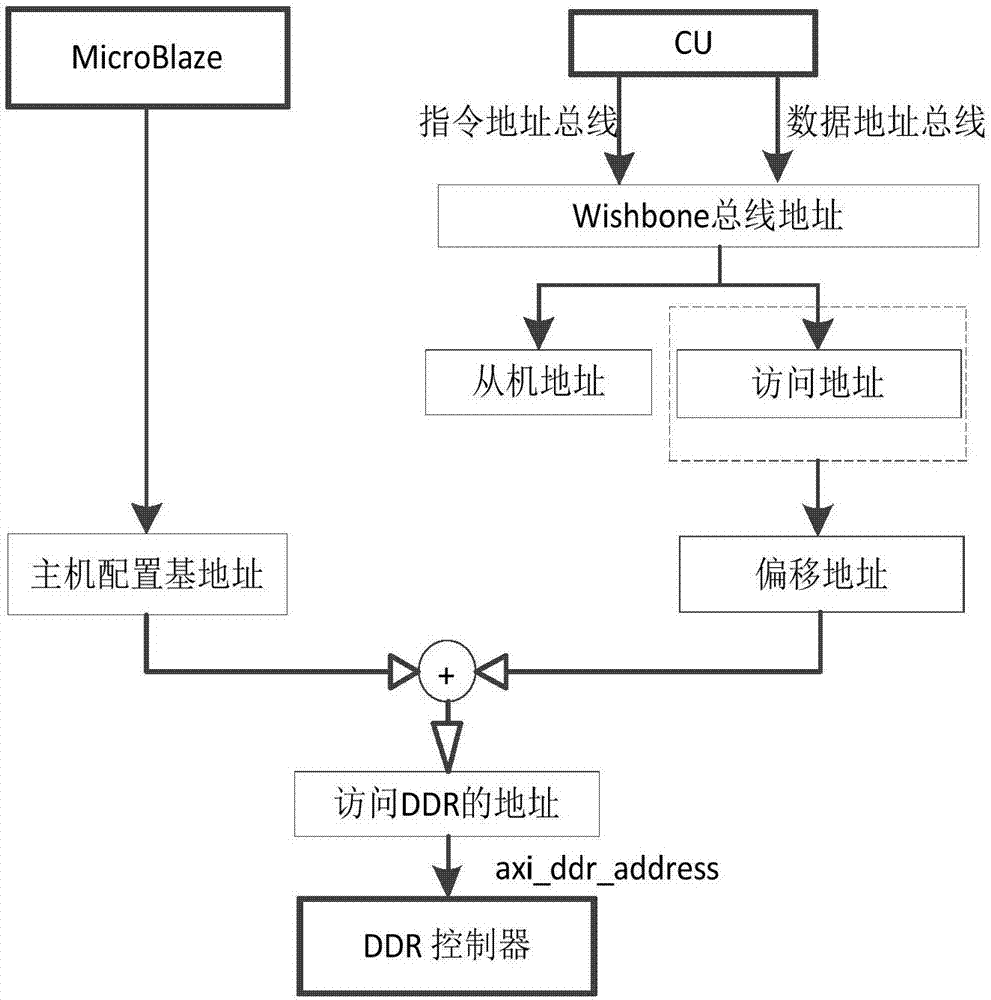

[0053] In the present invention, a dynamically configurable local data and instruction memory is realized by using the internal data and instruction buffer of the computing unit + the external DDR memory. This not only provides enough data and instruction storage space for each computing unit, but also does not slow down the speed of accessing storage.

[0054] On the basis of the programming and compiling model independently proposed by the present invention, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More