Timing Receiver Hardware Delay Calibration Method and System Based on Clock Compensation

A technology of hardware delay and calibration method, which is applied in the field of global navigation satellite systems, can solve problems such as insufficient hardware delay calibration accuracy, and achieve the effects of avoiding the influence of atmospheric errors, improving clock error accuracy, and improving calibration accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] One, at first introduce the method principle of the present invention in conjunction with accompanying drawing.

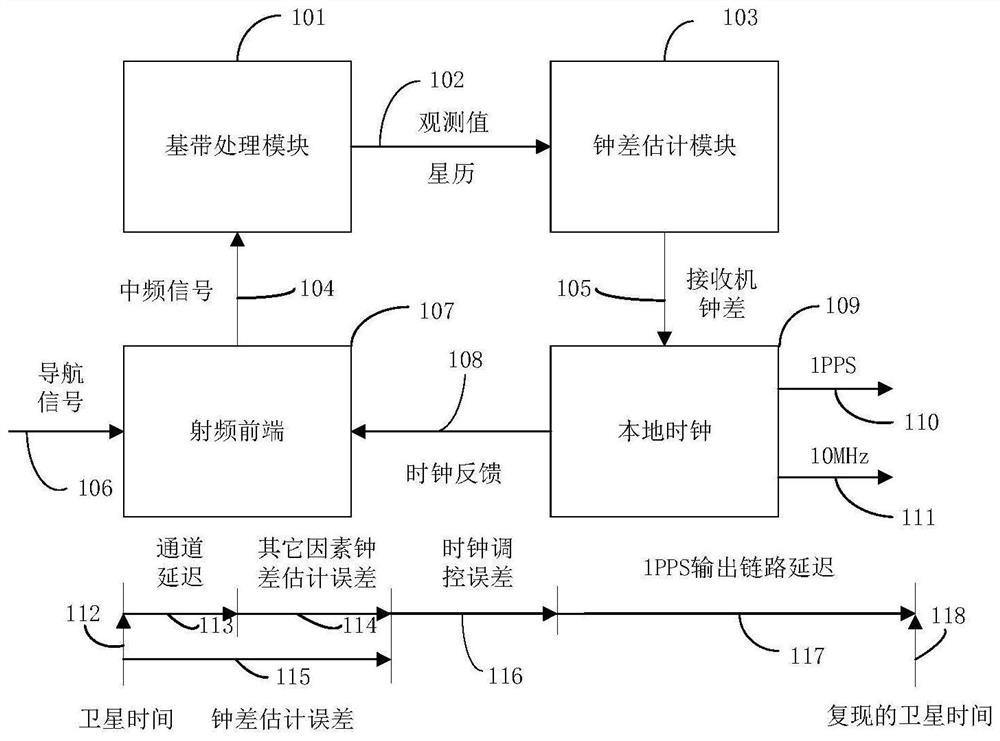

[0047] Such as figure 1 , for a timing receiver whose observation value extraction time is synchronized with 1PPS, a typical signal processing process: the satellite navigation signal 106 is first down-converted, filtered and sampled by the RF front-end 107 to obtain a digital intermediate frequency signal 104, and then the baseband processing module 101 performs a digital intermediate frequency signal 104 The signal is captured and tracked, and the observation value and ephemeris 102 are output. After the clock difference estimation module 103 is positioned and solved, the clock difference 105 of the timing receiver is obtained. The local clock 109 is adjusted according to the clock difference, and the local clock is fed back 108 to the satellite navigation signal. The receiving part forms a closed loop to keep the clock difference of the timing receiver at...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More