Comprehensive CPU model

A model and type of technology, applied in the field of logic function verification, can solve problems such as large time cost and labor cost, and achieve the effects of reducing development cycle, simple structure, and reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

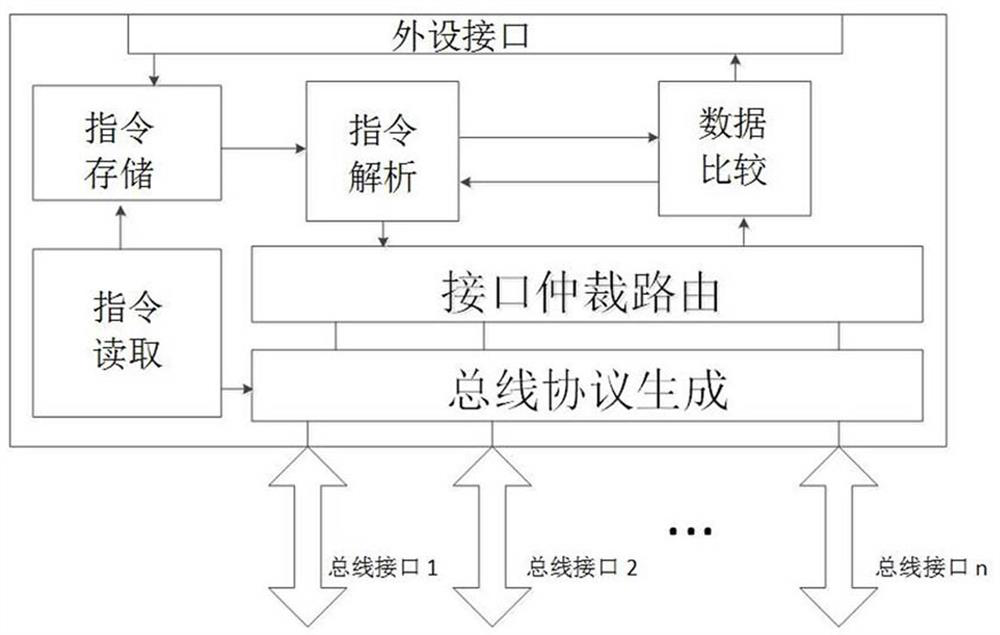

[0032] This embodiment discloses a comprehensive CPU model, such as figure 1 As shown, this CPU model mounts n bus interfaces, n is a positive integer greater than 1, and n can be configured according to system requirements.

[0033] The CPU model includes an instruction acquisition module, an instruction analysis module, a data comparison module, an interface arbitration routing module and a bus protocol generation module.

[0034] The instruction obtaining module is used to obtain the instructions required for model operation, and provide the instructions to the instruction parsing module;

[0035] The instruction parsing module realizes parsing the compiled instruction into a binary that can be recognized by the CPU to achieve the purpose of distinguishing the instruction function, and then passes the parsed instruction to the data comparison module;

[0036] The data comparison module compares the result of executing the instruction with the received instruction, so as to...

Embodiment 2

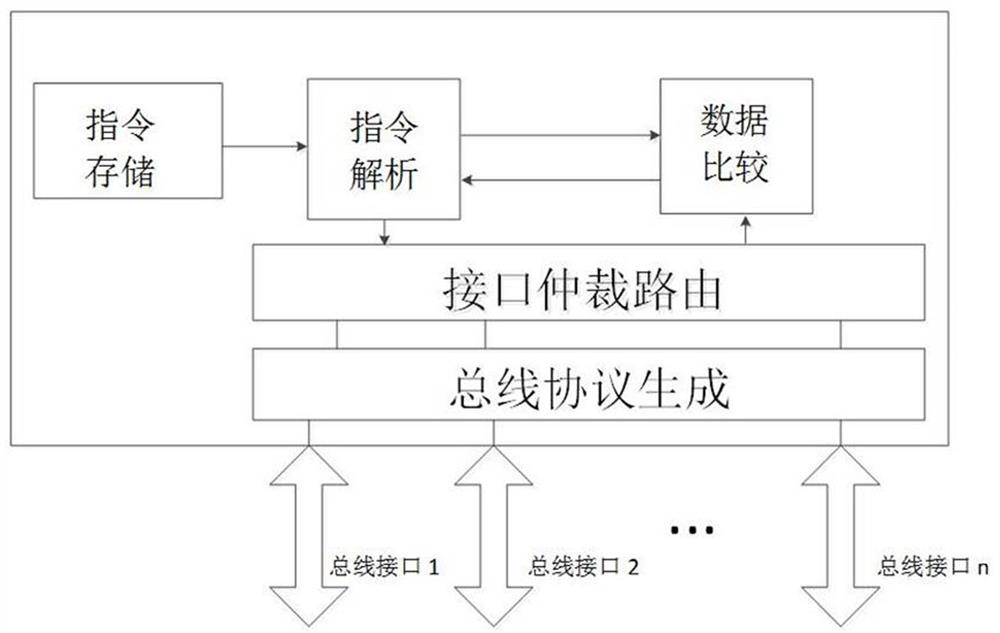

[0041] In this example, if figure 2 As shown, the instruction acquisition module is an instruction storage module, that is, the instruction is acquired by means of embedded instruction storage, and the acquired instruction is passed to the instruction analysis module.

Embodiment 3

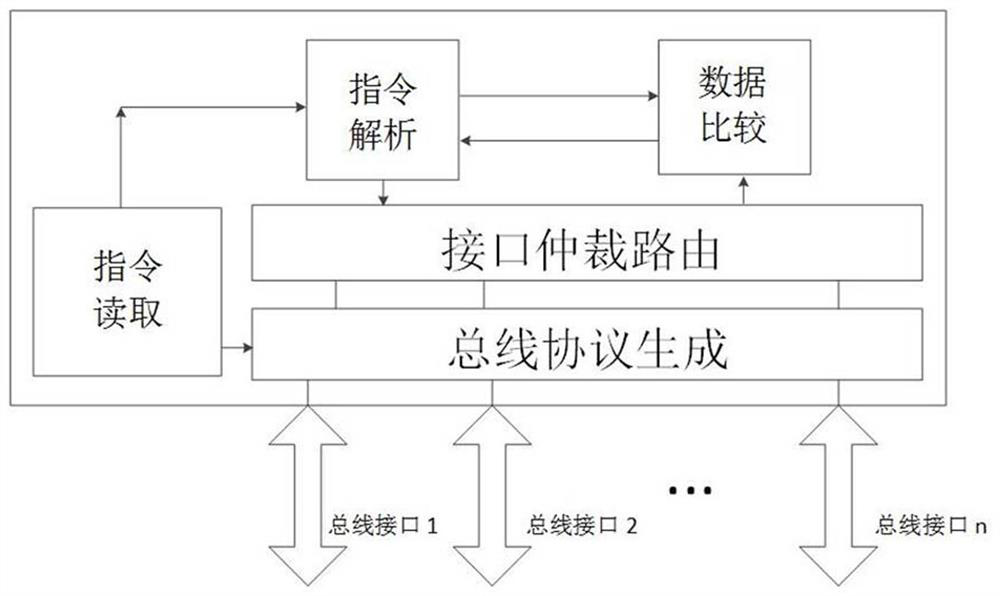

[0043] Such as image 3 As shown, the instruction acquisition module in this embodiment is an instruction reading module, that is, the instruction is obtained by reading instructions from an external storage, and the obtained instructions are passed to the instruction analysis module.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More