Flash memory device with stable source line regardless of bit line coupling and loading effect

A storage device and flash technology, applied in information storage, read-only memory, static memory, etc., can solve the problems of reduced storage unit characteristics and increased chip size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

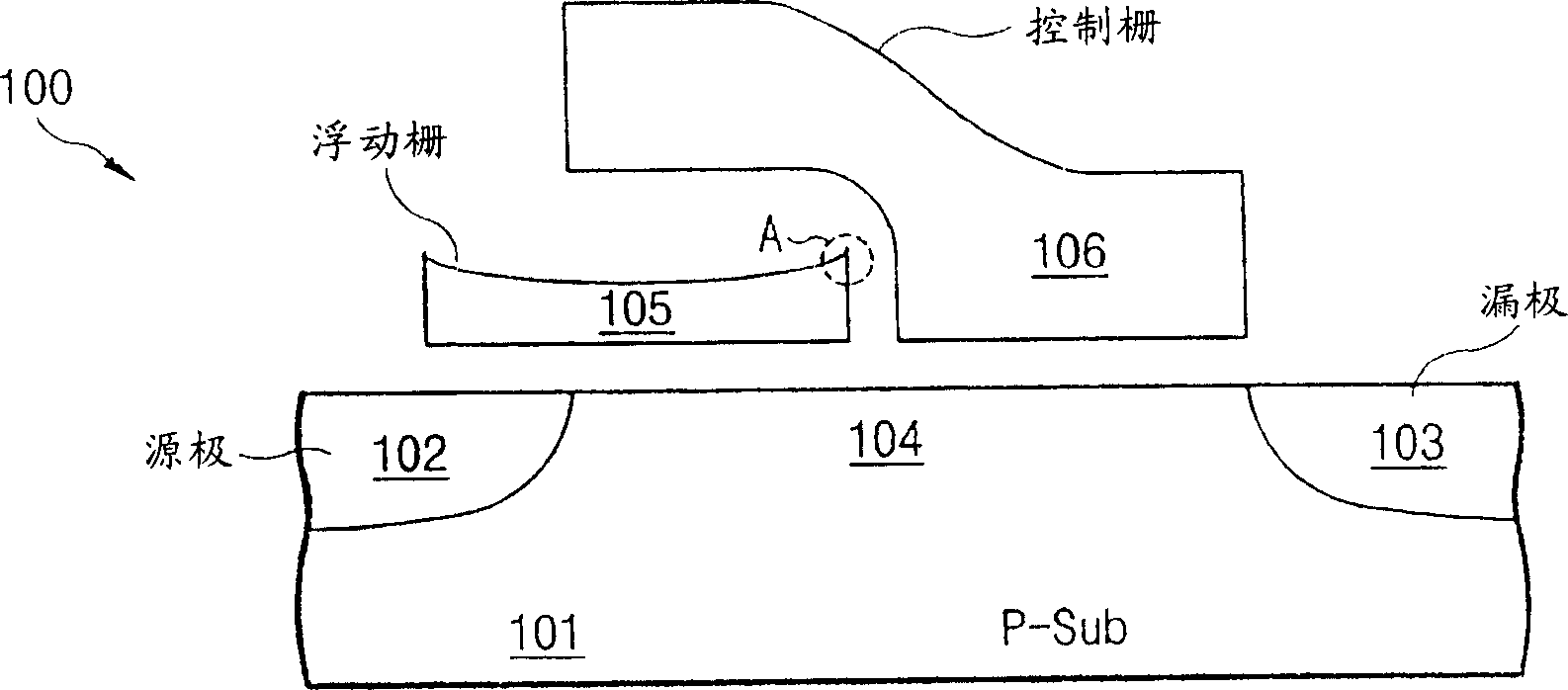

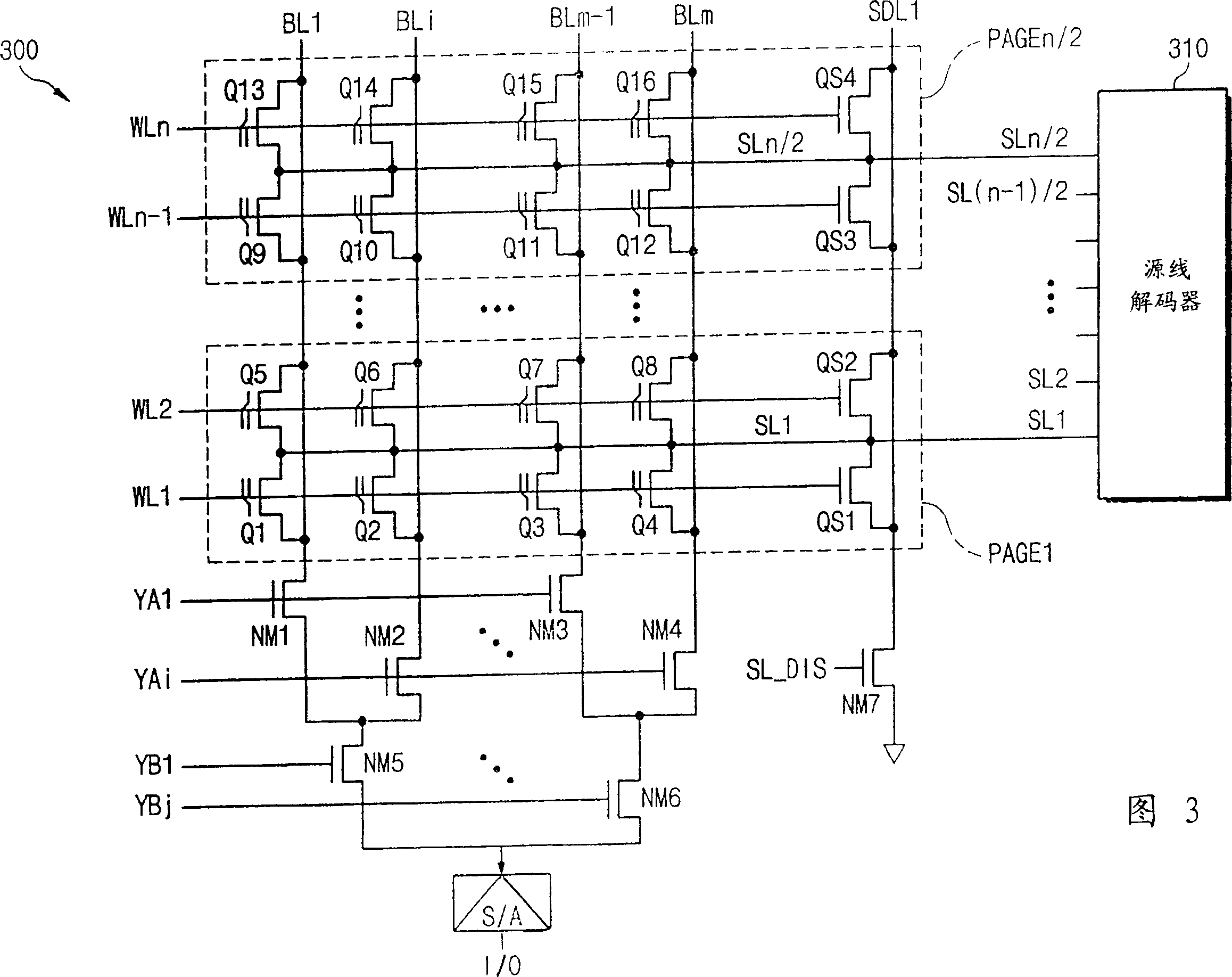

[0027] FIG. 5 is a schematic diagram of a flash memory device according to an embodiment of the present invention. Referring to FIG. 5, compared with the conventional memory cell array block 300 of FIG. 3, in the memory cell array block 300 of FIG. The cell array block 500 includes selection transistors QS51 to QS54 having the same structure as memory cell transistors Q1 to Q16. In other words, memory cell transistors Q1 to Q16 and selection transistors QS51 to QS54 are both in the form of split gate transistors as figure 1 type shown. Memory cell transistors Q1 to Q16 are "off" cells that can be selectively programmed, or "on" cells that are not programmed, while selection transistors QS51 to QS54 are "on" cells that are not programmed. In this structure, the source line discharge signal SL_DIS is inverted by the inverter INV1 and sent to the discharge line SDL1.

[0028] In this case, in the read and erase modes, a voltage of 0V is applied to the discharge line SDL1 servi...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap