Fault Tolerant Structure and Method of Cache in High Reliable System Chip

A system chip, reliable technology, applied in the direction of response error generation, error detection/correction, redundant code error detection, etc., can solve problems affecting processor execution performance, processor execution performance discount, multiple hardware resources, etc. Achieve the effect of improving fault tolerance, high reliability, and reducing system power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

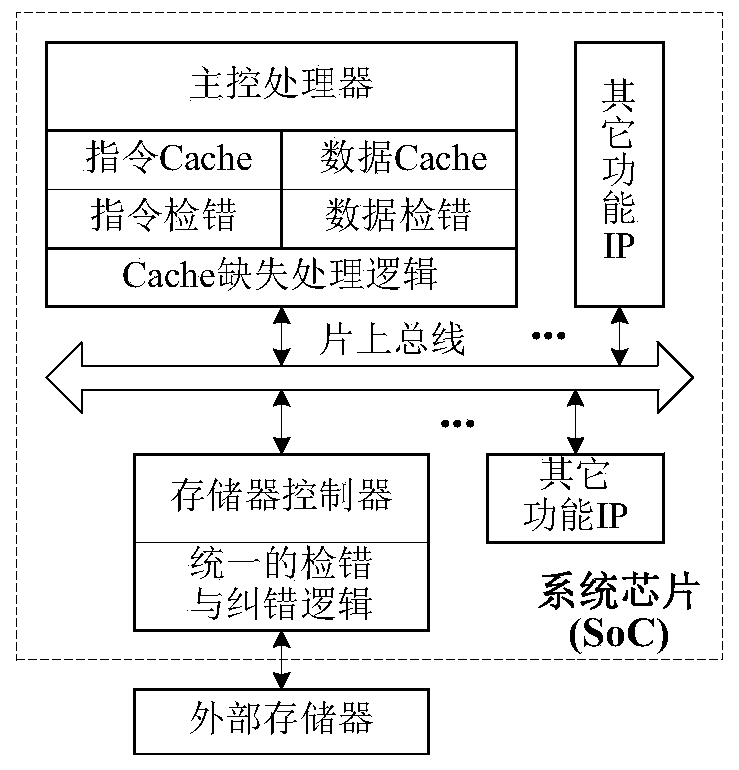

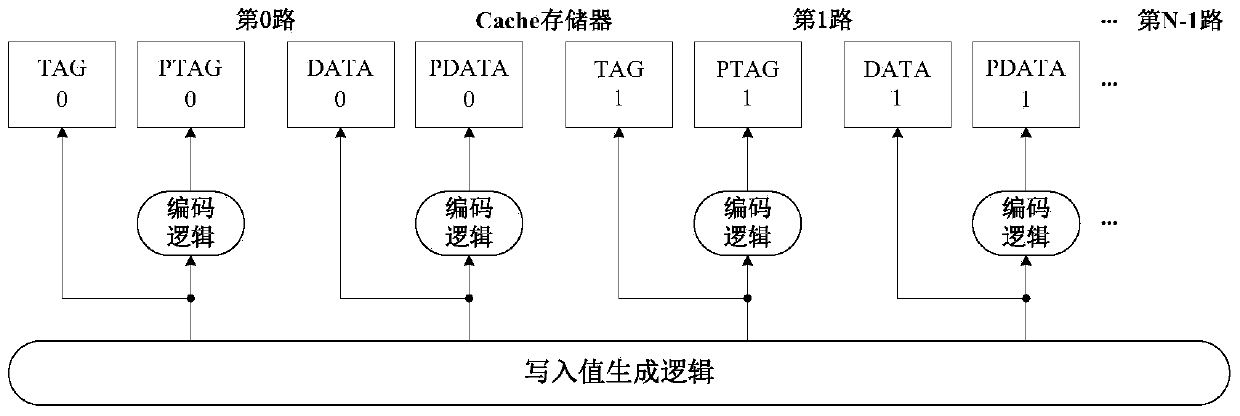

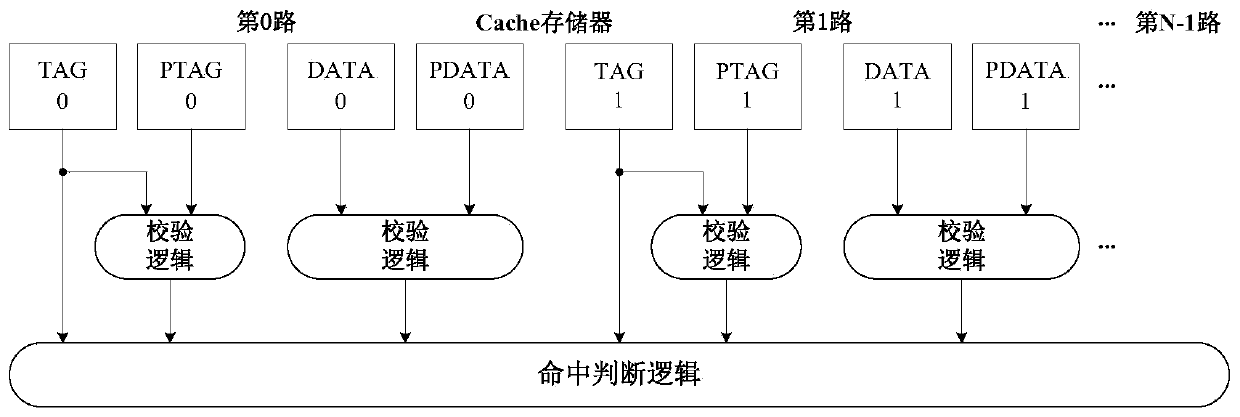

[0028] The present invention reduces additional auxiliary information through a simple parity cross-code check algorithm, thereby reducing hardware resources and power consumption; adopting an error-tolerant strategy that only detects errors but does not correct errors for Cache, and cooperates with the coding idea of cross-grouping can Guarantee the reliability of the whole system, and reduce the complexity of the design to a great extent; since the Cache memory can still cache instructions and data, it will only be processed as missing when the verification error occurs, so the overall system There is no noticeable loss in execution performance. In the system chip design, a highly reliable Cache fault-tolerant structure is realized without introducing obvious hardware resources, power con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More