FPGA realization module and FPGA realization method for signal subspace decomposition by time-sharing multiplexing of hardware resources

A technology of signal subspace and hardware resources, applied in the field of FPGA implementation modules, can solve the problems of consuming hardware resources and reducing the speed of decomposition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

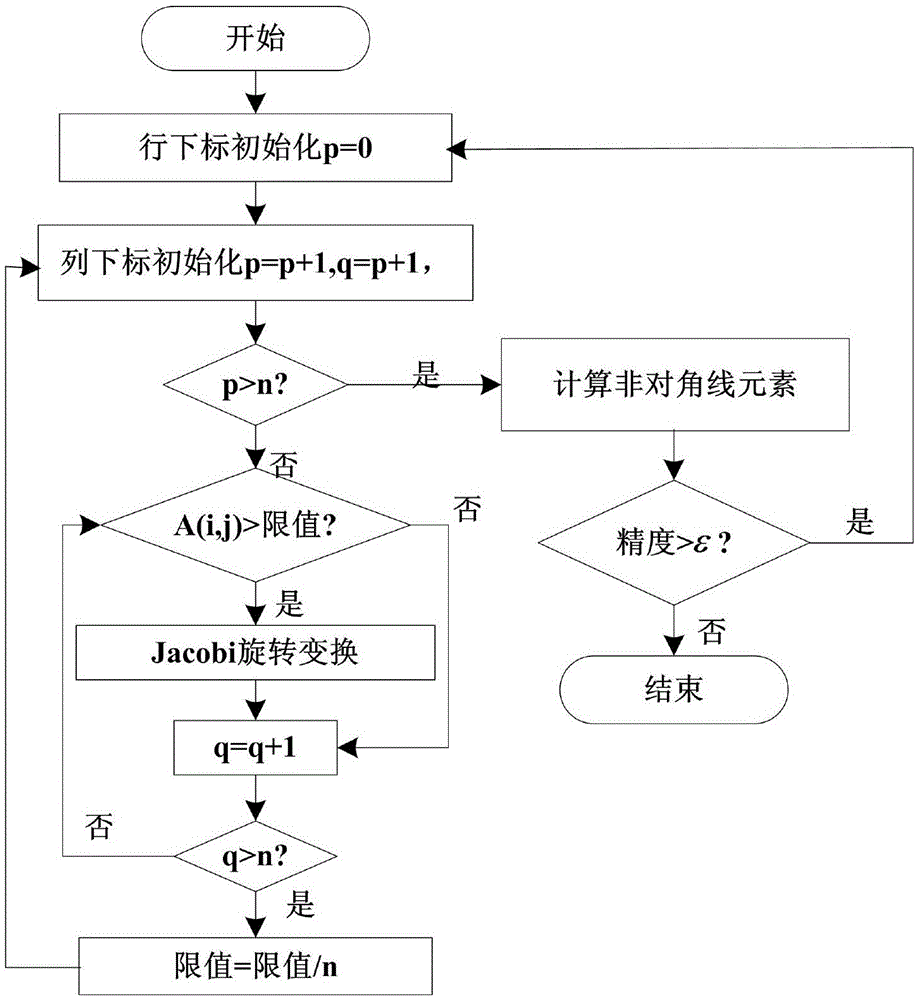

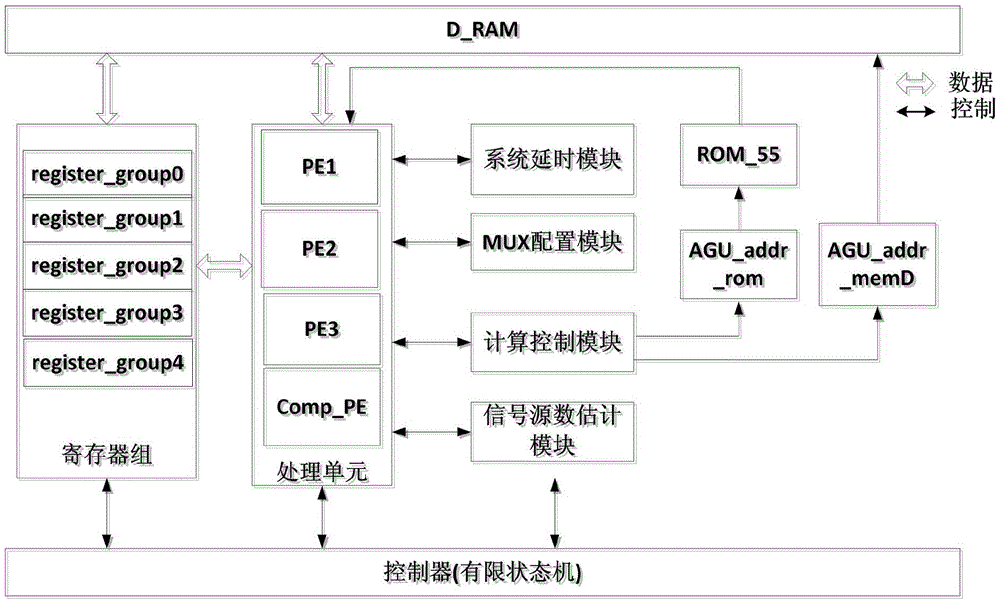

[0062] In this embodiment, an FPGA implementation module for signal subspace decomposition of time-division multiplexing hardware resources, including an automatic sorting pass Jacobi algorithm unit and a space signal source number estimation calculation unit;

[0063] In this embodiment, the overall execution flow chart of the Jacobi algorithm for automatic sorting is as follows: figure 1 As shown, the automatically sorted clearance Jacobi unit reads the N-order covariance matrix Α=[a pq ] n×n And perform operations to obtain a diagonal matrix Α of order N k ;diagonal matrix Α k The elements on the main diagonal of are the eigenvalues λ of the Nth order covariance matrix A 1 ,λ 2 ,...,λ p ,...,λ q ,...,λ n ; and λ 1 ,λ 2 ,...,λ p ,...,λ q ,...,λ n Sort in descending order; 1≤p≤n; 1≤q≤n; p≠q;

[0064] In the specific implementation, if the number of array elements is set to be 8, then the covariance matrix Α is an 8-order matrix, 64 elements are arranged in Α, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More