Dual Rail Precharge Logic Device

A logic device and pre-charging technology, applied in secure communication devices, electrical components, digital transmission systems, etc., can solve problems such as increasing clock edge transient power consumption, reduce complexity, ensure the ability to resist DPA attacks, eliminate The effect of power differences

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

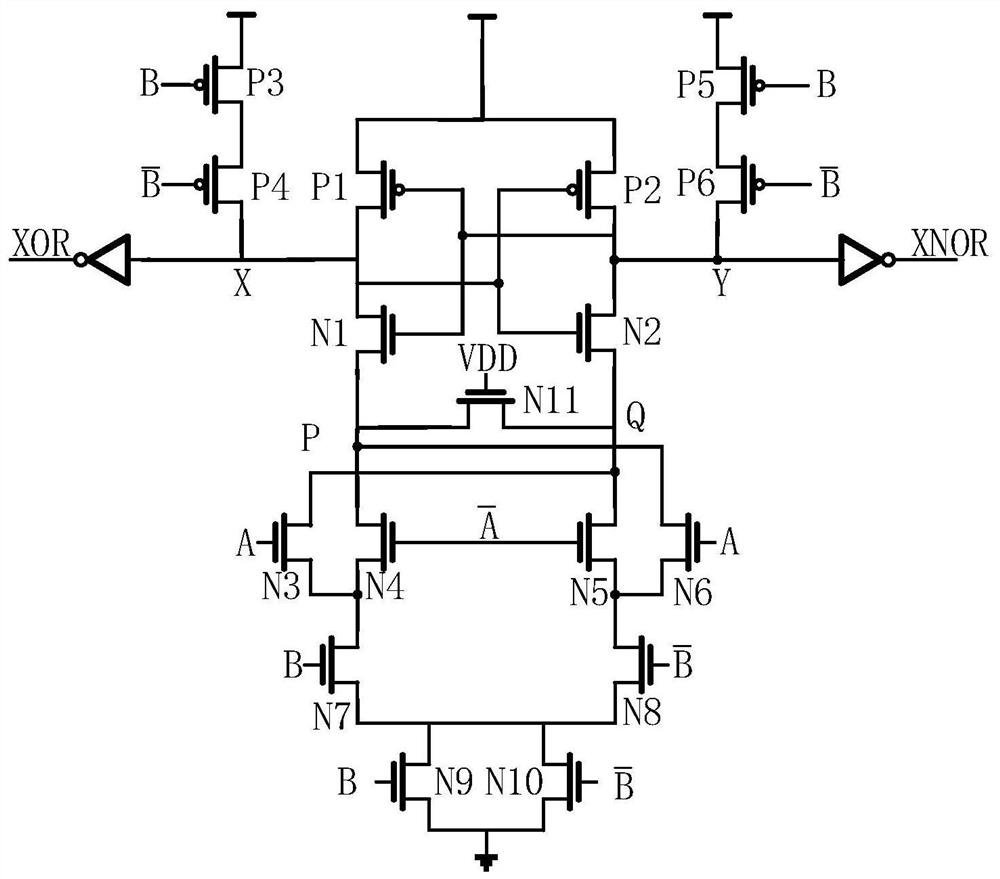

[0017] In order to solve the above problems, the present invention proposes a new dual-rail precharge logic unit, which inherits the advantages of the SABL unit, that is, it has a complementary topology structure, which ensures that the discharge conditions of the internal nodes are the same under different inputs, and at the same time A new pre-charge structure is adopted to replace the original clock signal, making the new dual-rail pre-charge logic unit compatible with the existing design process.

[0018] In order to improve the anti-DPA attack capability of the unit, a dual-rail pre-charged logic unit is proposed. Combine below figure 1 The unit structure and working principle of the standard unit are introduced. The basic structure of the logic unit is SABL logic, figure 1 It is a circuit diagram of the XOR / XNOR unit of an improved SABL structure, where A, B, It is the input signal of the unit, and XOR and XNOR are the output signals of the unit. Compared with the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More