Power flattening standard integrated circuit

An integrated circuit and standard technology, applied in the field of anti-power attack and information security, can solve the problems of increasing the difficulty of clock signal layout and wiring, TDPL unit protection failure, etc., to ensure the ability to resist DPA attacks, avoid protection failure, Effect of Eliminating Differences in Power Consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

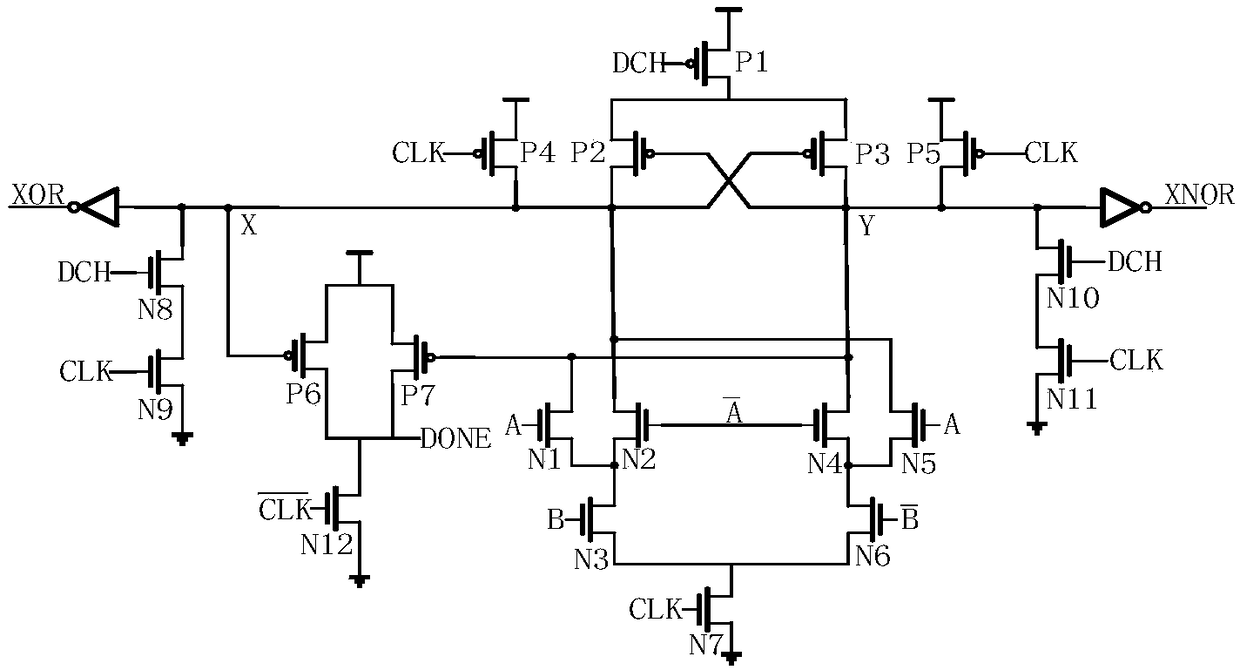

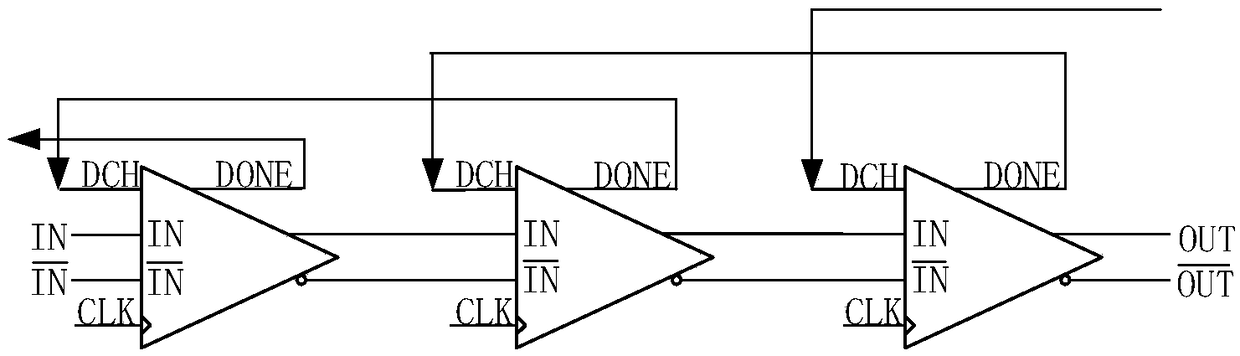

[0018] In order to solve the problems in the prior art, the present invention proposes a self-timed three-stage dual-rail precharge logic unit (ST-TDPL) based on the three-stage dual-rail precharge logic. This unit only uses a clock signal, but still maintains The three-stage working mode reduces the complexity of the unit on the basis of realizing that the power consumption is independent of the internal signal, and at the same time improves the safety performance of the unit.

[0019] To improve the anti-DPA attack capability of the cell, a novel self-timed three-stage dual-rail precharge logic structure (ST-TDPL) is proposed. Combine below figure 1 with figure 2 The unit structure and working principle of the standard unit are introduced. The basic structure of the logic unit is dual-rail dynamic logic, figure 1 It is a circuit diagram of an XOR / XNOR unit of ST-TDPL structure, where A, B, are the unit input signals, CLK and It is the clock control signal of the unit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More