A kind of synchronization circuit and synchronization method based on ddr read data integer clock cycle

A clock cycle and synchronous circuit technology, applied in the direction of generating/distributing signals, etc., can solve the problems of difficulty in determining the phase of data and internal clock, increase of comparison logic, speed loss, etc., to achieve integer clock cycle synchronization, reduce complexity, high speed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

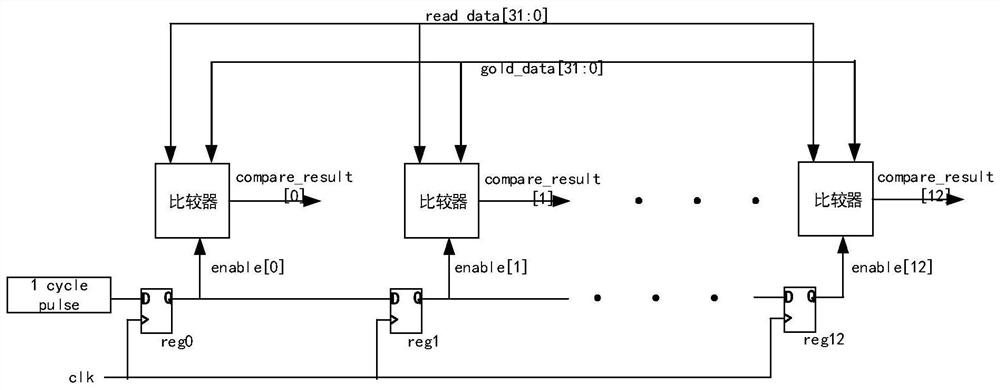

[0073] Such as figure 1 As shown, reg0~reg12 are 13 registers (register reg), 1 cycle pulse is a pulse of 1 clock cycle, the comparator logic means that the comparator has 3 inputs, one is gold_data (reference data), and the other is read_data (physical layer The data read from the IO is the above DDR read data), one is enable (comparator enable).

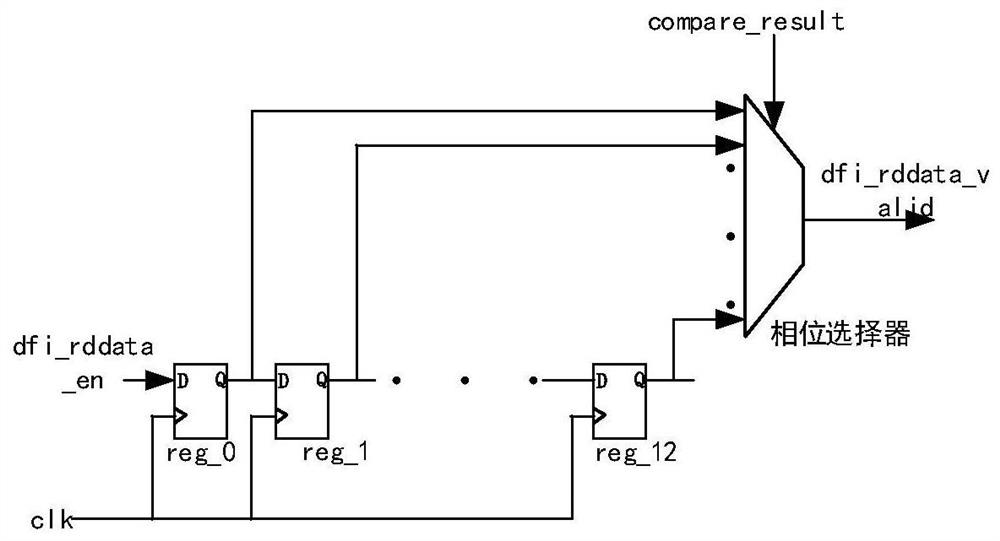

[0074] Such as figure 2 As shown, reg_0~reg_12 are 13 registers (register reg_). This circuit is the effective selection logic for reading data, and the selection signal is the output result of the compare_result comparator.

[0075] The 13 registers reg0~reg12 are connected in series to generate 13 pulses delayed by one beat in turn, which are used as the enable signal of the comparator, where reg0 corresponds to enable[0], and reg1 corresponds to enable[1], which are inferred sequentially. reg12 corresponds to enable[12]. Both gold_data and read_data are 32bit data. The generation of 1cycle pulse is a signal of 1 clock cycle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More