Method for designing embedded, isomorphic, symmetric and dual-core microprocessor

A design method and embedded technology, applied in machine execution devices, concurrent instruction execution, etc., can solve the problems of no articles published, no mature chips available, and multi-core research work has not really started, to maintain synchronization and good synchronization. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

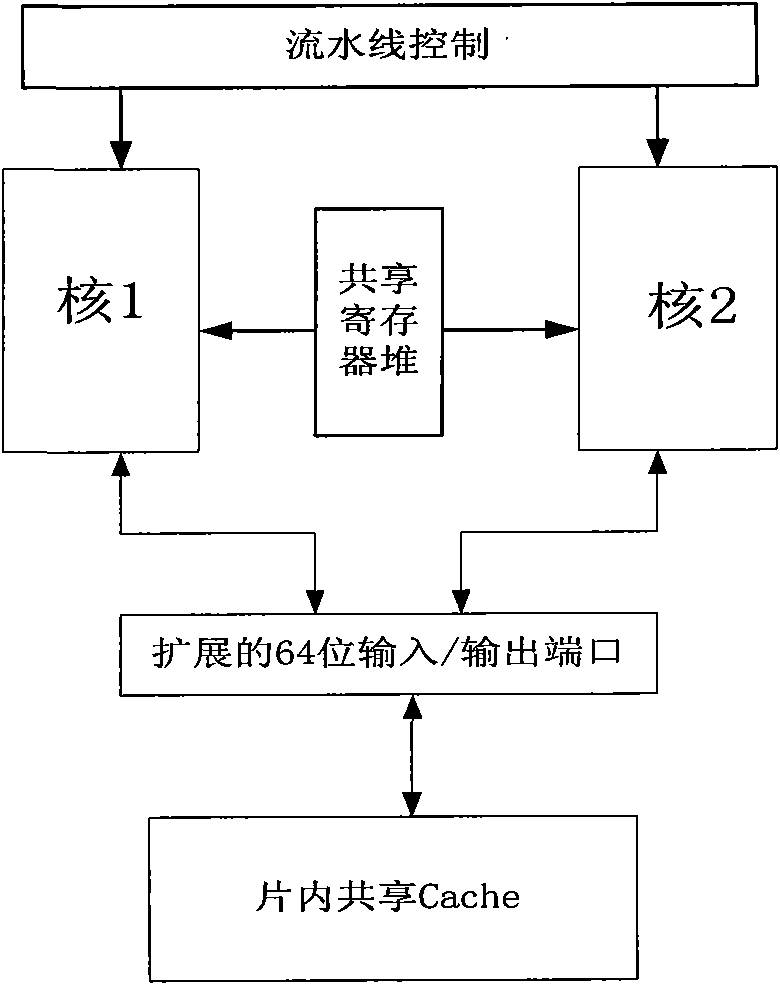

[0043] see figure 1 , the dual-core microprocessor implementation method based on shared register set of invention, carries out in the following manner:

[0044] 1) Use common PC registers to realize the synchronization of dual-core instruction fetches, avoiding repeated instruction fetches or omissions of instruction fetches by two cores, that is, dual-cores;

[0045] 2) Use the shared register file to realize the flexibility of dual-core resource sharing and data exchange, avoiding the need to expand the instruction set to achieve data sharing;

[0046] 3) By adopting the register correlation elimination strategy and the pipeline control merging strategy, the two pipelines are managed in a unified manner, and the work coordination of the two pipelines is realized.

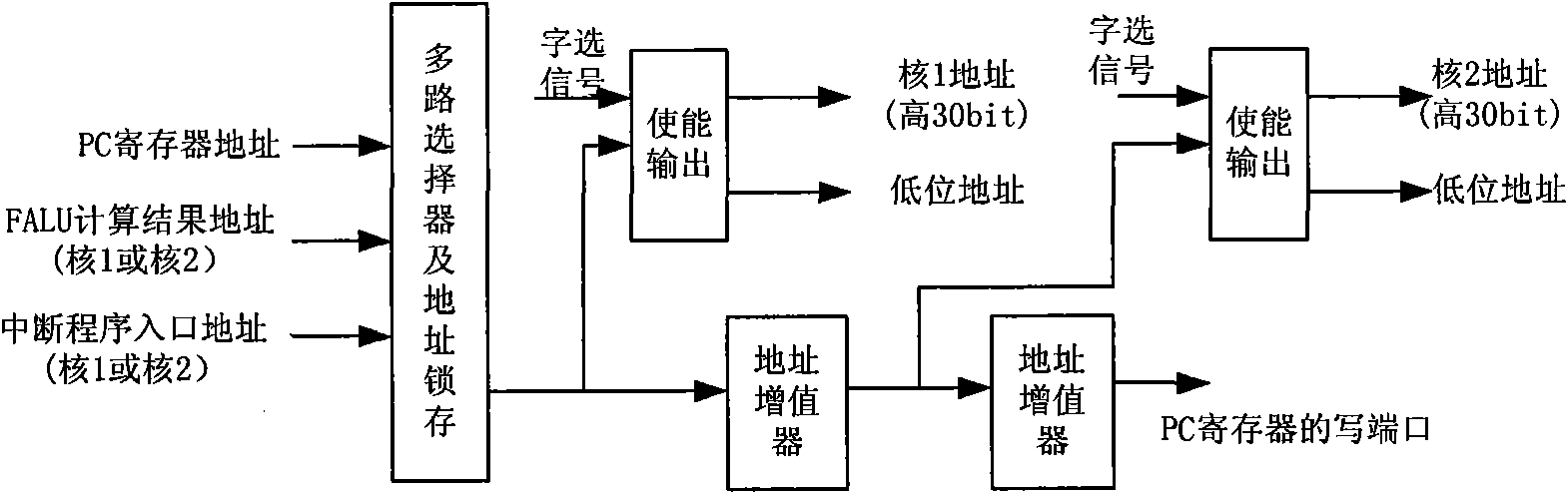

[0047] The above common PC register scheme: core 1 and core 2 share a PC r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More