Polishing process of 8-inch polished wafers doped with silicon lightly

A silicon polishing wafer and lightly doped technology, which is applied in polishing machine tools, manufacturing tools, metal processing equipment, etc., can solve the difficulty of developing 8-inch lightly doped silicon polishing wafers and other problems

Active Publication Date: 2012-05-09

ZHONGHUAN ADVANCED SEMICON MATERIALS CO LTD +1

View PDF0 Cites 3 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

This has brought greater difficulty to the development of 8-inch lightly doped silicon polishing wafers

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

[0016] The wax polishing process of 8-inch 725μm thick lightly doped silicon wafer is as follows:

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

Login to View More

Abstract

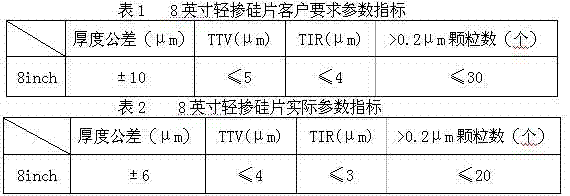

The invention relates to a polishing process of 8-inch polished wafers doped with silicon lightly. In the process, a waxed single-surface polishing system is adopted, and two-time rough polishing, one-time medium polishing and one-time finish polishing are comprised. Each time of polishing is carried out in four stages. The polishing pressure of each stage of rough polishing is set in a range of 1.5 -2.2 bar. The total polishing time of the four stages of the rough polishing is set in a range of 8-11 min. The polishing pressure of each stage of medium polishing is set in a range of 1.2 -2.0 bar. The total polishing time of the four stages of the medium polishing is set in a range of 7-10 min. The polishing pressure of each stage of finish polishing is set in a range of 0.5 -1 bar. The total polishing time of the four stages of the finish polishing is set in a range of 7-10 min. According to the process, the surface geometric parameters and other quality indexes of the polished wafers doped with silicon lightly are improved, and all of the indexes reach and exceed industrial standards, therefore, the technical problem that traditional process is not suitable for polishing 8-inch polished wafers doped with silicon lightly is solved.

Description

Technical field [0001] The invention relates to a silicon wafer manufacturing process for semiconductor power devices, in particular to a polishing process for an 8-inch lightly doped silicon polishing wafer. Background technique [0002] Silicon wafer polishing is the use of chemical and mechanical action to finally eliminate the damage and deformation layer on the surface of the silicon wafer. Chemical mechanical polishing combines the characteristics of chemical polishing without damage and mechanical polishing to obtain a smooth and bright surface. In the polishing process, the two effects of chemical corrosion and mechanical friction are carried out alternately and cyclically to remove the residual mechanical damage on the surface of the silicon wafer due to the previous process, thereby obtaining a smooth, bright, non-damaged, and high geometric precision mirror. [0003] Alkaline silica polishing technology uses chemical polishing and mechanical polishing, both of which act...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): B24B39/06H01L21/304

Inventor 李翔刘振福李科技武卫张宇

Owner ZHONGHUAN ADVANCED SEMICON MATERIALS CO LTD