FFT accelerator with high throughput rate

A high-throughput, accelerator technology, applied in the field of high-throughput FFT accelerators, can solve the problems of low throughput, low computing efficiency, data throughput, and reduced utilization of computing units, achieving high throughput and saving on-chip The effect of storage resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The solution of the present invention will be described in detail below in conjunction with the accompanying drawings.

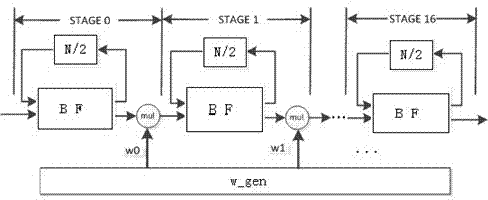

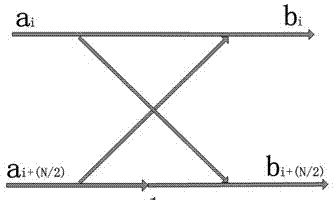

[0033] A Fast Fourier Transformation (FFT) processor with a large number of points is usually implemented based on a Field Programmable Gate Array (Field Programmable Gate Array, FPGA). The high-throughput FFT accelerator provided in this embodiment is based on an FPGA chip, adopts a frequency decimation radix-2 FFT algorithm, and adopts a hardware architecture of one-way delayed feedback. The system test platform of the present embodiment is the necessary design tool ISE of the FPGA based on XILINX.

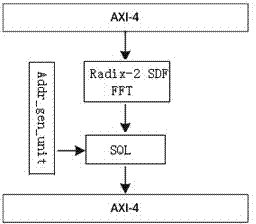

[0034] Such as figure 1 , the high-throughput FFT accelerator provided in this embodiment includes a data storage module, an address generation module, and an FFT acceleration module. The data storage module is used for reading, writing and transmitting data, and this embodiment is a QDR memory. The address generating module provides the target addre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More