Lamination packaging structure of double chips

A stacked packaging, dual-chip technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of limiting the function of finished circuits, waste, etc., to increase the assembly volume of components and improve the function of the package body , Conducive to the effect of product volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0008] The present invention will be described in more detail below in conjunction with the accompanying drawings and embodiments.

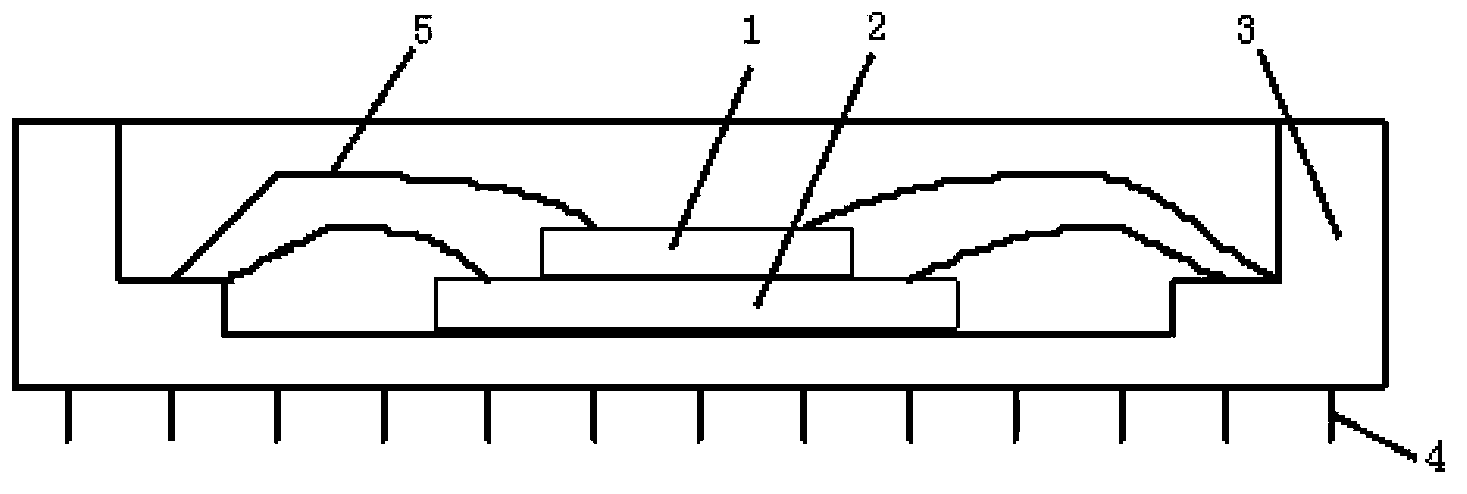

[0009] As shown in the figure, the present invention is a two-chip stacked packaging structure, including a large chip 2 and a small chip 1, and the reverse side of the large chip 2 is pasted on the inner bottom of the ceramic package shell 3 through conductive glue or insulating glue. The reverse side of the small chip 1 is pasted on the front of the large chip 2 by insulating glue, and the lead-out ends of the small chip 1 and the large chip 2 are pressure-welded on the ceramic package shell 3 through gold wire 5 and lead out through the pin 4 .

[0010] There are more chips in the same package. Its functions have been expanded, and this way does not need to develop new chips again, which effectively reduces the development cost and cycle.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More