A low-power scanning self-test circuit and self-test method

A self-testing circuit and self-testing technology, applied in the direction of measuring electricity, measuring electrical variables, electronic circuit testing, etc., can solve problems such as energy loss, and achieve the effect of low energy consumption replanting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The objects and functions of the present invention and methods for achieving the objects and functions will be clarified by referring to the exemplary embodiments. However, the present invention is not limited to the exemplary embodiments disclosed below; it can be implemented in various forms. The essence of the description is only to help those skilled in the relevant art comprehensively understand the specific details of the present invention.

[0036] Hereinafter, embodiments of the present invention will be described with reference to the accompanying drawings. In the drawings, the same reference numerals represent the same or similar components, or the same or similar steps.

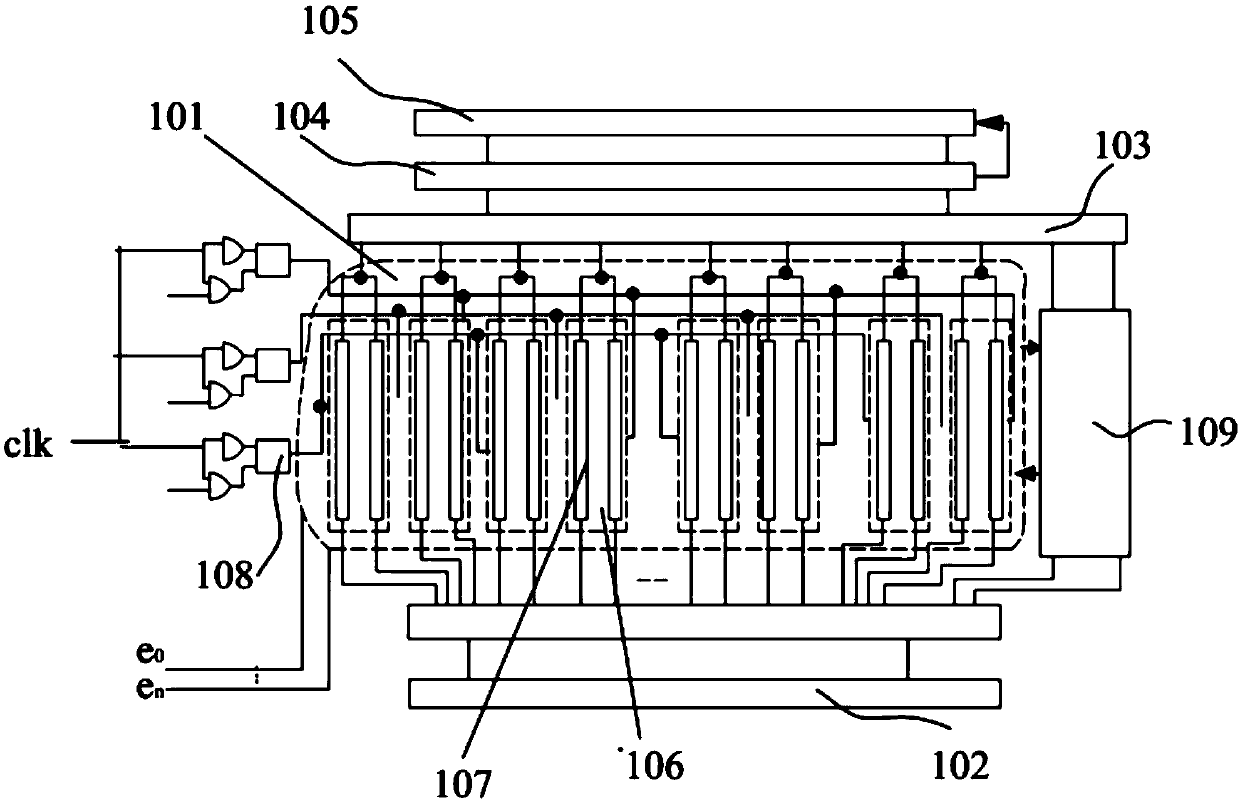

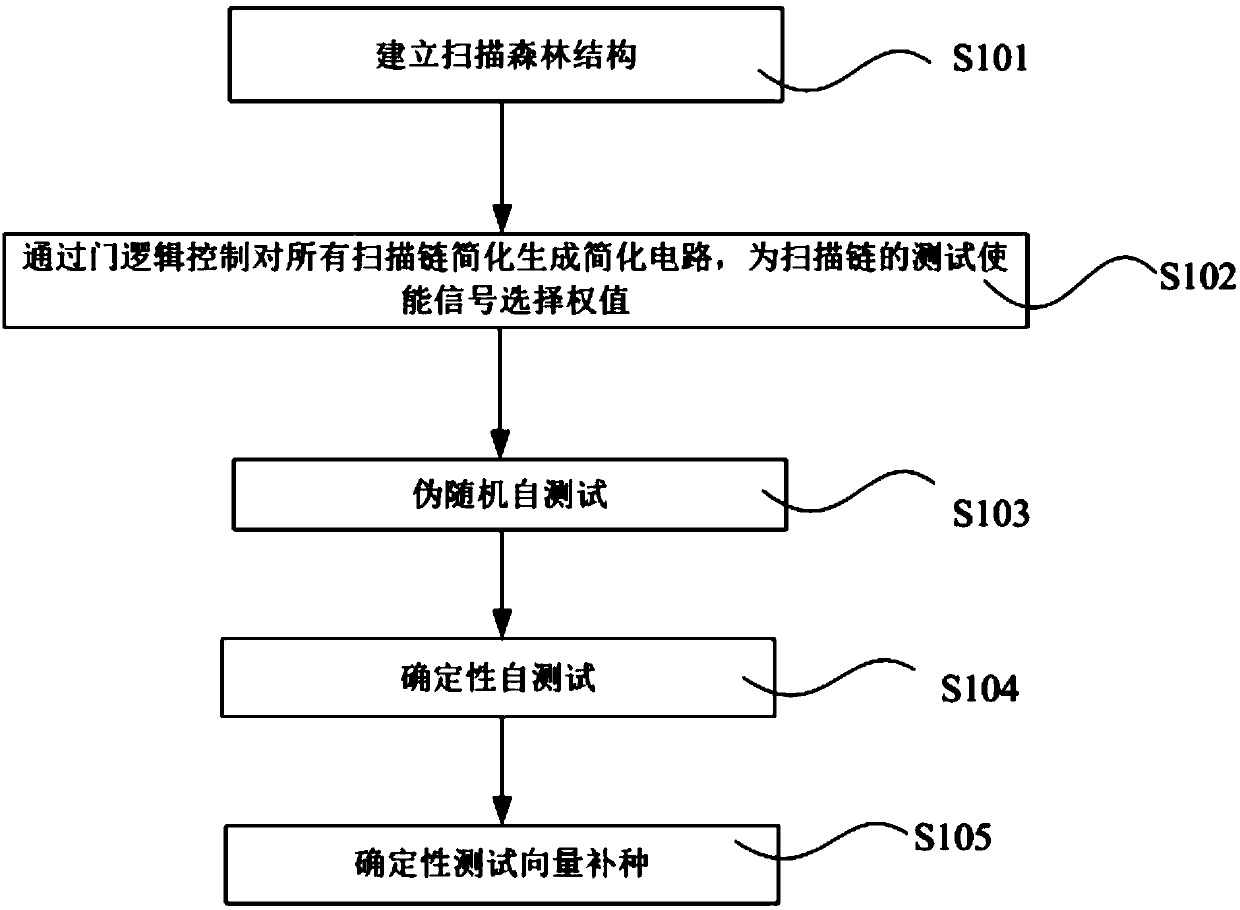

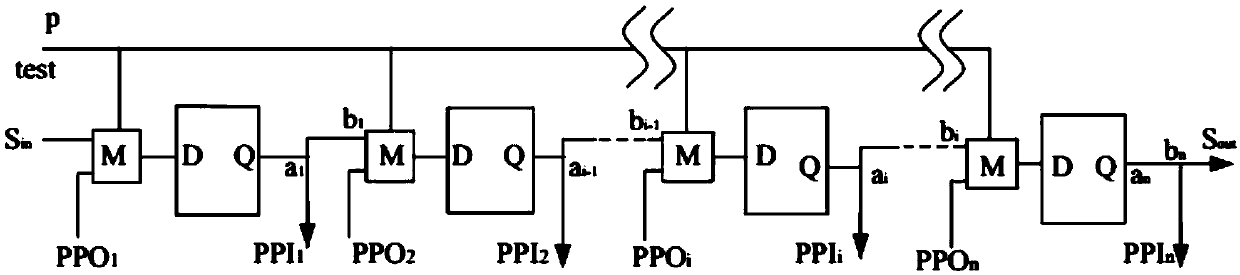

[0037] Through this embodiment, the low-power scanning self-test circuit and the test method provided by the present invention are specifically described. In the low-power scanning self-test circuit in the embodiment, the scan chains under the same scan tree are in the same self-test proces...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More