A kind of multi-layer stacked 3d-sip chip test method

A chip testing, multi-layer stacking technology, applied in electronic circuit testing, electrical measuring, measuring devices, etc., can solve the problem of increased difficulty in the testing stage, and achieve the effect of eliminating the need for a large number of pins and flexible application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

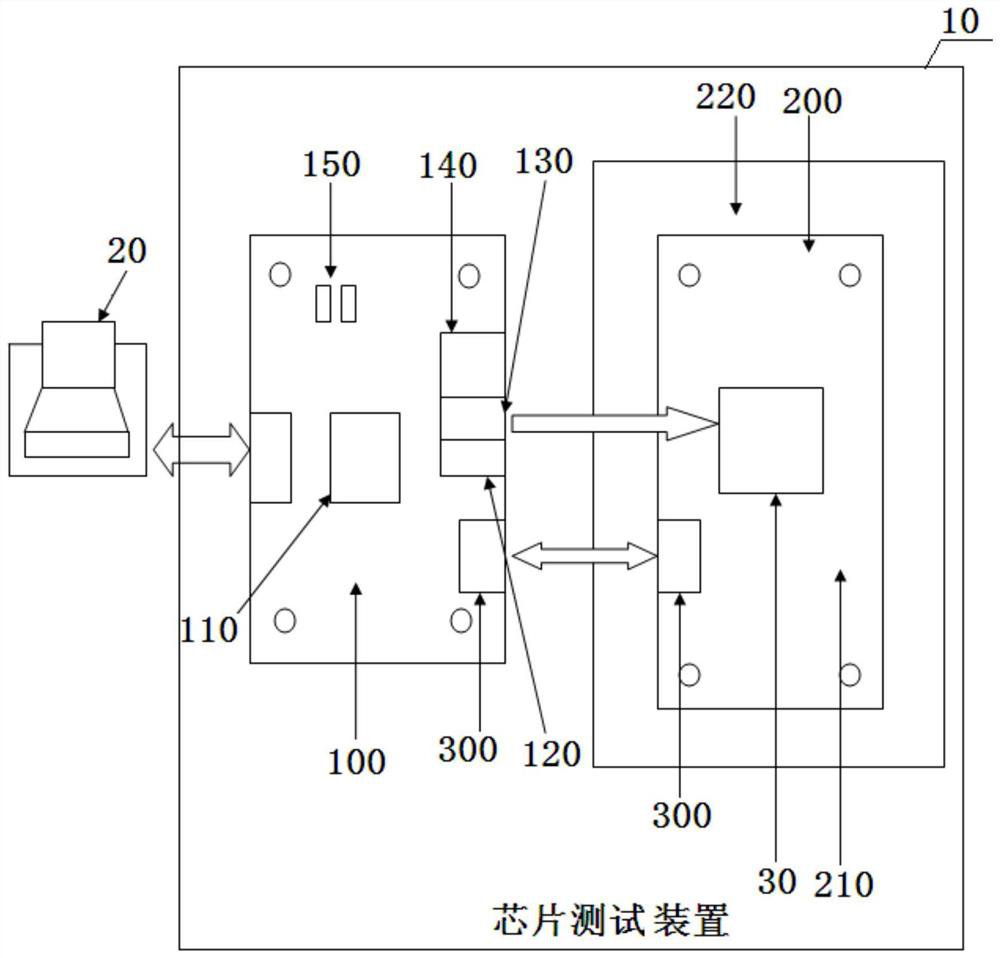

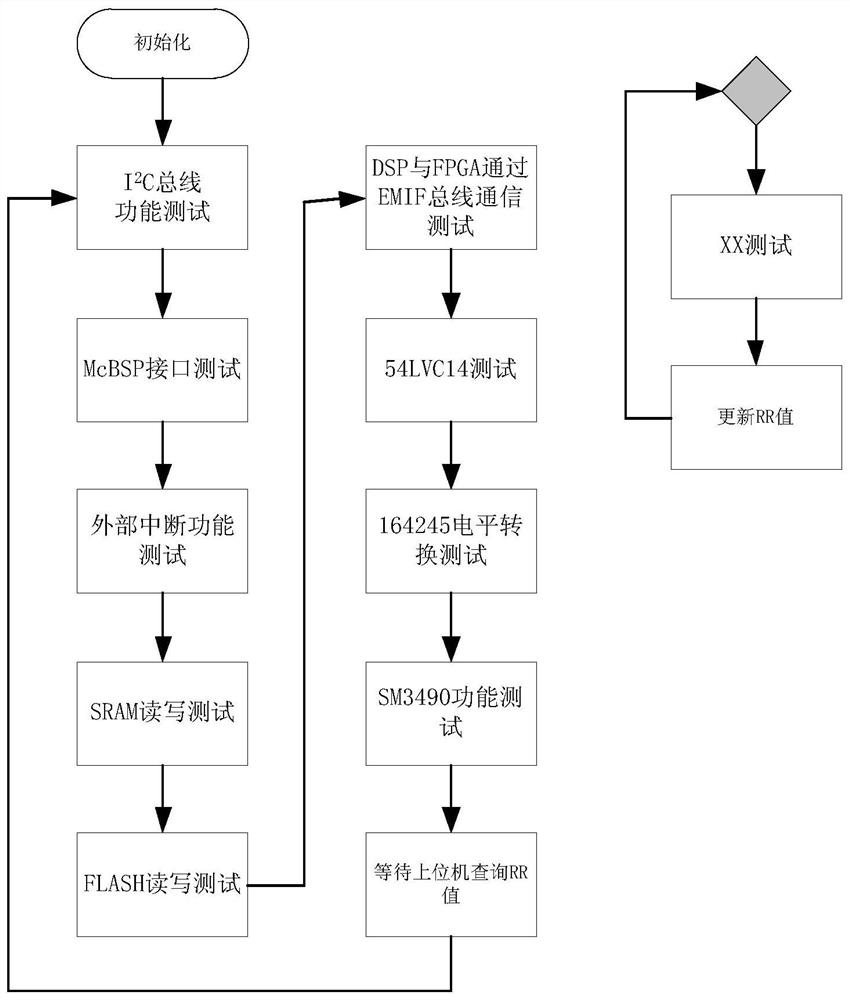

[0025] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

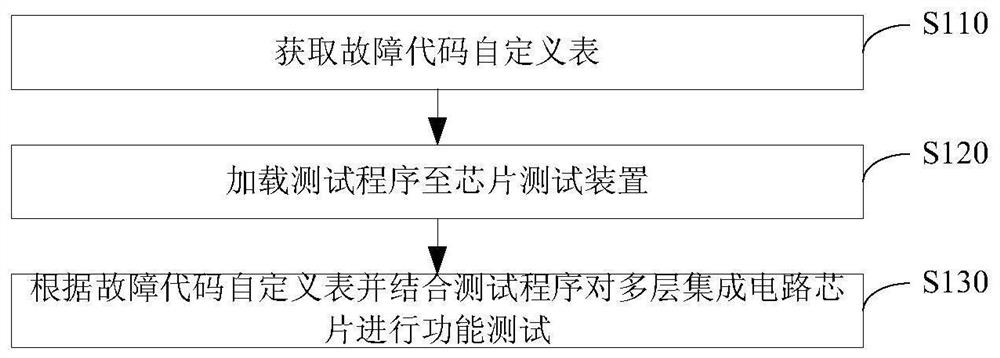

[0026] As an aspect of the present invention, a kind of 3D-SIP chip testing method of multi-layer stacking is provided, wherein, as figure 1 Shown, described 3D-SIP chip test method comprises:

[0027] S110. Acquiring a custom fault code table;

[0028] S120, load the test program to the chip test device;

[0029] S130. Perform a functional test on the multilayer integrated circuit chip according to the fault code custom table and in combination with the test program;

[0030] Wherein, the chip testing device is used for executing a test program and for installing the multi-layer integrated circuit chip.

[0031] The multi-layer stacked 3D-SIP chip testing m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More