Convolutional hardware accelerator based on RS (Reed-Solomon) data stream and method thereof

A technology of hardware accelerator and data flow, which is applied in the direction of reasoning method, electrical digital data processing, digital computer components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The scheme of the present invention will be described in detail below in conjunction with the accompanying drawings,

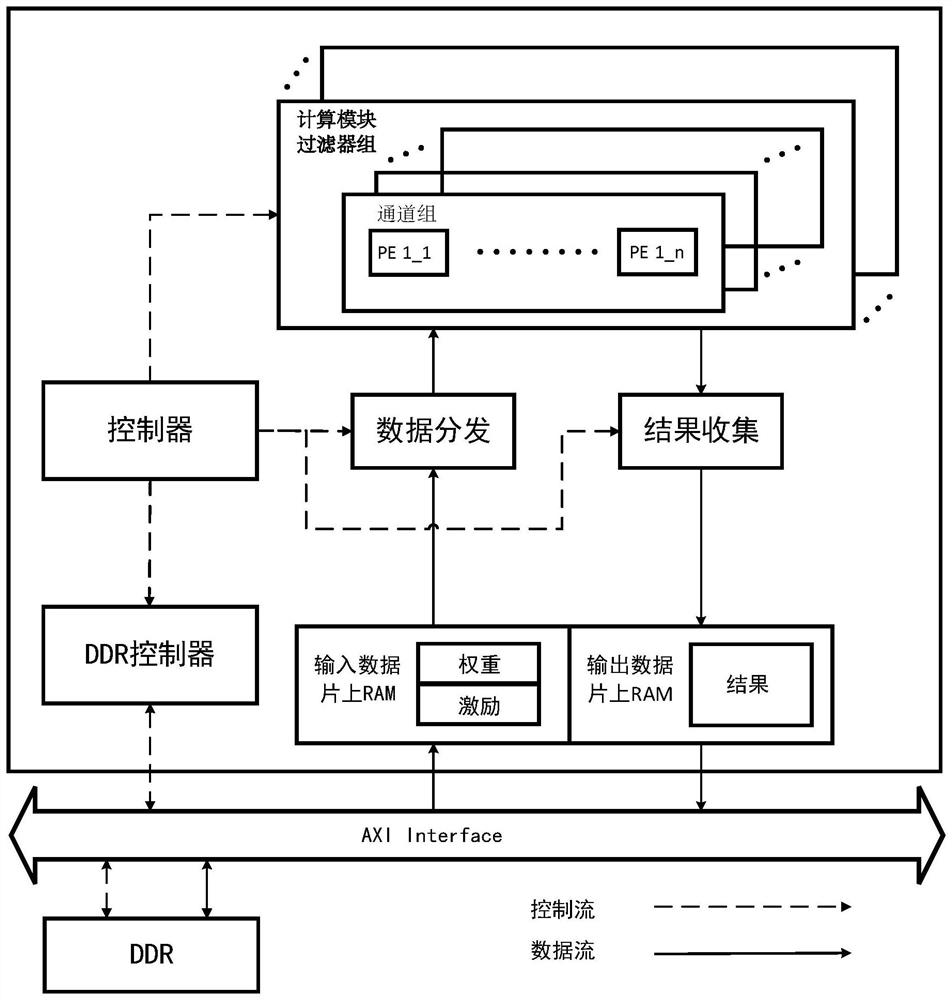

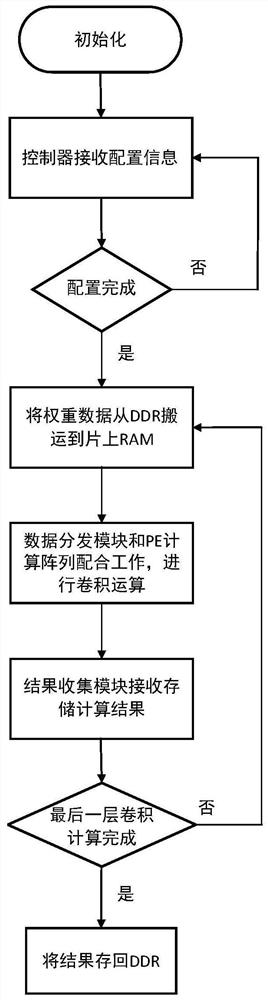

[0035] Such as figure 1The structural block diagram of the convolution hardware accelerator based on RS row fixed data flow is shown, including the controller, DDR controller, on-chip data cache unit (RAM), off-chip DDR memory, data distribution module, photoelectric calculation module and result collection module. Off-chip DDR memory for storing raw image data and neural network inference result data. The on-chip data cache unit is used to store the original image data read from the off-chip DDR memory, convolution kernel weight data and convolution calculation intermediate results. The DDR controller is used to control the data interaction between the off-chip DDR memory and the on-chip data cache unit. The photoelectric computing module is used to complete the convolution operation of each layer of the network, including multiple photoelectric com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More