Method and device for support vector conditional memory access

A support vector and conditional access technology, applied in the direction of machine execution devices, instruments, electrical digital data processing, etc., can solve the problem of reducing the efficiency and flexibility of memory access devices, not directly supporting read and write access operations, storage body organization and addressing Complicated problems, to achieve the effect of reducing the number of constant loading and shuffling, saving data storage space, and improving effective utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

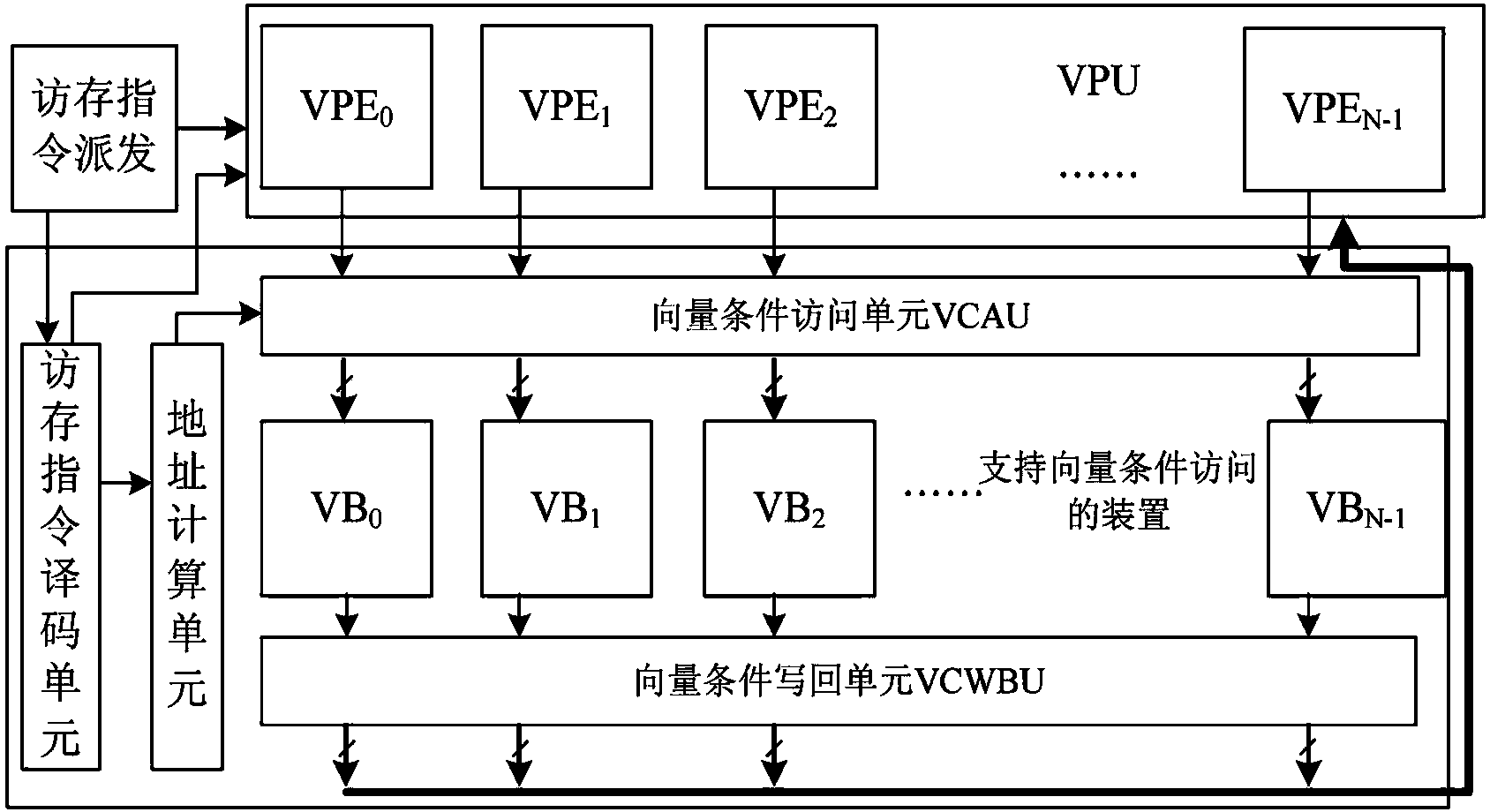

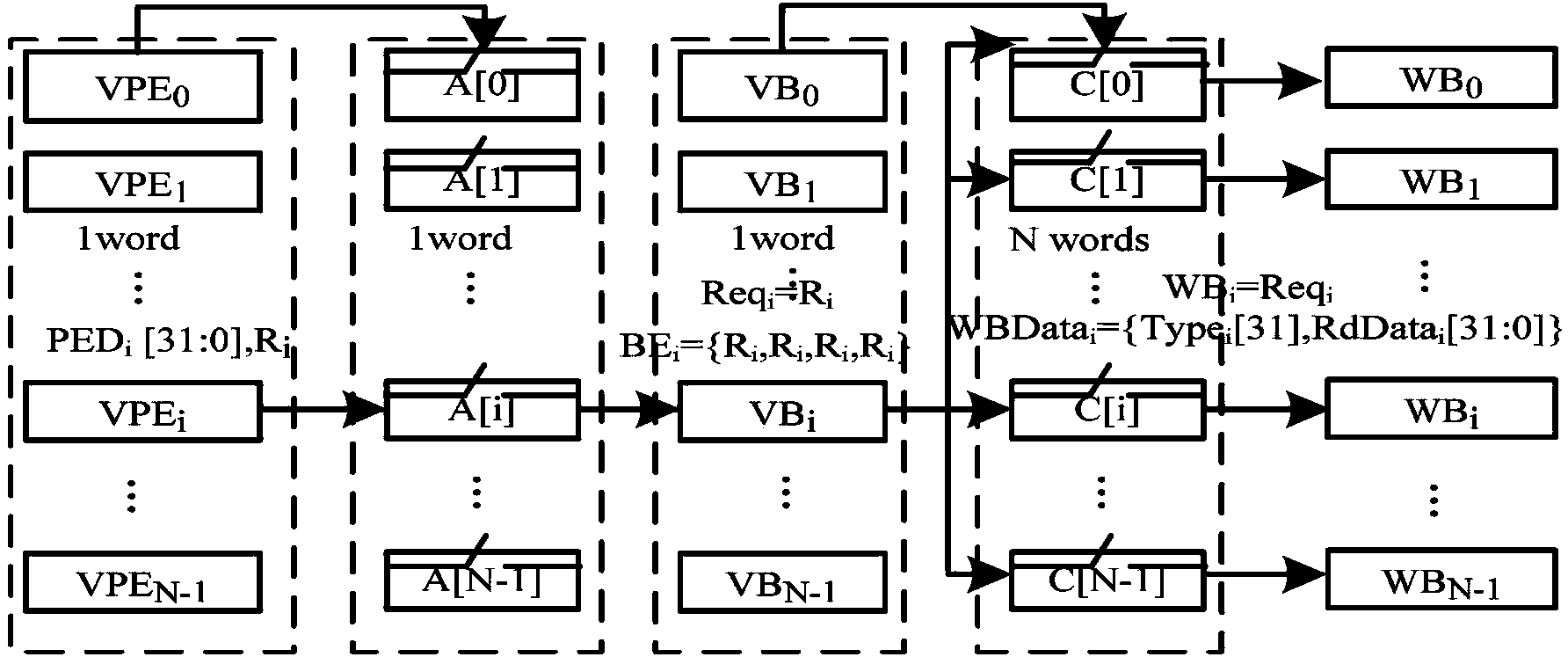

[0028] In a VM using N-way SIMD technology, the invention provides a method and device for supporting vector conditional memory access for vector data access and scalar data access of a VM composed of N-way W-bit-width VBs.

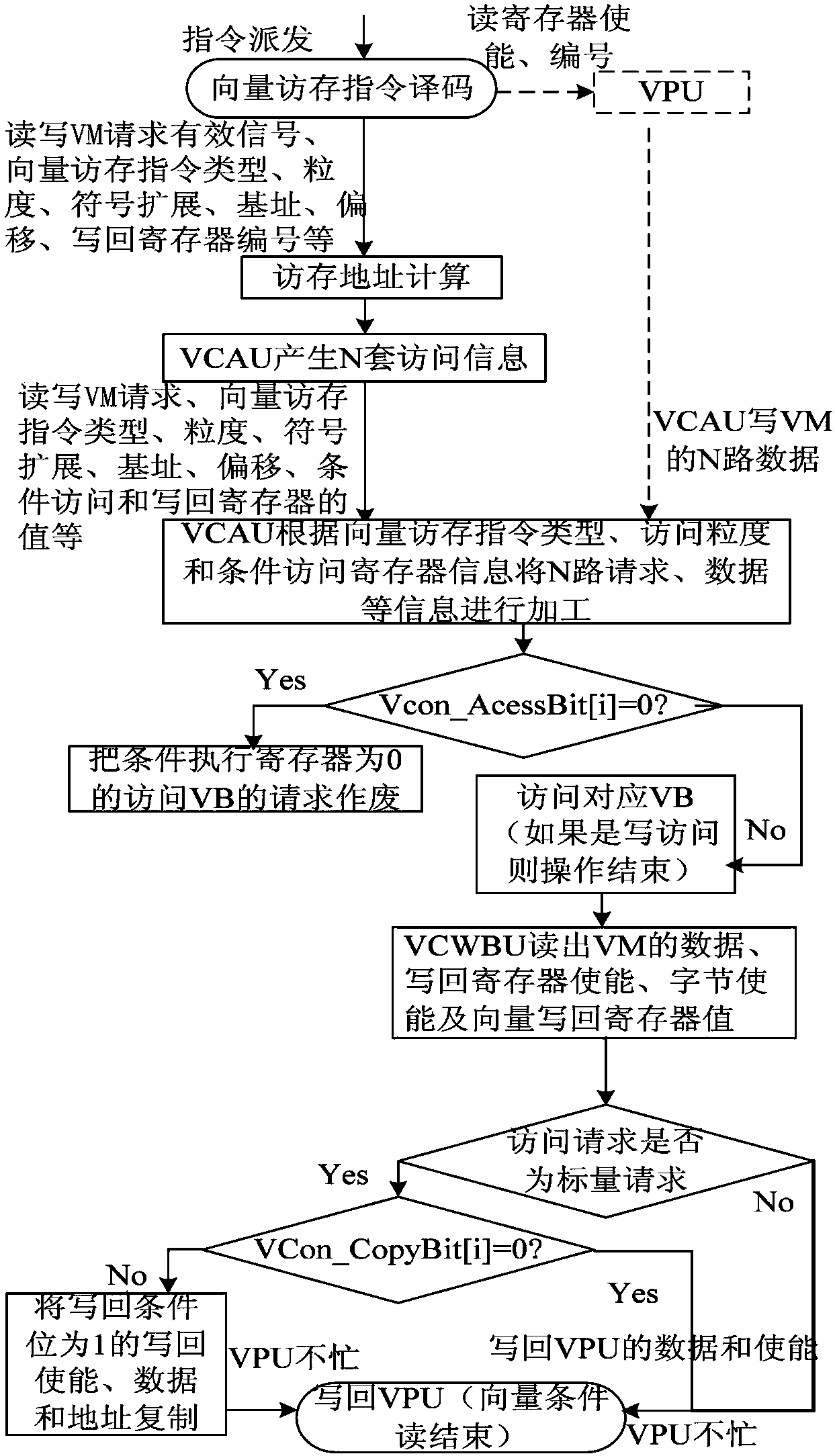

[0029] like figure 1 As shown, a method for conditional memory access of support vectors, the steps are:

[0030] (1) Set a programmable N-bit VPE conditional access register VCon_AcessBit[N-1:0] and N-bit VB conditional write-back register VCon_CopyBit [N-1:0] in the vector conditional access unit VCAU; corresponding to N The memory access condition execution bit of a VPE, when it is 1, it means execution, and when it is 0, it means no execution; among them, VCon_AcessBit[N-1:0] controls whether the corresponding VB executes the memory access operation, and VCon_CopyBit[N-1:0] is only in Control whether the co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More