On-line traffic bottleneck predictive control method based on field programmable gate array (FPGA) and improved dispersed macroscopic D model

A technology of predictive control and macro traffic flow, applied in the field of FPGA control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

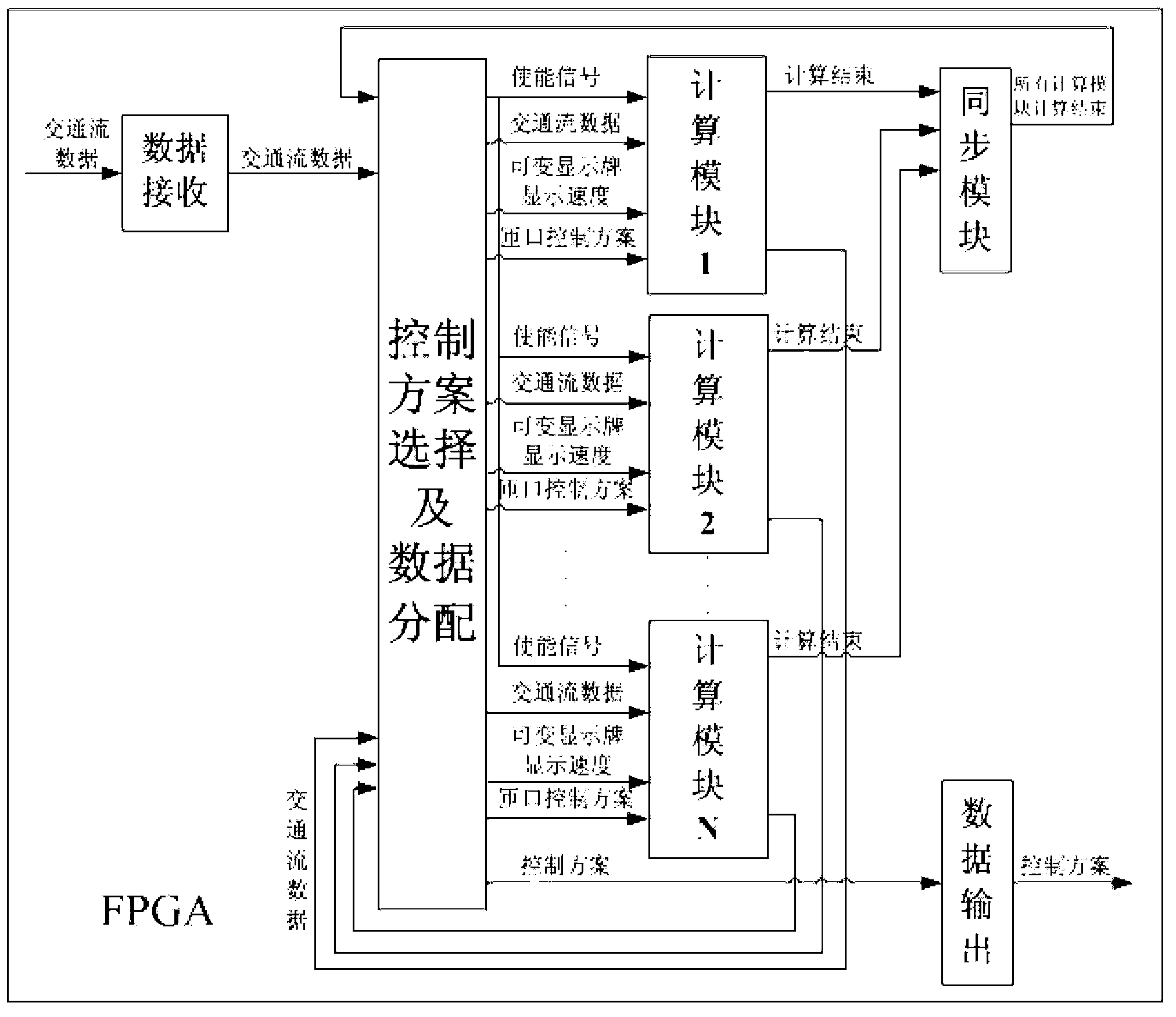

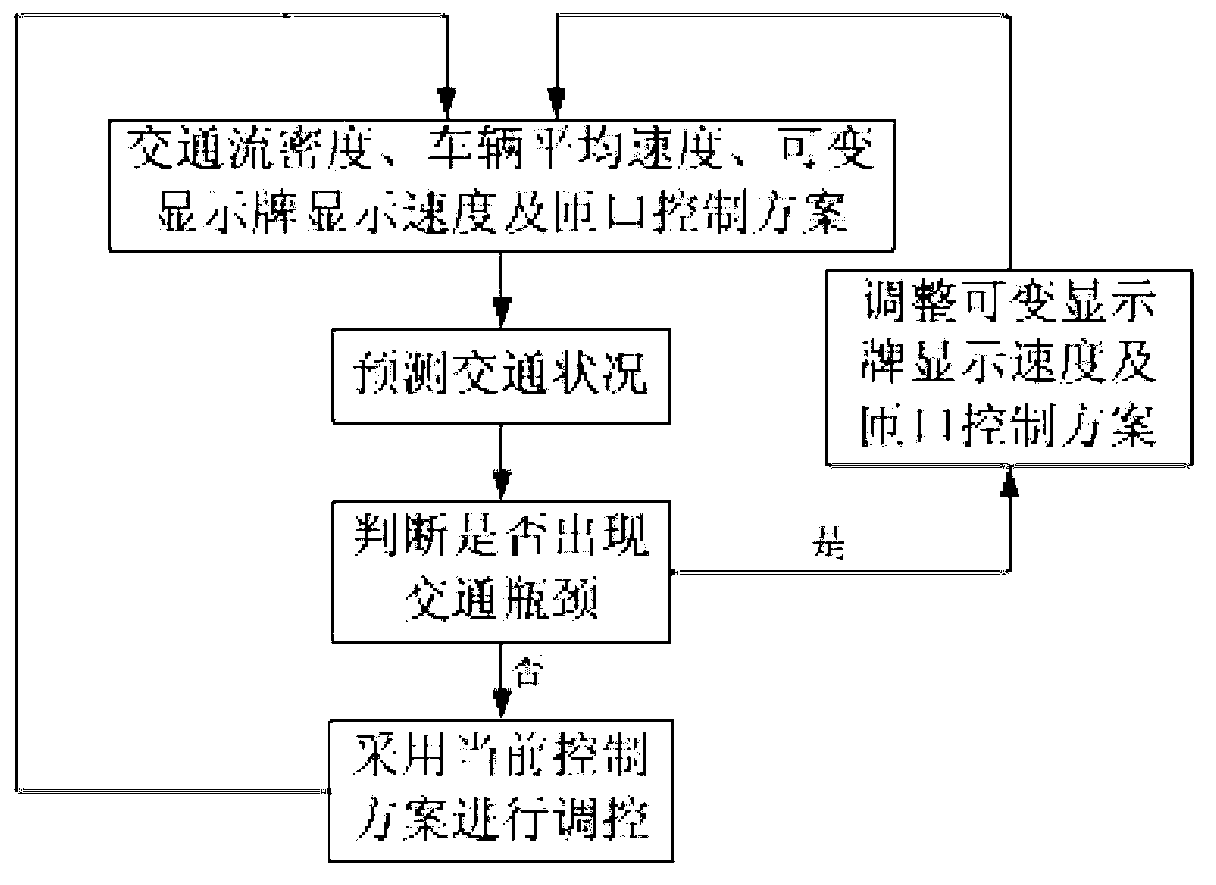

[0046] Refer to attached figure 1 , 2 Describe the present invention in detail.

[0047] The flow chart of the control method of the present invention is attached figure 2 As shown, in the case of no traffic bottleneck, the control scheme is that the variable display board displays the allowable free flow speed of the road, and the turn control does not limit the input and output. The speed and turn control scheme predicts the traffic flow density and the average vehicle speed of each road section for a period of time T c (T c take T 0 , T 1 If there is no traffic bottleneck, use the current control scheme for regulation. If there is a bottleneck, adjust the display speed of the variable display board and the turn control scheme according to the aforementioned priority principle. and continue to predict for some time T c , if the traffic bottleneck cannot be removed, continue to adjust the control scheme until a control scheme is found that can solve the traffic bottlen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More