Data layout method and device thereof

A data layout and data block technology, applied in the direction of electrical digital data processing, instruments, memory systems, etc., can solve the problems of a large number of memory accesses, program performance degradation, etc., and achieve the effect of improving program execution speed and reducing main memory access overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

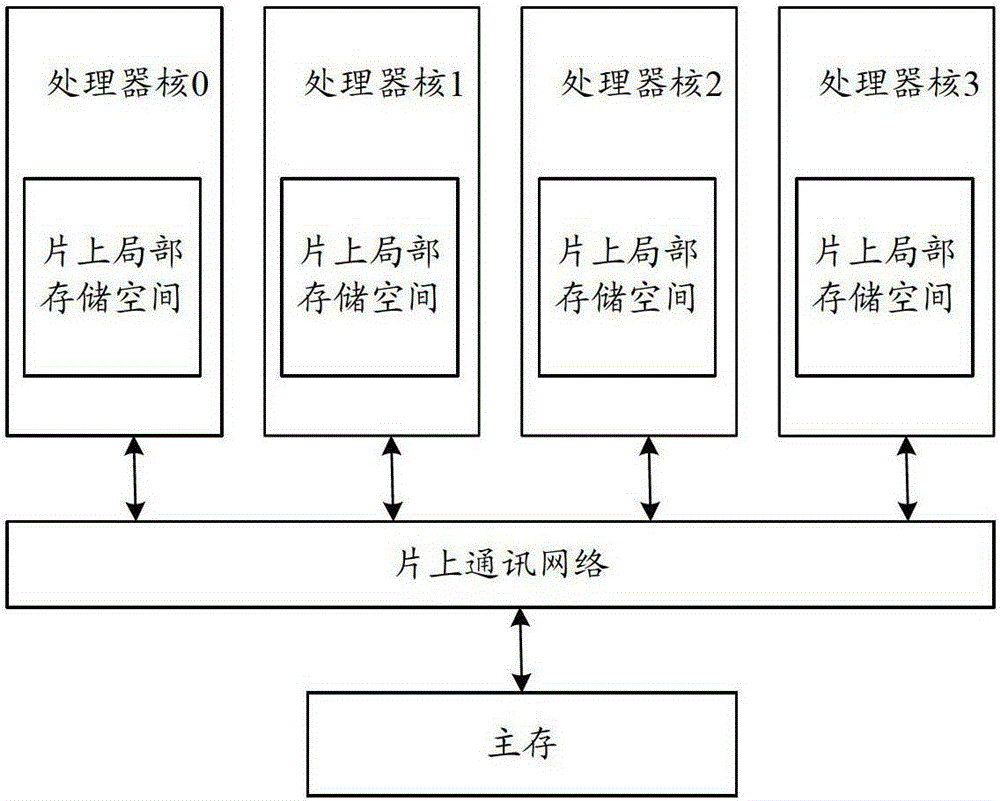

[0028] In the existing technology, such as figure 1 As shown, each slave processor core of the heterogeneous many-core has its own on-chip local storage space, and all slave processor cores obtain boundary data from the main memory through an on-chip communication network (on-chip network). After research, the inventors found that under the shared storage model, too large boundary data will lead to heavy main memory access overhead, thereby greatly affecting the program execution speed of the entire processor. If the distributed storage model is adopted, by determining the The boundary data and privatization of the boundary data to each processor core can reduce the main memory access overhead caused by boundary communication, thereby increasing the program execution speed of the entire processor.

[0029] In view of the above problems, an embodiment of the present invention provides a data layout method. figure 2 It is a flowchart of a data layout method in an embodiment of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More