A write-copy circuit suitable for SRAM

A static random, write copy technology, applied in static memory, digital memory information, information storage, etc., can solve the problem of not being able to achieve the best system performance, and achieve the effect of reducing the pulse width of the word line

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

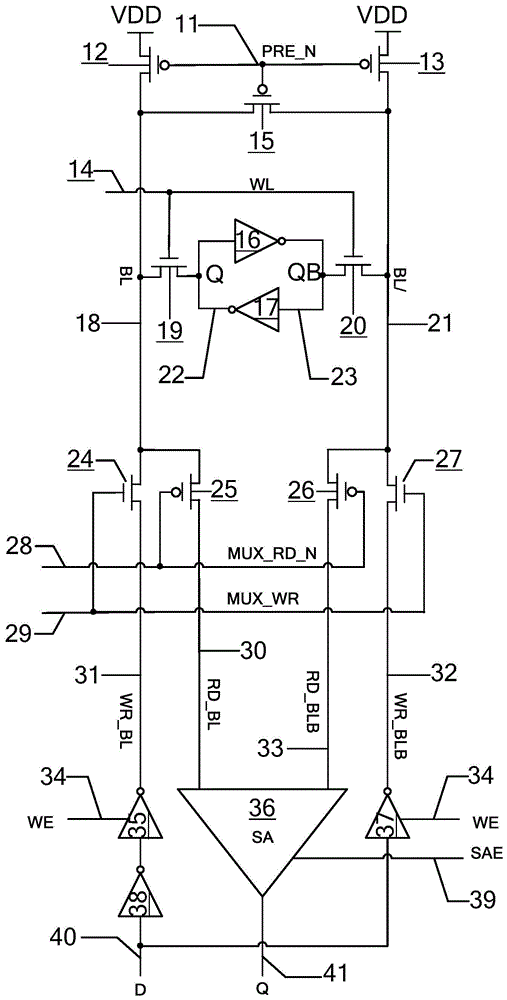

[0029] see figure 1 as shown, figure 1 It is a typical data path instance of SRAM. The typical data path includes precharge circuits, memory cells, bit line selectors, sense amplifiers and write drivers.

[0030] The precharge circuit is composed of PMOS transistors 12,13,15. The storage unit is composed of a pair of cross-coupled inverters 16, 17 and NMOS transmission transistors 19, 20 respectively connected to storage nodes 22, 23. The bit line selector is composed of a pair of NMOS transistors 24,27 and a pair of PMOS transistors 25,26. Sensitive amplifiers such as figure 1 Sensitive amplifier 36 in the middle. The write driver consists of an inverter 38 and a pair of tri-state inverters 35,37.

[0031] In the holding mode of the static memory, the word line 14 of the memory cell is inactive (active high), and the bit line 18 and the bit line ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More