A Static Random Access Memory and Its Bit Line Precharge Self-timing Circuit

A static random and memory technology, applied in the direction of static memory, digital memory information, information storage, etc., can solve the problems of static memory read and write access time and the minimum clock cycle impact, and achieve the effect of good resistance and good process voltage temperature deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

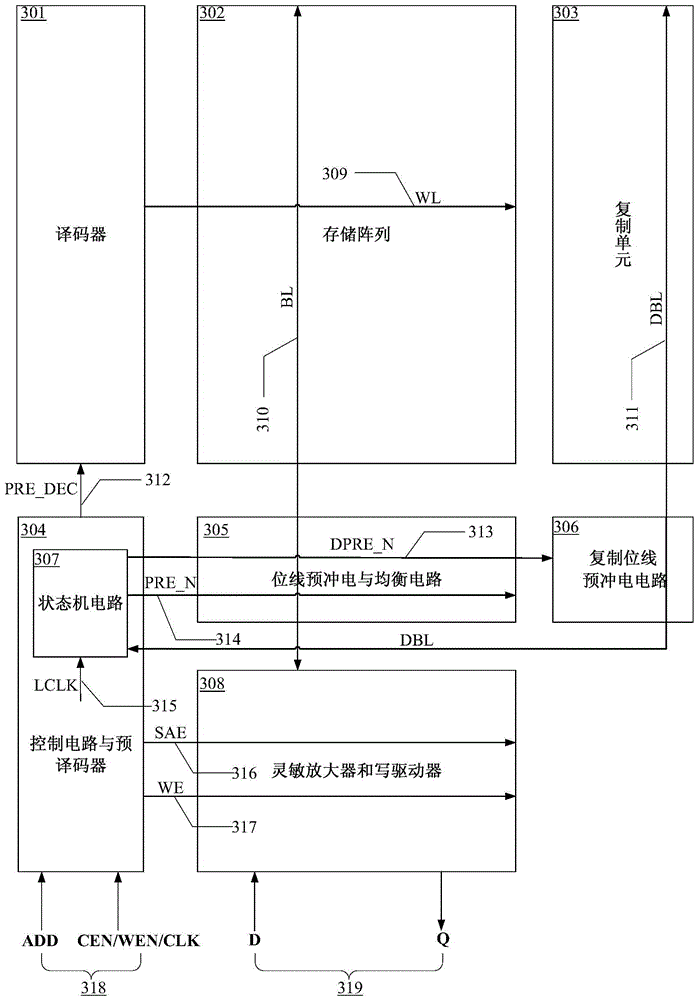

[0041] Embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

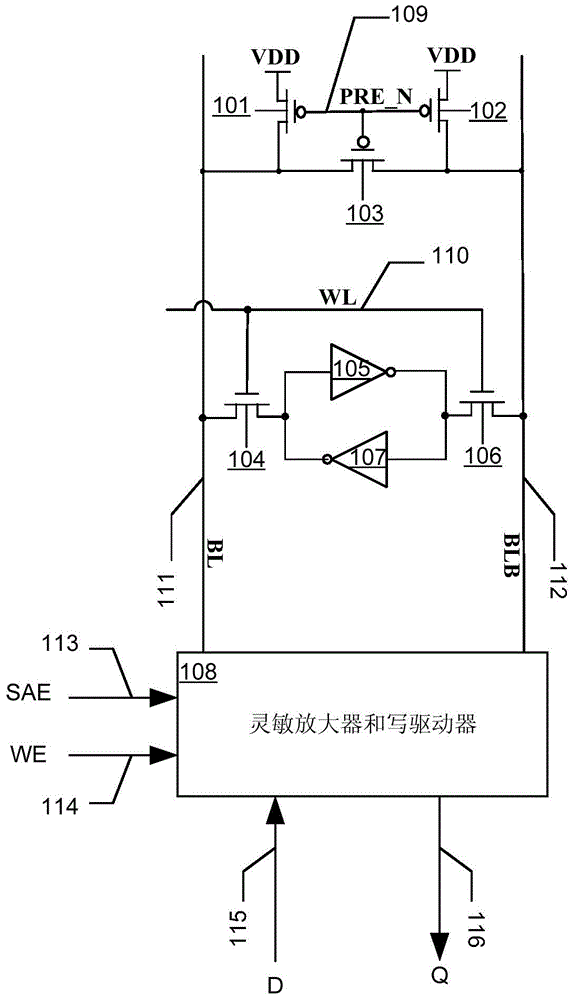

[0042] like image 3 as shown, image 3 It is an example of a SRAM implemented according to the present invention. The SRAM includes a decoder 301, a memory array 302, a copy unit 303, a control circuit and a pre-decoder 304, a bit line precharge and equalization circuit 305, a copy bit line precharge circuit 306, a state machine circuit 307 and a sensitive amplifier and write driver 308 .

[0043] The decoder 301 is connected to the memory array 302 through a plurality of word lines (WL) 309 , and the decoder 301 is also connected to the control circuit and the pre-decoder 304 through a plurality of pre-decoder outputs (PRE_DEC) 312 .

[0044] The memory array 302 is also connected to a bit line precharge and equalization circuit 305 and a sense amplifier and write driver 308 through a plurality of bit lines (BL) 310 .

[0045] The duplicate unit 30...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More