Layout design method, layout design system and manufacture method of integrated circuit

A technology of integrated circuit and layout design, applied in computing, electrical digital data processing, instruments, etc., can solve the problems of low yield rate of integrated circuits, well proximity effect and shallow trench isolation stress effect, etc., to improve and lengthen the design cycle Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

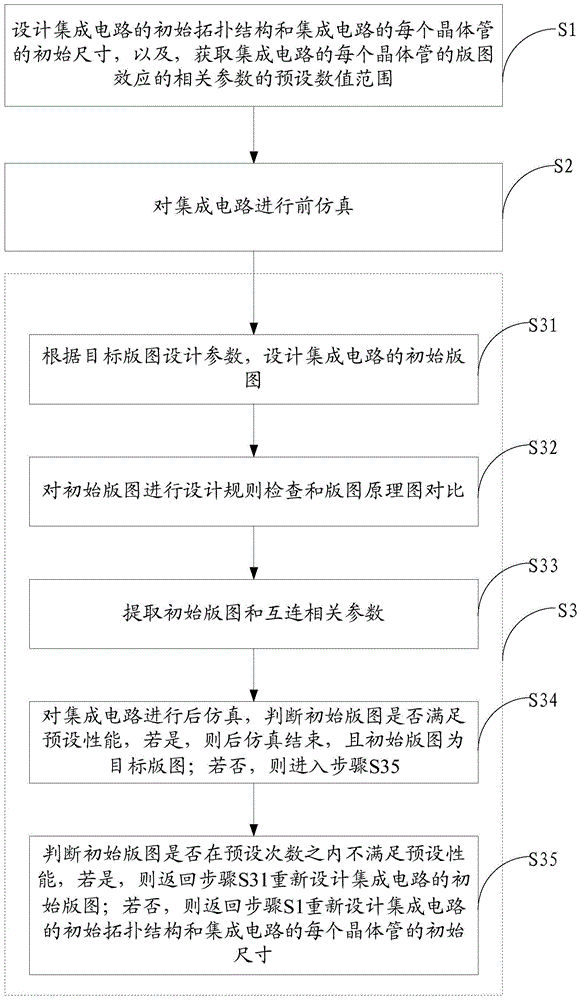

[0038] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0039] As mentioned in the background technology, due to the further shrinkage of the transistor size, the characteristics of the transistor itself are more significantly affected by the layout dependent effect, such as the effect of the well proximity effect and the shallow trench isolation stress effect, which in turn leads to integration The production yield of the circuit is low.

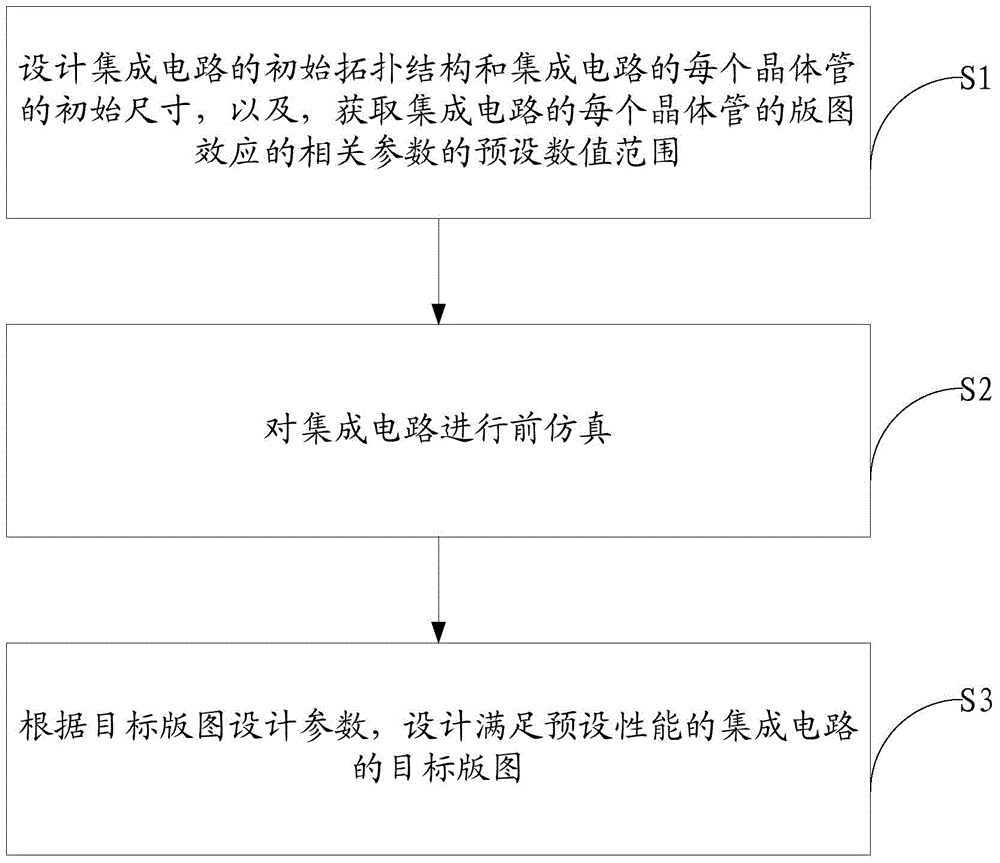

[0040] Based on this, the embodiment of the present application provides a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More