A bus virtualization method, device and system

A virtualization and bus technology, applied in the computer field, which can solve the problems of confusion of address registers and data registers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

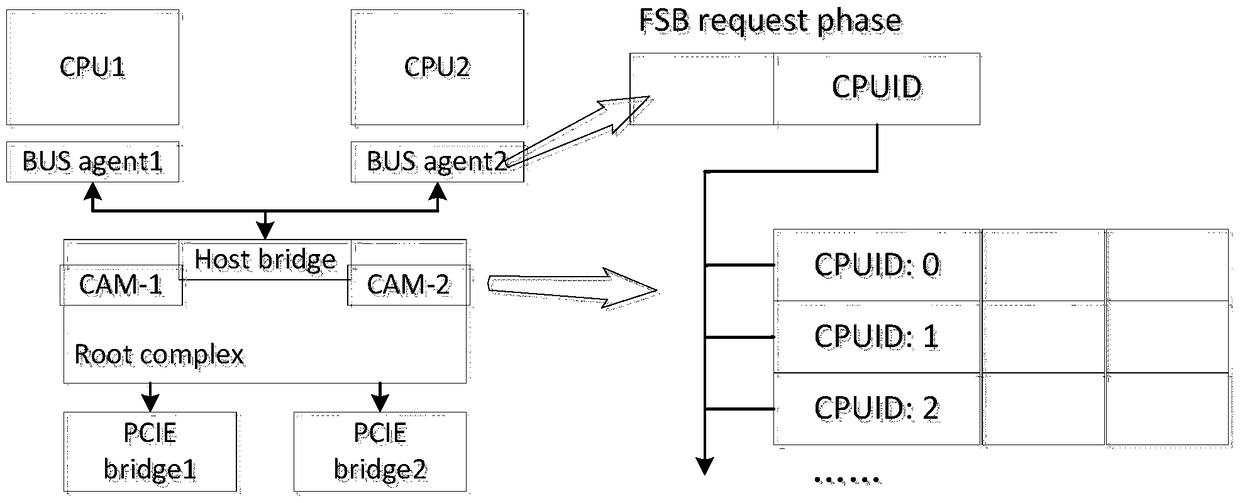

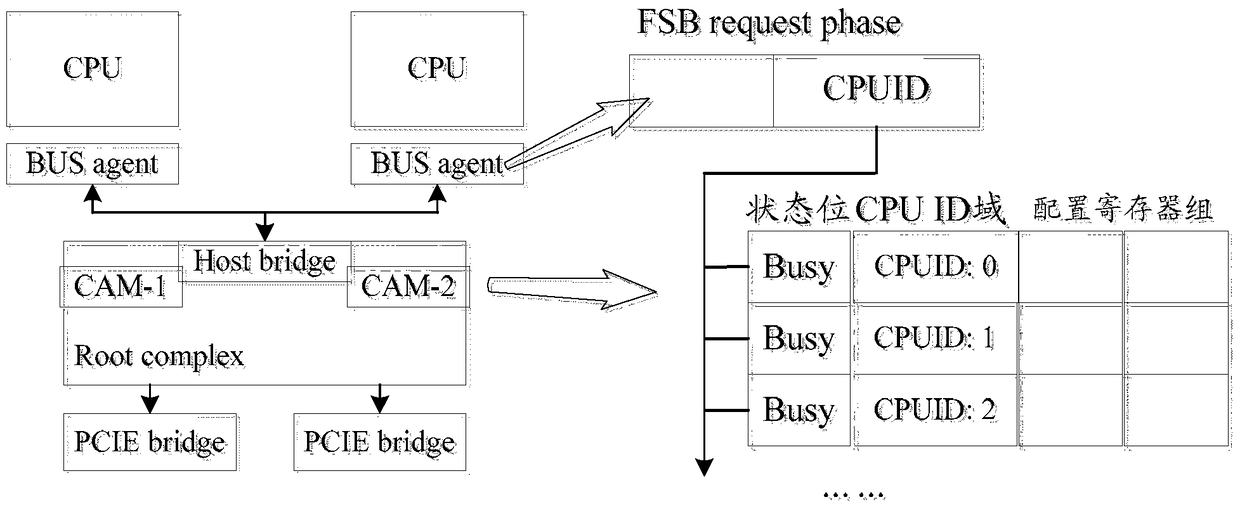

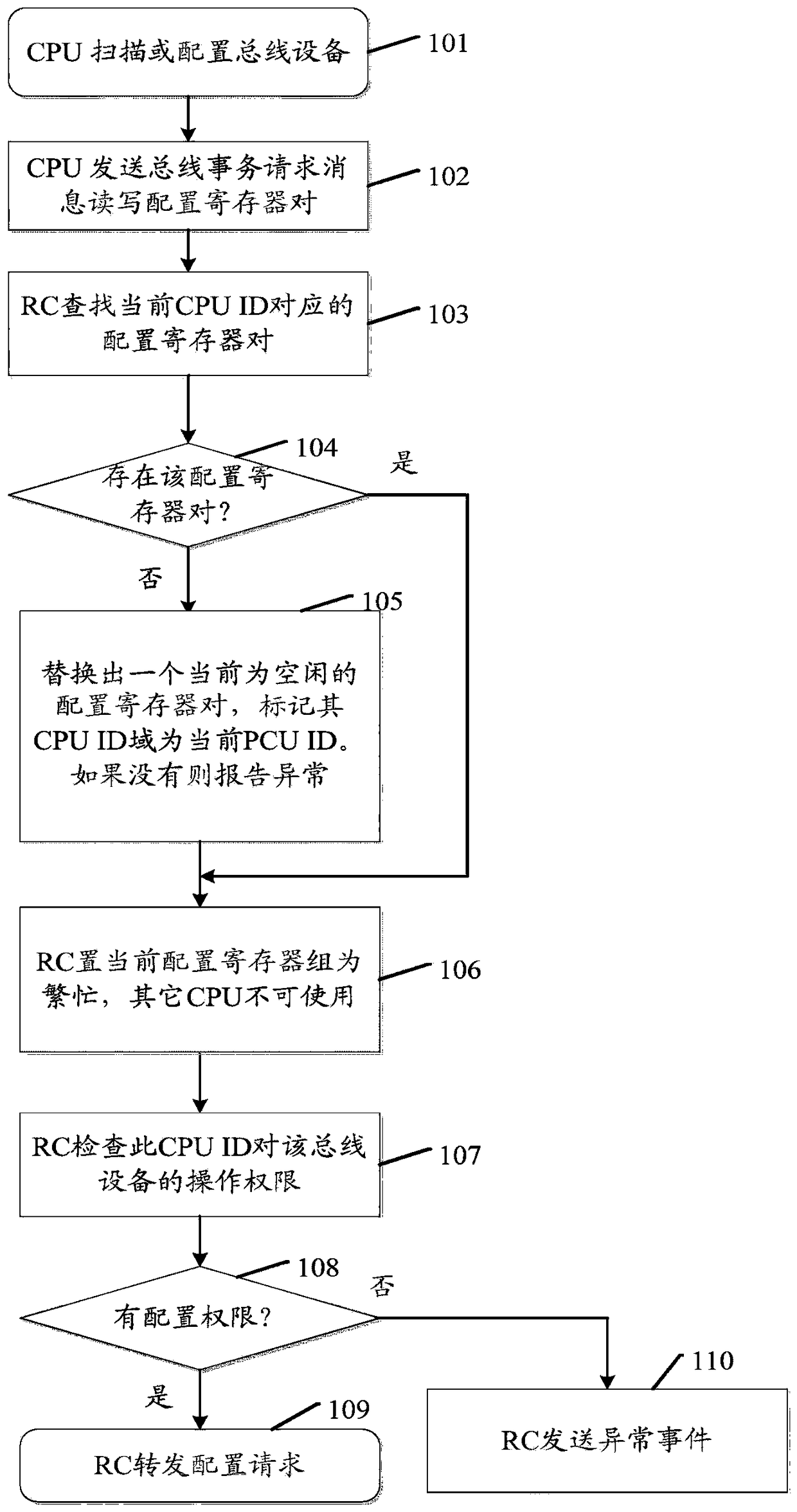

[0050] The embodiment of the present invention provides a method for bus virtualization, which can ensure that each processor core can use an independent pair of configuration registers when accessing a bus device, thereby ensuring correctness of the processor core's access to the bus device. Embodiments of the present invention also provide corresponding devices and systems. Each will be described in detail below.

[0051] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by those skilled in the art without creative efforts fall within the protection scope of the present invention.

[0052] An embodiment of the bus virtualization method provi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More