Fault testing method for interconnection resource of programmable logic device

A technology for interconnecting resources and programming logic, applied in the field of automatic fault traversal testing of interconnection resources of general-purpose programmable logic devices, and can solve the problem of high computational complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

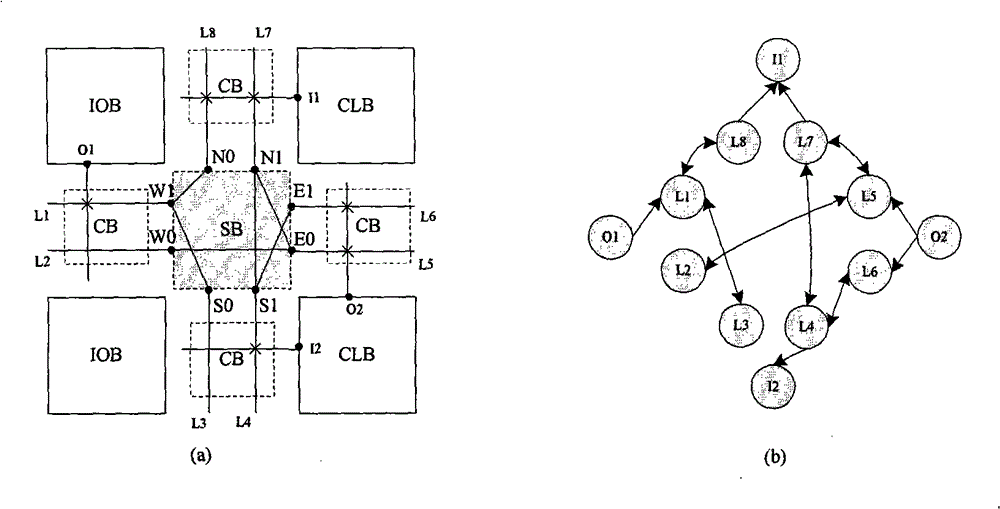

[0047] Take the FPGA structure model with a 3*3 array scale as an example, the model scale is 3*3, which means that there are 3 CLBs in the horizontal and vertical directions. There are 2 double lines and one long line in the channel, and the generated number of PIPs to be tested is 176. The specific structure of the FPGA chip is described as follows:

[0048]

subblock_lut_size="4"

switch_block_type="wilton" chan_width_uniform="1"

chip_chan_width="3, 3"

segment_x="3 2" segment_y="3 2" / >

[0049]

[0050] According to the structure description file, the corresponding wiring resource diagram is generated to generate the test r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More