Fast arithmetic multi-bit serial pulse dual-base binary finite field multiplier

A dual-substrate, multi-bit technology, which can be used in calculations using the number system, calculations using non-contact manufacturing equipment, etc., and can solve problems such as high latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The technical solution of the present invention will be further described below in conjunction with specific embodiments.

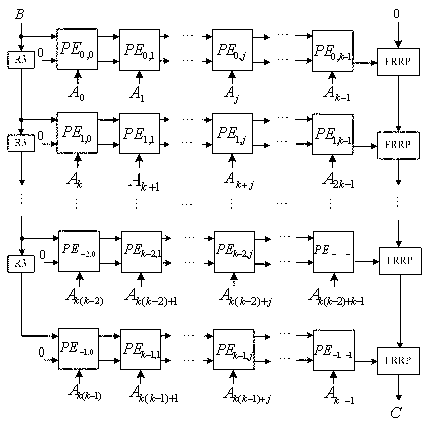

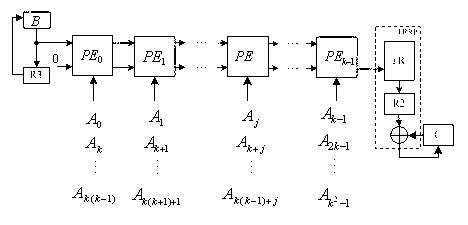

[0018] Such as figure 2 As shown, the specific implementation of the present invention is to construct a fast arithmetic multi-bit series pulsating dual-base binary finite field multiplier, including input B, k PE modules, FRRP modules, and R3 modules, the k PEs The modules are connected in series, and the k PE modules have passed k cycles, and the input of the first cycle A is A 0 , A 1 ,..., A k-1 , B is directly input, and the calculation result is restored and input into the register C through the FRRP module; the input A of the second cycle A k , A k+1 ,..., A 2k-1 , B is input by the R3 module, and the calculation result is also restored by the FRRP module, added to the calculation result of the first cycle, and stored in the register C; thus, the kth cycle, the input of A is B is input after (k-1) the R3 module, the calculation result is restor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More